Similar presentations:

Практика 3 (1)

1. Цифровая электроника

Практичеcкая работа 303.10.2025г

2. Устройства комбинационной логики

Аппаратная реализация булевыхфункций

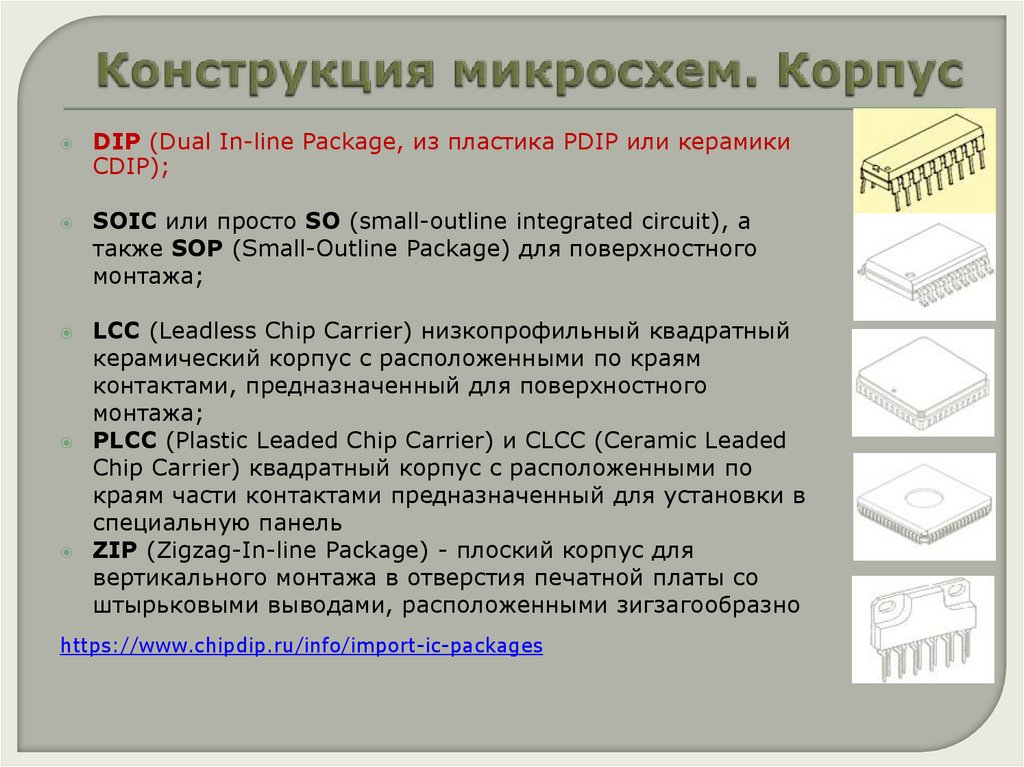

3. Конструкция микросхем. Корпус

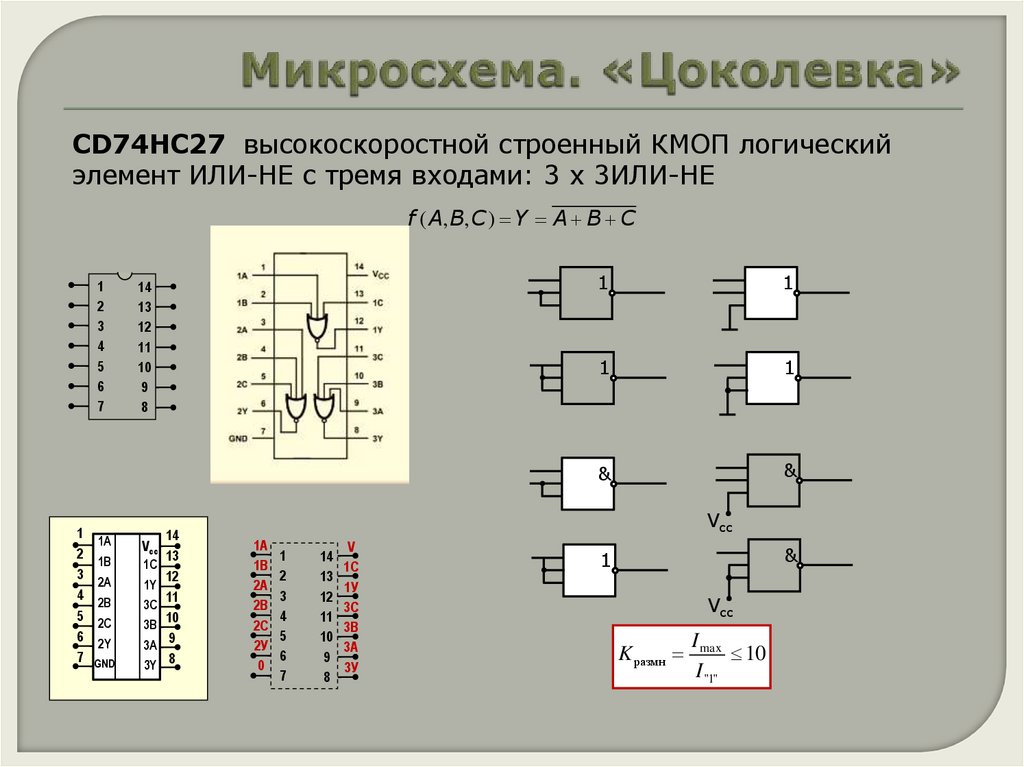

DIP (Dual In-line Package, из пластика PDIP или керамикиCDIP);

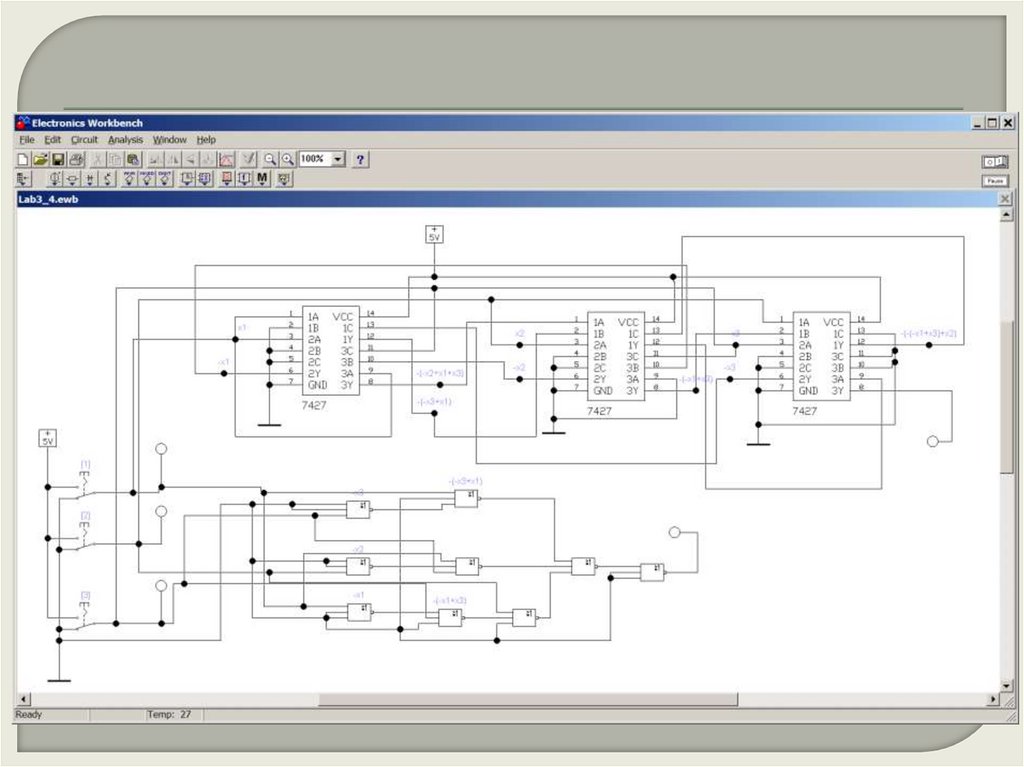

SOIC или просто SO (small-outline integrated circuit), а

также SOP (Small-Outline Package) для поверхностного

монтажа;

LCC (Leadless Chip Carrier) низкопрофильный квадратный

керамический корпус с расположенными по краям

контактами, предназначенный для поверхностного

монтажа;

PLCC (Plastic Leaded Chip Carrier) и СLCC (Ceramic Leaded

Chip Carrier) квадратный корпус с расположенными по

краям части контактами предназначенный для установки в

специальную панель

ZIP (Zigzag-In-line Package) - плоский корпус для

вертикального монтажа в отверстия печатной платы со

штырьковыми выводами, расположенными зигзагообразно

https://www.chipdip.ru/info/import-ic-packages

4.

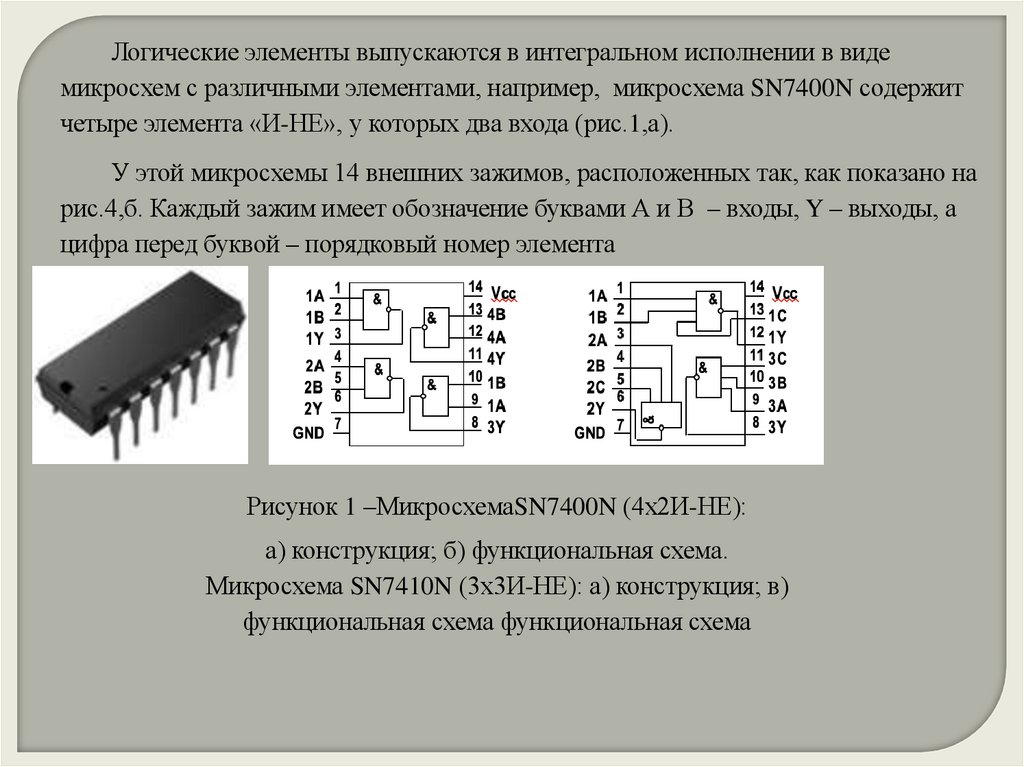

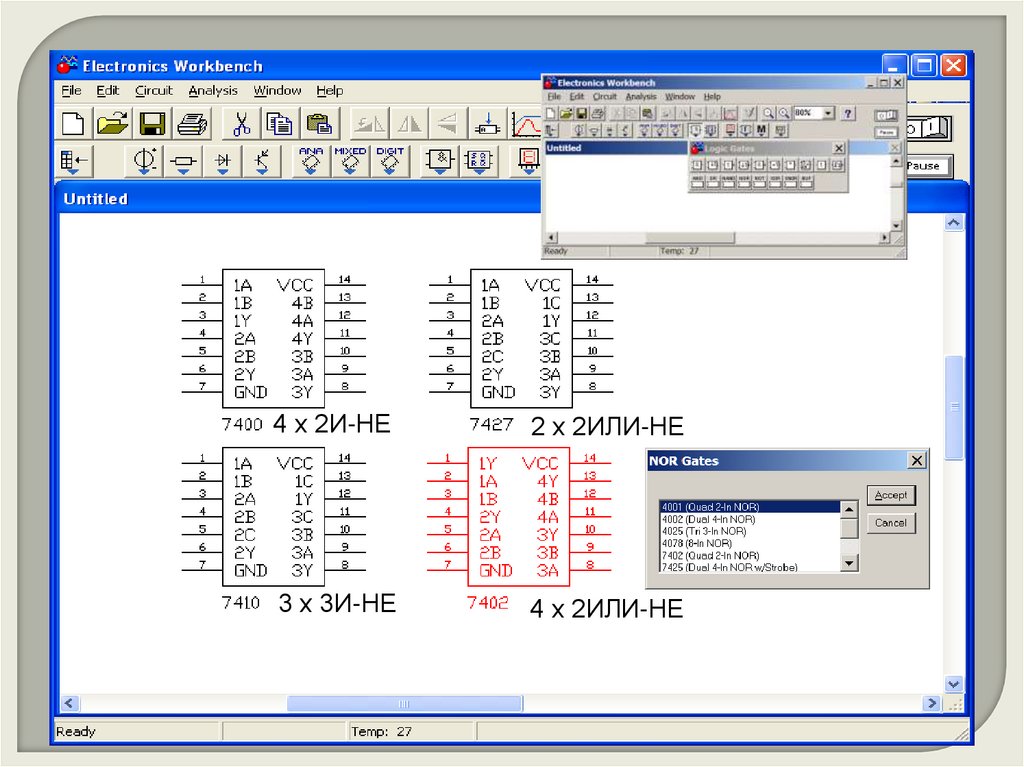

Логические элементы выпускаются в интегральном исполнении в видемикросхем с различными элементами, например, микросхема SN7400N содержит

четыре элемента «И-НЕ», у которых два входа (рис.1,а).

У этой микросхемы 14 внешних зажимов, расположенных так, как показано на

рис.4,б. Каждый зажим имеет обозначение буквами А и В – входы, Y – выходы, а

цифра перед буквой – порядковый номер элемента

Рисунок 1 –МикросхемаSN7400N (4х2И-НЕ):

а) конструкция; б) функциональная схема.

Микросхема SN7410N (3х3И-НЕ): а) конструкция; в)

функциональная схема функциональная схема

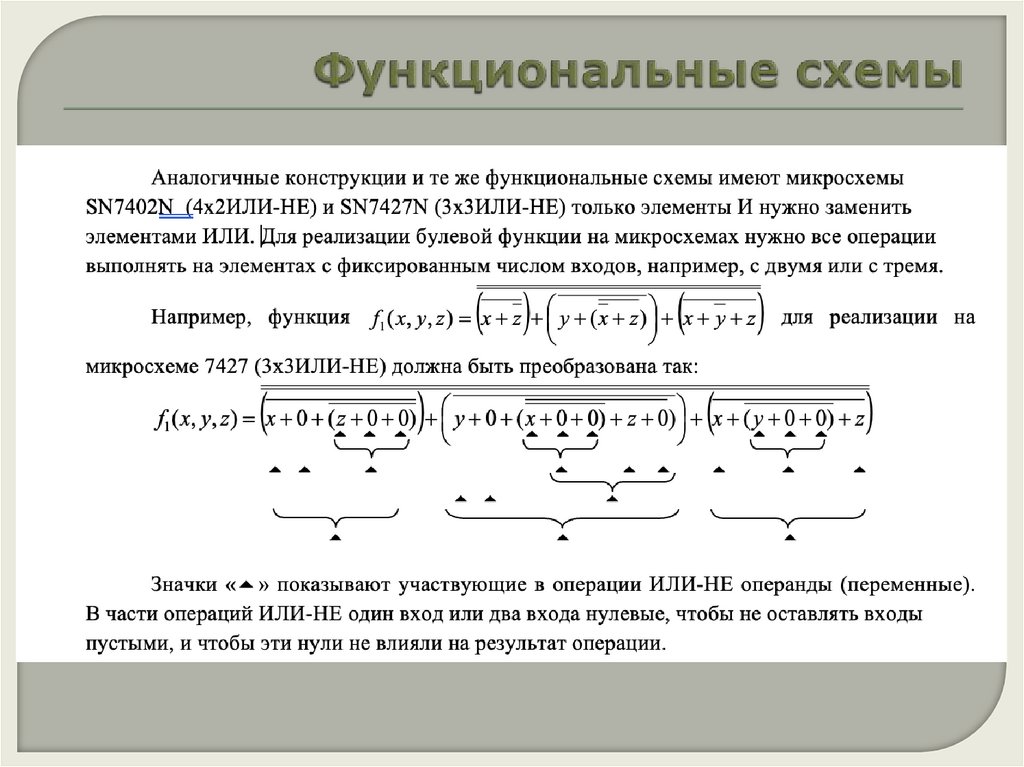

5. Функциональные схемы

6.

7. Микросхема. «Цоколевка»

CD74HC27 высокоскоростной строенный КМОП логическийэлемент ИЛИ-НЕ с тремя входами: 3 х 3ИЛИ-НЕ

f ( A, B, C ) Y A B C

1

2

3

4

5

6

7

1

1А

2

1В

3

2А

4

2В

5

2С

6

2Y

7 GND

14

13

12

11

10

9

8

14

Vсс

13

1С

12

1Y

11

3С

10

3В

9

3А

3Y 8

1

1

1

1

&

&

Vcc

1А

1В

2А

2В

2С

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

&

1

Vcc

K размн

I max

10

I "1"

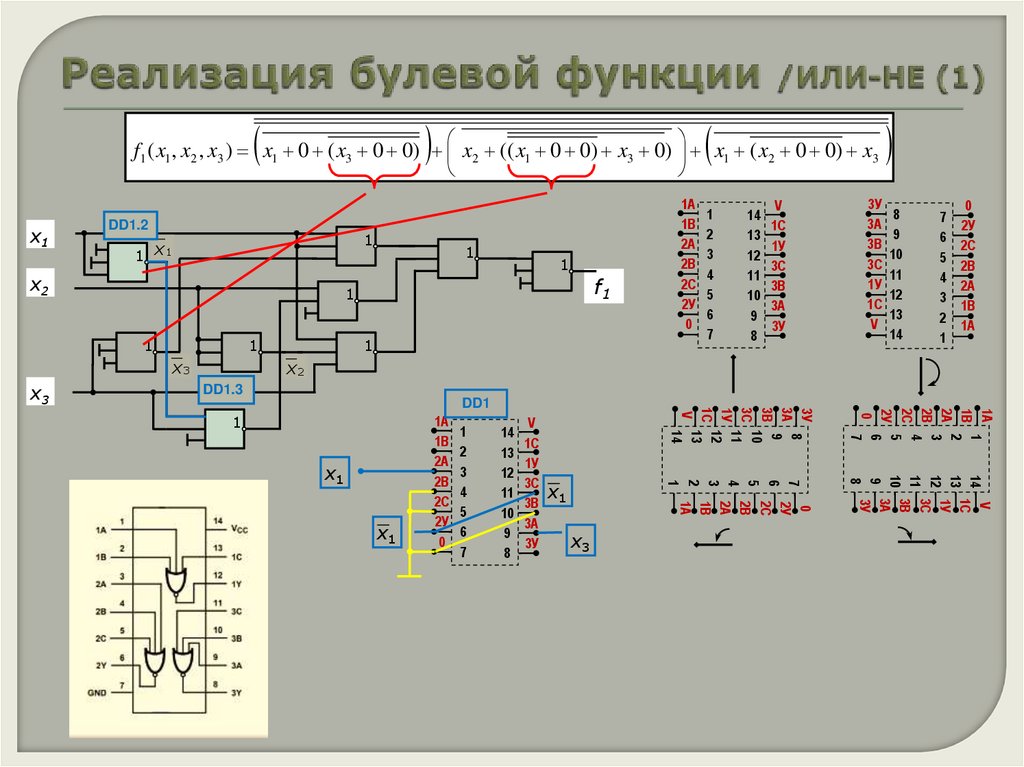

8. Реализация булевой функции /ИЛИ-НЕ (1)

f1 ( x1 , x2 , x3 ) x1 0 ( x3 0 0) x2 (( x1 0 0) x3 0) x1 ( x2 0 0) x3x1

DD1.2

1

1

x1

x2

1

f1

1

1

1

1

x3

x3

1

1А

1В

2А

2В

2С

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

3У

8

3А

9

3В

10

3С

11

1У

12

1С

13

V

14

7

6

5

4

3

2

1

0

2У

2С

2В

2А

1В

1А

x2

DD1.3

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

V

1С

1У

3С

x

3В 1

3А

x3

3У

0

2У

2С

2В

2А

1В

1А

x1

14

13

12

11

10

9

8

1А

1В

2А

2В

2С

2У

0

x1

1

2

3

4

5

6

7

7

6

5

4

3

2

1

1

3У

8

3А

9

3В

10

3С

11

1У

12

1С

13

V

14

DD1

1А

1В

2А

2В

2С

2У

0

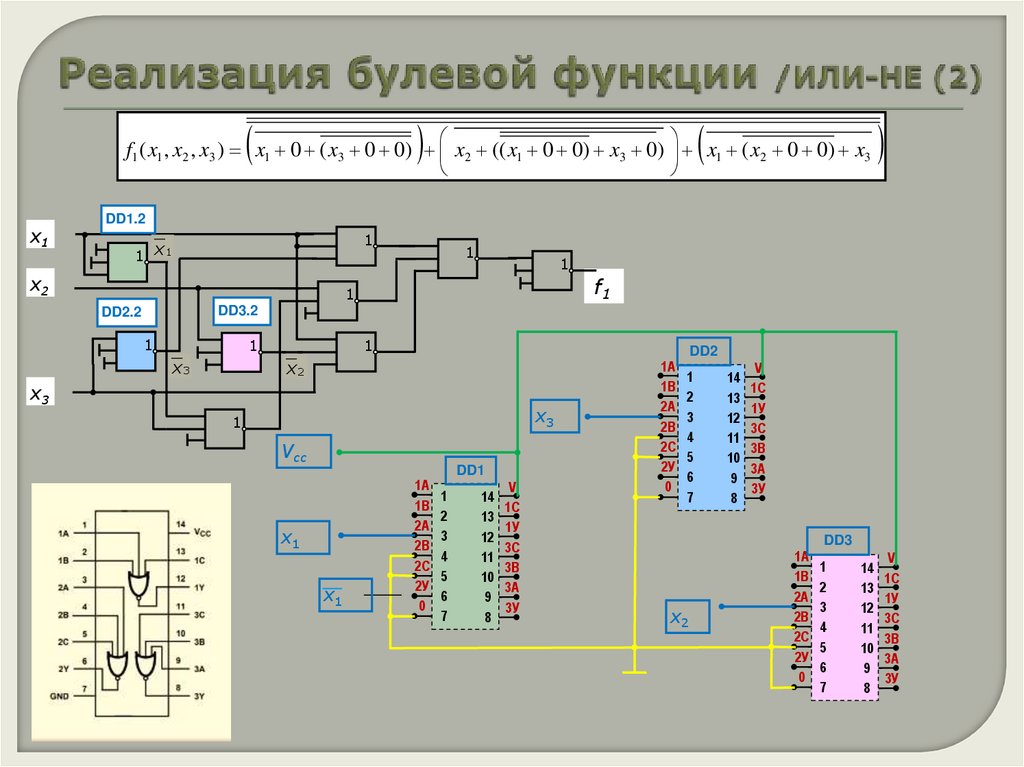

9. Реализация булевой функции /ИЛИ-НЕ (2)

x3 x ( x 0 0) xf1 ( x1 , x2 , x3 ) x1 0 f0((xx3 1 , x

0 2 , x

0)3 ) xx12x 3 ( ( xx1 2 ( 0x1 0)x 3 )x3 x01)x 2

1

2

3

x1

DD1.2

1

1

x1

x2

1

1

f1

1

DD3.2

DD2.2

1

1

1

x3

x2

x3

x3

1

Vcc

x1

x1

1А

1В

2А

2В

2С

2У

0

DD1

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD2

1

2

3

4

5

6

7

x2

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD3

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

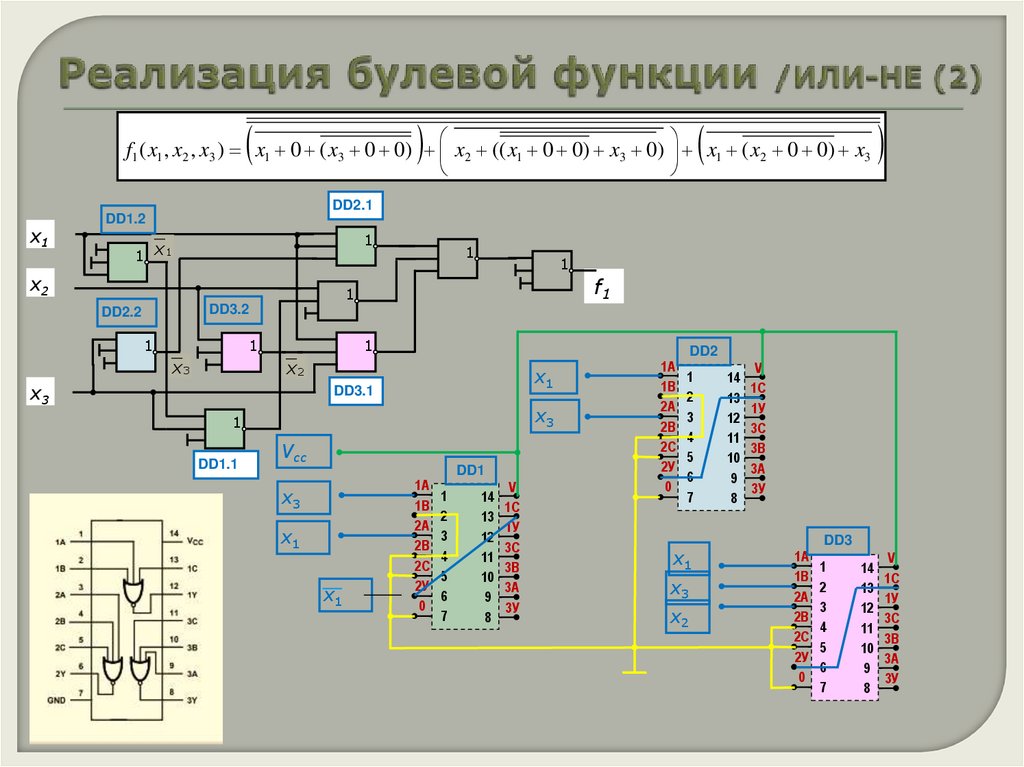

10. Реализация булевой функции /ИЛИ-НЕ (2)

x3 x ( x 0 0) xf1 ( x1 , x2 , x3 ) x1 0 f0((xx3 1 , x

0 2 , x

0)3 ) xx12x 3 ( ( xx1 2 ( 0x1 0)x 3 )x3 x01)x 2

1

2

3

DD2.1

x1

DD1.2

1

1

x1

x2

1

1

f1

1

DD3.2

DD2.2

1

1

1

x3

x2

x3

x1

DD3.1

x3

1

DD1.1

Vcc

x3

x1

x1

1А

1В

2А

2В

2С

2У

0

DD1

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD2

1

2

3

4

5

6

7

x1

x3

x2

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD3

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

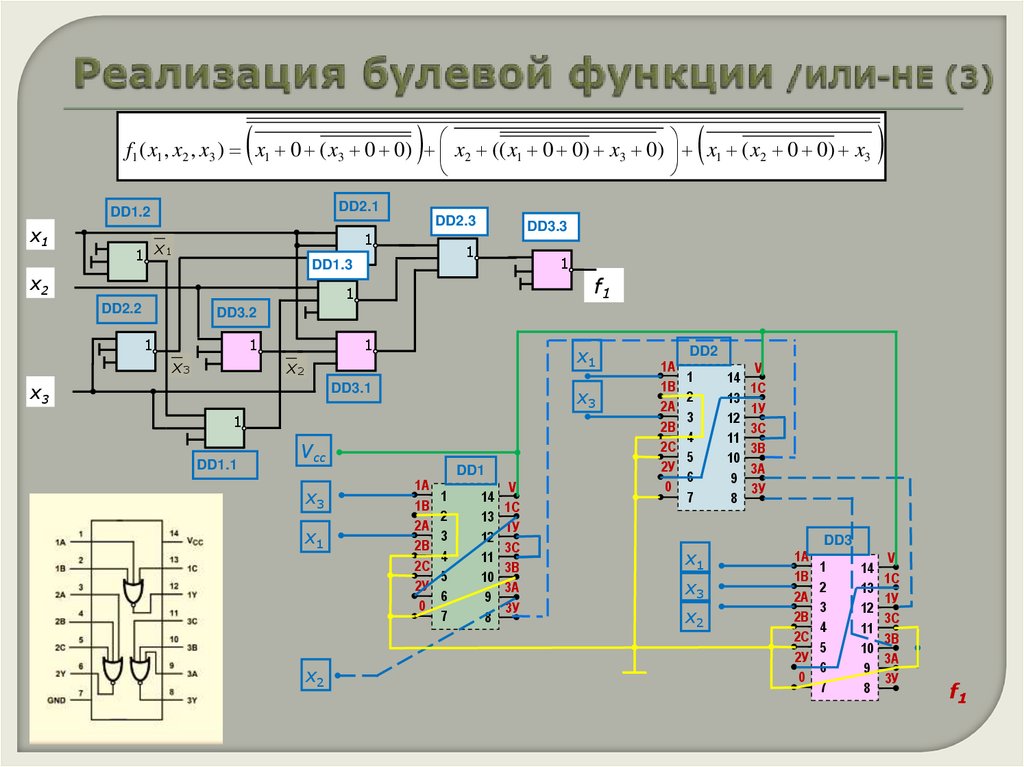

11. Реализация булевой функции /ИЛИ-НЕ (3)

x3 x ( x 0 0) xf1 ( x1 , x2 , x3 ) x1 0 f0((xx3 1 , x

0 2 , x

0)3 ) xx12x 3 ( ( xx1 2 ( 0x1 0)x 3 )x3 x01)x 2

1

2

3

DD2.1

DD1.2

x1

1

DD2.3

1

x1

1

DD1.3

x2

DD3.3

1

f1

1

DD2.2

DD3.2

1

1

1

x3

x1

x2

x3

DD3.1

x3

1

DD1.1

Vcc

x3

x1

x2

1А

1В

2А

2В

2С

2У

0

DD1

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD2

1

2

3

4

5

6

7

x1

x3

x2

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD3

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

f1

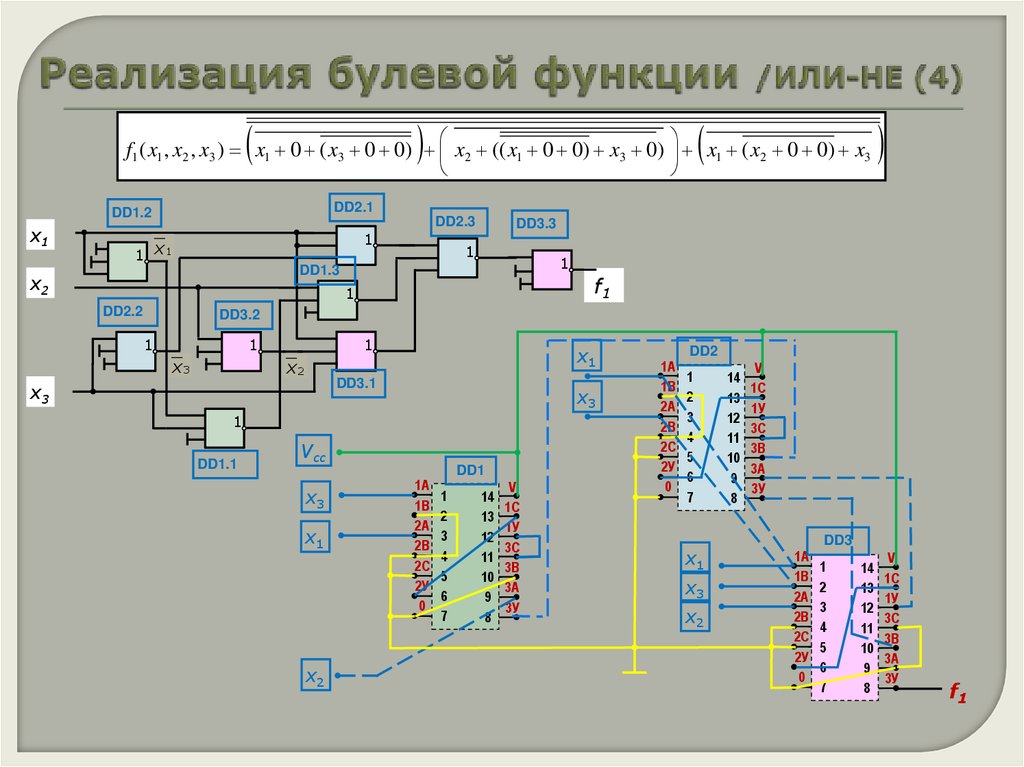

12. Реализация булевой функции /ИЛИ-НЕ (4)

x3 x ( x 0 0) xf1 ( x1 , x2 , x3 ) x1 0 f0((xx3 1 , x

0 2 , x

0)3 ) xx12x 3 ( ( xx1 2 ( 0x1 0)x 3 )x3 x01)x 2

1

2

3

DD2.1

DD1.2

x1

1

DD2.3

1

x1

DD3.3

1

1

DD1.3

x2

f1

1

DD2.2

DD3.2

1

1

1

x3

x1

x2

DD3.1

x3

x3

1

DD1.1

Vcc

x3

x1

x2

1А

1В

2А

2В

2С

2У

0

DD1

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD2

1

2

3

4

5

6

7

x1

x3

x2

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD3

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

f1

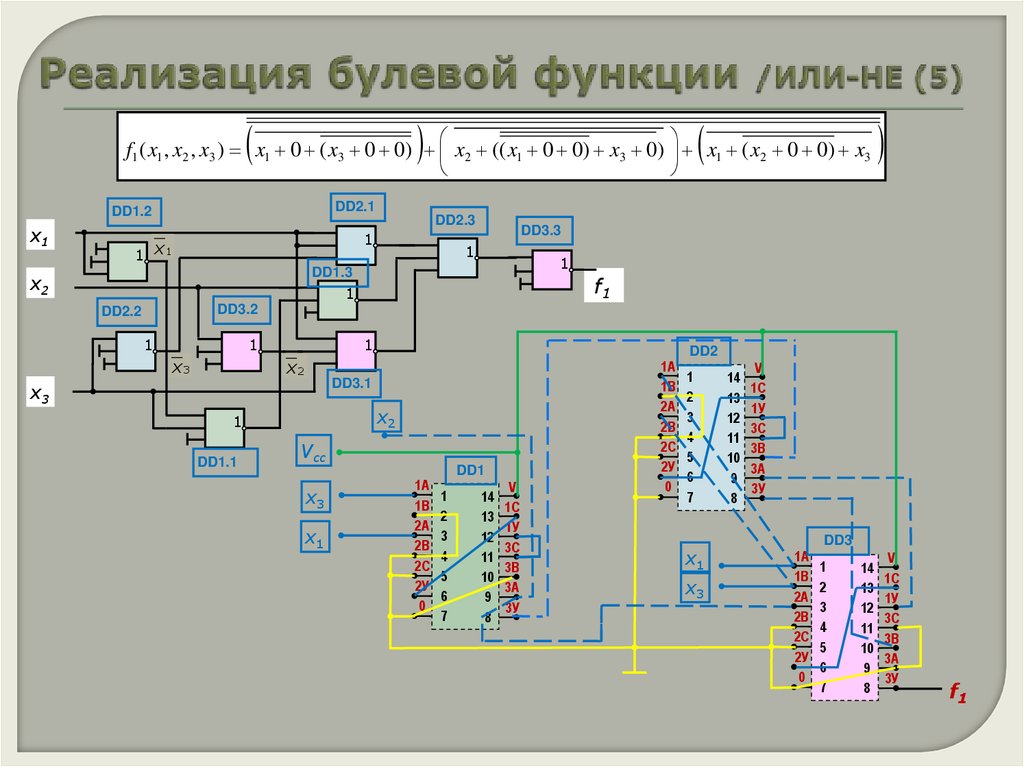

13. Реализация булевой функции /ИЛИ-НЕ (5)

x3 x ( x 0 0) xf1 ( x1 , x2 , x3 ) x1 0 f0((xx3 1 , x

0 2 , x

0)3 ) xx12x 3 ( ( xx1 2 ( 0x1 0)x 3 )x3 x01)x 2

1

2

3

DD2.1

DD1.2

x1

DD2.3

1

1 x1

DD3.3

1

1

DD1.3

x2

f1

1

DD3.2

DD2.2

1

1

1

x3

x2

DD3.1

x3

x2

1

DD1.1

Vcc

x3

x1

1А

1В

2А

2В

2С

2У

0

DD1

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD2

1

2

3

4

5

6

7

x1

x3

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD3

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

f1

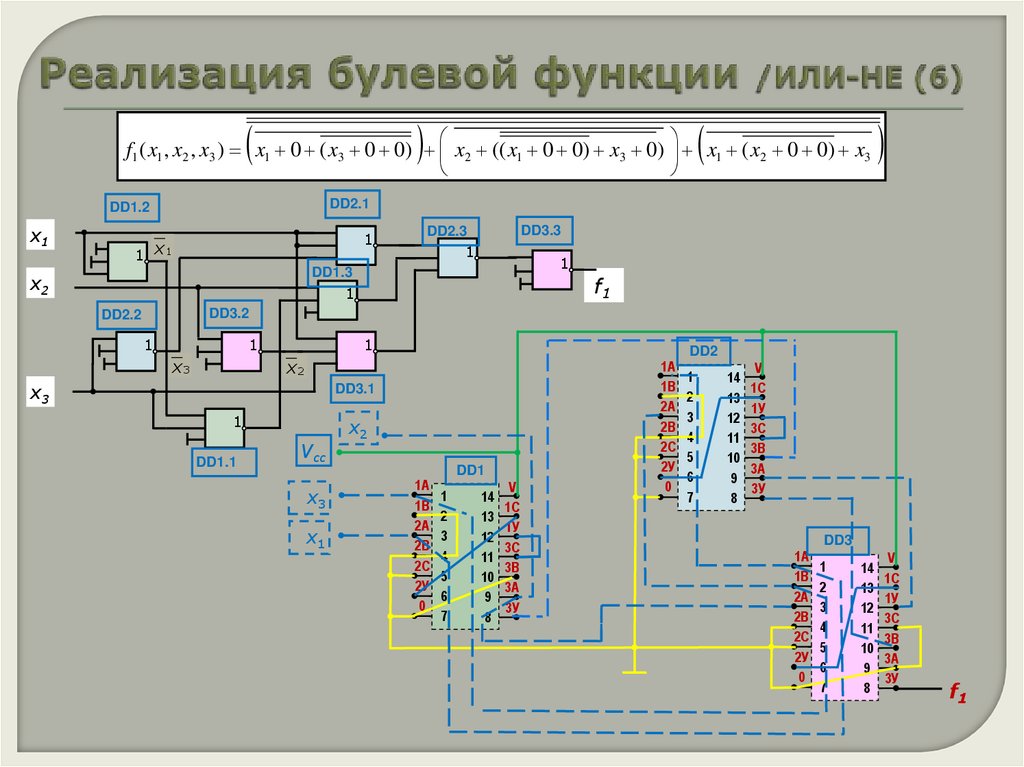

14. Реализация булевой функции /ИЛИ-НЕ (6)

x3 x ( x 0 0) xf1 ( x1 , x2 , x3 ) x1 0 f0((xx3 1 , x

0 2 , x

0)3 ) xx12x 3 ( ( xx1 2 ( 0x1 0)x 3 )x3 x01)x 2

1

2

3

DD2.1

DD1.2

x1

1

1 x1

DD3.3

DD2.3

1

1

DD1.3

x2

f1

1

DD3.2

DD2.2

1

1

1

x3

x2

x3

DD3.1

1

DD1.1

Vcc

x3

x1

x2

1А

1В

2А

2В

2С

2У

0

DD1

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD2

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

1А

1В

2А

2В

2С

2У

0

DD3

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

1С

1У

3С

3В

3А

3У

f1

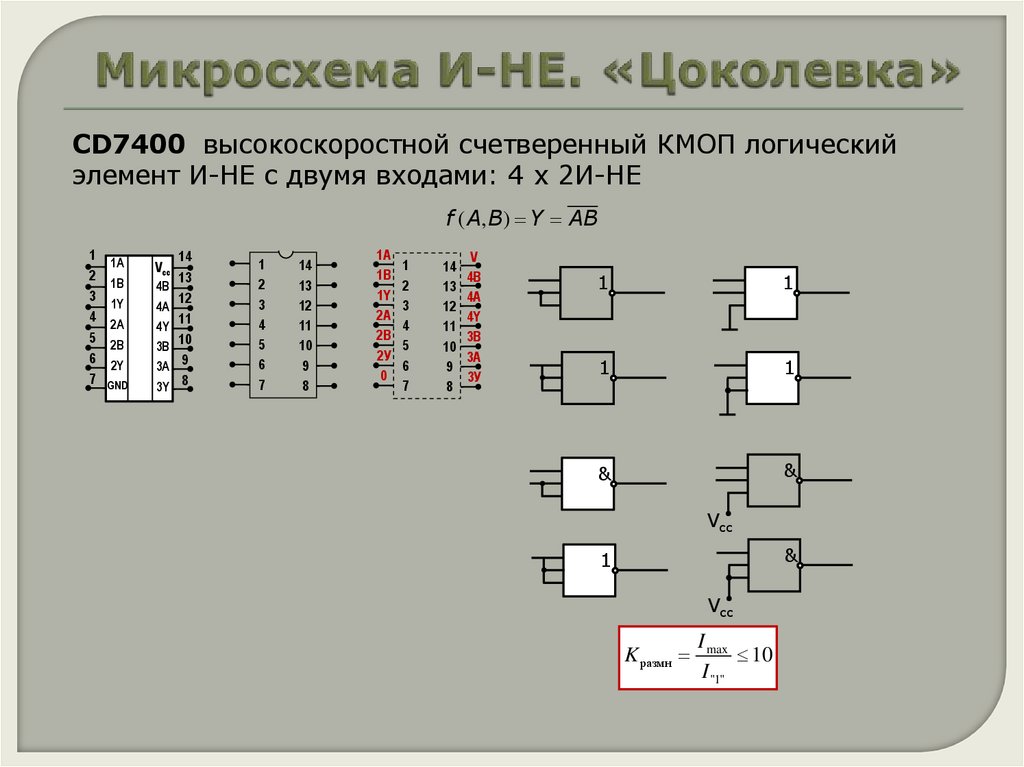

15. Микросхема И-НЕ. «Цоколевка»

CD7400 высокоскоростной счетверенный КМОП логическийэлемент И-НЕ с двумя входами: 4 х 2И-НЕ

f ( A, B) Y AB

1

1А

2

1В

3

1Y

4

2A

5

2B

6

2Y

7 GND

14

13

4B

12

4A

11

4Y

10

3В

9

3А

3Y 8

Vсс

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1А

1В

1Y

2A

2B

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

4B

4A

4Y

3В

3А

3У

1

1

1

1

&

&

Vcc

&

1

Vcc

K размн

I max

10

I "1"

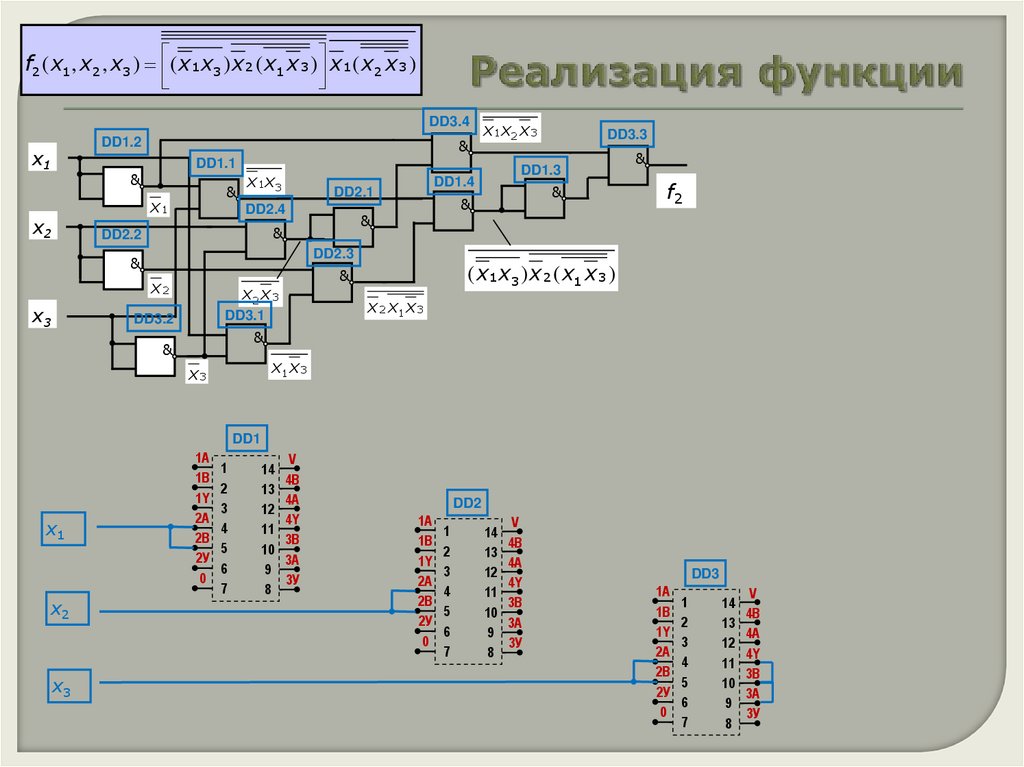

16. Реализация функции

f2 ( x1 , x2 , x3 ) ( x1 x3 ) x 2 ( x1 x 3 ) x1 ( x2 x 3 )DD3.4

DD1.2

x1

&

DD1.1

&

&

x1

x2

x1 x3

DD2.3

&

x2

x3

f2

x 2 x1 x 3

DD3.1

DD3.2

&

( x1 x3 ) x 2 ( x1 x 3 )

&

x2 x 3

&

&

&

&

DD2.2

DD3.3

DD1.3

DD1.4

DD2.1

DD2.4

x1 x2 x 3

&

&

x1 x 3

x3

DD1

x1

x2

x3

1А

1В

1Y

2A

2B

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

4B

4A

4Y

3В

3А

3У

DD2

1А

1В

1Y

2A

2B

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

4B

4A

4Y

3В

3А

3У

DD3

1А

1В

1Y

2A

2B

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

4B

4A

4Y

3В

3А

3У

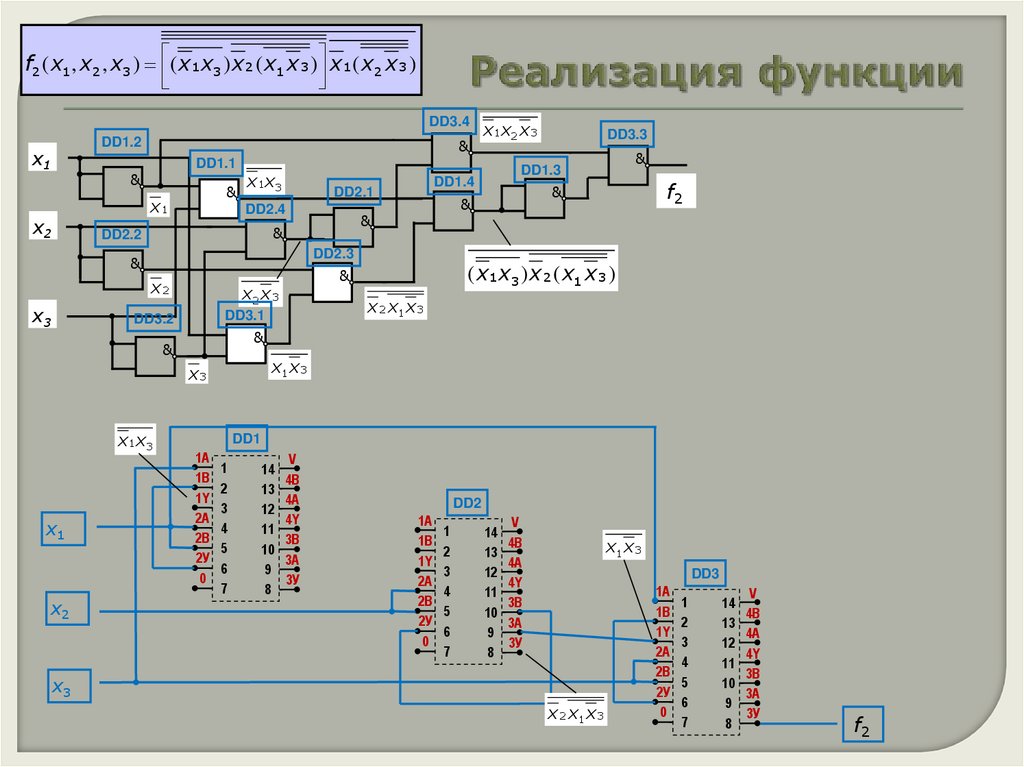

17. Реализация функции

f2 ( x1 , x2 , x3 ) ( x1 x3 ) x 2 ( x1 x 3 ) x1 ( x2 x 3 )DD3.4

DD1.2

x1

&

DD1.1

&

&

x1

x2

x1 x3

DD2.3

&

x2

x3

&

&

x1 x 3

x3

x1 x3

x1

x2

x 2 x1 x 3

DD3.1

DD3.2

f2

( x1 x3 ) x 2 ( x1 x 3 )

&

x2 x 3

&

&

&

&

&

DD2.2

DD3.3

DD1.3

DD1.4

DD2.1

DD2.4

x1 x2 x 3

DD1

1А

1В

1Y

2A

2B

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

4B

4A

4Y

3В

3А

3У

DD2

1А

1В

1Y

2A

2B

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

4B

4A

4Y

3В

3А

3У

x1 x 3

DD3

x3

x 2 x1 x 3

1А

1В

1Y

2A

2B

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

4B

4A

4Y

3В

3А

3У

f2

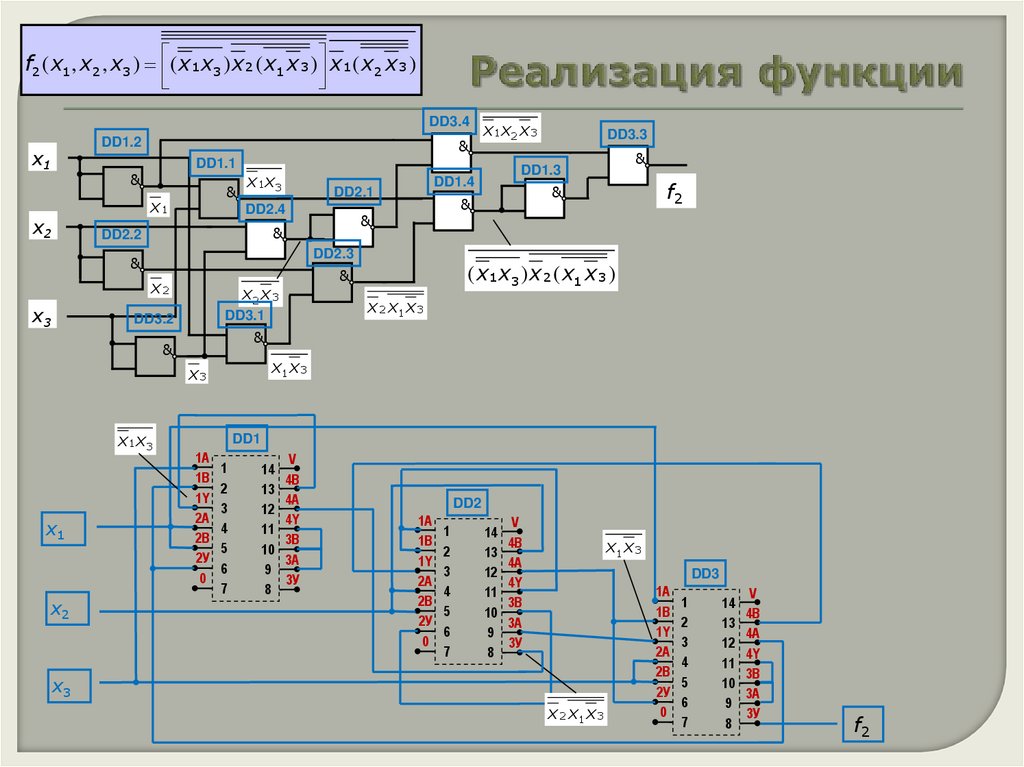

18. Реализация функции

f2 ( x1 , x2 , x3 ) ( x1 x3 ) x 2 ( x1 x 3 ) x1 ( x2 x 3 )DD3.4

DD1.2

x1

&

DD1.1

&

&

x1

x2

x1 x3

DD2.3

&

x2

x3

&

&

x1 x 3

x3

x1 x3

x1

x2

x 2 x1 x 3

DD3.1

DD3.2

f2

( x1 x3 ) x 2 ( x1 x 3 )

&

x2 x 3

&

&

&

&

&

DD2.2

DD3.3

DD1.3

DD1.4

DD2.1

DD2.4

x1 x2 x 3

DD1

1А

1В

1Y

2A

2B

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

4B

4A

4Y

3В

3А

3У

DD2

1А

1В

1Y

2A

2B

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

4B

4A

4Y

3В

3А

3У

x1 x 3

DD3

x3

x 2 x1 x 3

1А

1В

1Y

2A

2B

2У

0

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

4B

4A

4Y

3В

3А

3У

f2

19.

20.

4 х 2И-НЕ2 х 2ИЛИ-НЕ

3 х 3И-НЕ

4 х 2ИЛИ-НЕ