Similar presentations:

Организация работы и функционирование процессора

1. Организация работы и функционирование процессора

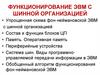

ОРГАНИЗАЦИЯ РАБОТЫ ИФУНКЦИОНИРОВАНИЕ

ПРОЦЕССОРА

Устройства,

входящие в состав процессора

2. Центральный процессор (ЦП)

■это основное устройство ЭВМ, осуществляющее

обработку данных и выполняющее функции управления

системой (инициирование ввода/вывода, управление

доступом к основной памяти, обработку сигналов,

поступающих от различных внешних устройств и от

внутренних устройств ЭВМ и др.).

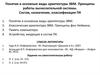

3. 1. Логическая структура ЦП

■ Организация центрального процессора (ЦП) определяетсяархитектурой и принципами работы ЭВМ (состав и

форматы команд, представление чисел, способы

адресации, общая организация машины и её основные

элементы),

а

также

технико-экономическими

показателями.

4. Логическая структура ЦП

5. Логическую структуру ЦП представляет ряд функциональных средств

Логическую структуру ЦП представляетряд функциональных средств

■ Средства обработки обеспечивают выполнение операций с числами с фиксированной

точкой, с числами с плавающей точкой, с десятичными данными и с полями

переменной длины.

■ Локальная память состоит из регистров общего назначения, регистров с плавающей

точкой, а также управляющих регистров.

■ Средства управления памятью подразделяются на средства управления доступом к

ОП, средства предварительной выборки команд и данных, буферную память и

средства защиты памяти.

■ Средства управления вводом/выводом обеспечивают приоритетный доступ программ

к периферийным устройствам через каналы ввода/вывода (или контроллеры).

■ К системным средствам относятся средства службы времени: часы астрономического

времени, таймер, коммутатор и т. д.

6. Существует обязательный минимальный (стандартный) набор функциональных средств для каждого типа центрального процессора. Он

включает в себя:■ регистры общего назначения;

■ средства выполнения стандартного набора операций;

■ средства управления вычислительным процессом.

Конкретная реализация ЦП может различаться составом

средств, способом их реализации, техническими

параметрами.

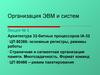

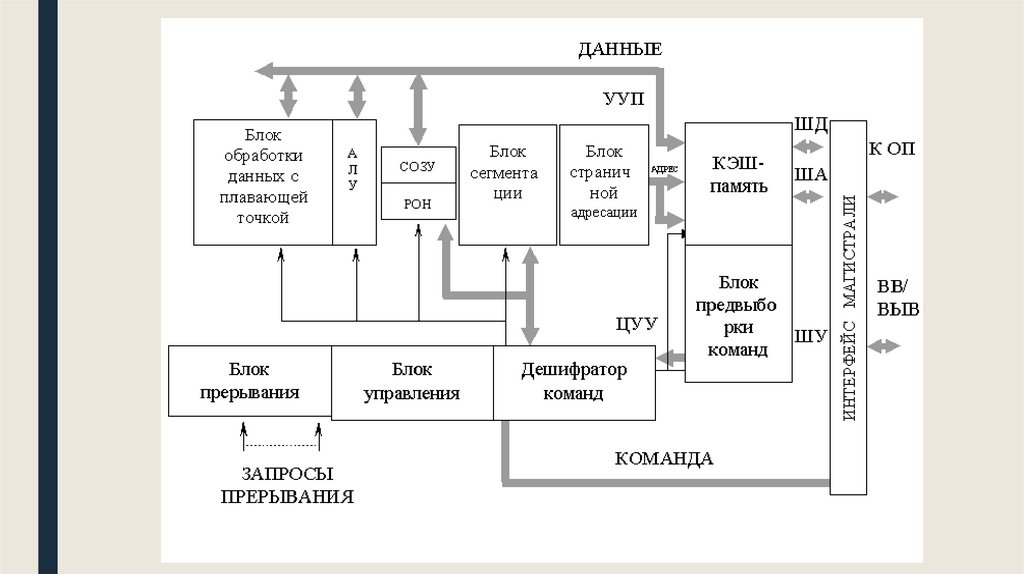

7. 2. Структурная схема процессора

Все функциональные средства по своей структуре разбиваются наследующие устройства:

■ Центральное устройство управления;

■ Арифметико-логическое устройство;

■ Устройство управления памятью;

■ Сверхоперативное запоминающее устройство;

■ Устройство предварительной выборки команд и данных;

■ Интерфейс магистрали.

8.

9. Центральное устройство управления (ЦУУ) включает дешифратор команд, блок управления и блок прерываний.

Центральное устройство управления(ЦУУ) включает дешифратор команд, блок

управления и блок прерываний.

■ Дешифратор команд дешифрирует (декодирует) команды, которые

поступают из блока предварительной выборки.

■ Блок управления (БУ) формирует последовательности управляющих

сигналов, которые поступают на все блоки процессора,

обеспечивающие выполнение текущей команды и переход к

выполнению следующей.

■ Блок прерывания обеспечивает реакцию ЭВМ на запросы

прерываний от различных источников (устройств) внутри и вне ЦП.

10. Арифметико-логическое устройство (АЛУ) выполняет все арифметические и логические операции ЭВМ. В состав устройства входят:

Арифметико-логическое устройство(АЛУ) выполняет все арифметические и

логические операции ЭВМ. В состав

устройства входят:

• сумматоры,

• буферные и рабочие регистры,

• специализированные аппаратные средства (блок ускоренного

умножения),

• собственный блок управления (иногда).

Во многих современных процессорах операции с плавающей точкой

выполняются в отдельном блоке, который имеет собственные

регистры данных, регистры управления и работает параллельно с

блоком операций с фиксированной точкой.

11. Сверхоперативное запоминающее устройство (СОЗУ)–

■ Сверхоперативное запоминающее устройство (СОЗУ)–(регистровый файл) содержит регистры общего

назначения, в которых хранятся данные и адреса.

12. Устройство предвыборки команд и данных включает блок предвыборки команд и внутреннюю кэш-память процессора (кэш первого

уровня).■ Блок предвыборки команд осуществляет формирование очереди команд,

причем выборка из памяти осуществляется в промежутках между

магистральными циклами команд.

■ Во внутренней кэш-памятиосуществляется буферизация часто используемых

команд и данных. Благодаря этому существенно повышается производительность

процессора, сокращается число обращений к ОП.

13. Устройство управления памятью (диспетчер памяти) предназначено для сопряжения ЦП и подсистемы ввода/вывода с ОП.

■ Оно состоит из блока сегментации и блока страничной адресации,осуществляющих двухступенчатое формирование физического

адреса ячейки памяти: сначала в пределах сегмента, а затем в

пределах страницы.

■ Наличие двух этих блоков, их параллельное функционирование

обеспечивают максимальную гибкость проектируемой системы.

■ Сегментация полезна для организации памяти локальных модулей и

является инструментом программиста, в то время как страницы

позволяют системному программисту эффективно использовать

физическую память ЭВМ.

14. Интерфейс магистрали

■ Интерфейс магистрали реализует протоколы обмена(связь по определенным правилам) ЦП с памятью,

каналами (контроллерами) ввода/вывода и другими

активными устройствами системы ЭВМ.

■ Обмен осуществляется с помощью шин данных, адреса и

управления.

15. В современных суперскалярных процессорах может использоваться от 2 до 6 параллельно работающих исполнительных устройств. Это

могут быть:■ несколько целочисленных устройств;

■ устройство плавающей точки (блок FPU);

■ устройство выполнения переходов;

■ устройство загрузки/записи.

16. Перспективные типы процессоров ЭВМ

17. Ассоциативные процессоры (associative processors)

это специализированные устройства в компьютернойархитектуре, которые обрабатывают данные на основе

ассоциативной памяти.

В отличие от традиционных процессоров, где доступ к

данным происходит по адресу (как в RAM), здесь поиск и

обработка ведутся по содержимому данных.

Это позволяет параллельно обрабатывать большие объемы

информации, делая их полезными для задач вроде поиска,

фильтрации и анализа в реальном времени.

18. Матричный процессор (array processor)

Матричный процессор (arrayprocessor)

это процессор ЭВМ, представляющий собой сеть из более

простых процессоров, обладающих своей собственной памятью,

работающих параллельно и обменивающихся информацией со

своими ближайшими соседями.

Такие процессоры относятся к архитектуре с одним потоком

команд и несколькими потоками данных (SIMD).

SIMD (Single Instruction, Multiple Data) — технология

параллельной обработки данных, которая позволяет выполнить

одну инструкцию для нескольких элементов данных

одновременно. Также SIMD — один из классов вычислительных

систем в классификации Флинна.

19. Клеточные и ДНК-процессоры

Клеточные и ДНК-процессорытермины, которые относятся к биокомпьютингу —

междисциплинарной области, объединяющей биологию,

информатику и инженерию.

Она включает проектирование и создание вычислительных

систем с использованием биологических материалов, таких

как ДНК, белки, ферменты и живые клетки.

20. Коммуникационные процессоры (интерфейсные процессоры, контроллеры связи)

Коммуникационныепроцессоры (интерфейсные

процессоры, контроллеры связи)

это устройства, которые оптимизированы для сетевой

работы и взаимодействуют с другими процессорными

узлами, сетями или периферийными устройствами.

Цель — разгрузить вычислительный процессор от нагрузки,

связанной с передачей сообщений между узлами.

21. Процессоры для работы с базами данных (серверные процессоры)

Процессоры для работы с базамиданных (серверные процессоры)

это специализированные вычислительные системы,

предназначенные для выполнения всех или некоторых

функций систем управления базами данных (СУБД).

Они выполняют функции управления и распространения

данных, обеспечивают дистанционный доступ к информации

через шлюзы, а также репликацию обновлённых данных.

22. Потоковые процессоры

Потоковые процессорыэто процессоры, в основе работы которых лежит принцип

обработки многих данных с помощью одной команды.

Такие процессоры принадлежат к архитектуре SIMD (single

instruction stream / multiple data stream).

23. Нейронный процессор (Neural Processing Unit, NPU)

специализированный микропроцессор, созданный дляускорения задач искусственного интеллекта (ИИ) и

машинного обучения, включая алгоритмы искусственных

нейронных сетей и компьютерное зрение.

Также известен как ускоритель ИИ или процессор глубокого

обучения.

24. Процессоры с многозадачной (нечёткой) логикой (fuzzy logic)

Процессоры с многозадачной(нечёткой) логикой (fuzzy logic)

это специализированные аппаратные средства, которые

позволяют выполнять нечёткие операции и приближённые

рассуждения (нечёткий вывод) в соответствии с правилами

логического вывода.

Такие процессоры работают на базе нечёткой математики,

которая позволяет работать с входными данными,

постоянно меняющимися во времени, и значениями,

которые невозможно задать однозначно.

electronics

electronics