Similar presentations:

Иерархия памяти современных компьютеров. Разрыв производительности процессора и памяти

1. Иерархия памяти современных компьютеров

2. Разрыв производительности процессора и памяти

3. Иерархия памяти

Описание некоторого уровня иерархиипамяти:

º Размещение блока (где может размещаться блок

на верхнем уровне иерархии?).

º Идентификация блока (как найти блок, когда он

находится на верхнем уровне?).

º Замещение блоков (какой блок должен быть

замещен в случае промаха?).

º Стратегия записи (что происходит во время

записи? ).

4. Стратегии размещения блоков в кэш-памяти

º Если каждый блок основной памяти имеет только одно фиксированное место, на которомон может появиться в кэш-памяти, то такая кэш-память называется кэшем с прямым

отображением (direct mapped). Это наиболее простая организация кэш-памяти, при

которой для отображения адресов блоков основной памяти на адреса кэш-памяти просто

используются младшие разряды адреса блока. Таким образом, все блоки основной

памяти, имеющие одинаковые младшие разряды в своем адресе, попадают в один блок

кэш-памяти, т.е.

(адрес блока кэш-памяти) =

(адрес блока основной памяти) mod (число блоков в кэш-памяти)

º Если некоторый блок основной памяти может располагаться на любом месте кэш-памяти,

то кэш называется полностью ассоциативным (fully associative).

º Если некоторый блок основной памяти может располагаться на ограниченном множестве

мест в кэш-памяти, то кэш называется множественно-ассоциативным (set associative).

Обычно множество представляет собой группу из двух или большего числа блоков в

кэше.

º Если множество состоит из n блоков, то такое размещение называется множественноассоциативным с n каналами (n-way set associative). Для размещения блока, прежде всего,

необходимо определить множество. Множество определяется младшими разрядами

адреса блока памяти (индексом):

(адрес множества кэш-памяти) =

(адрес блока основной памяти) mod (число множеств в кэш-памяти)

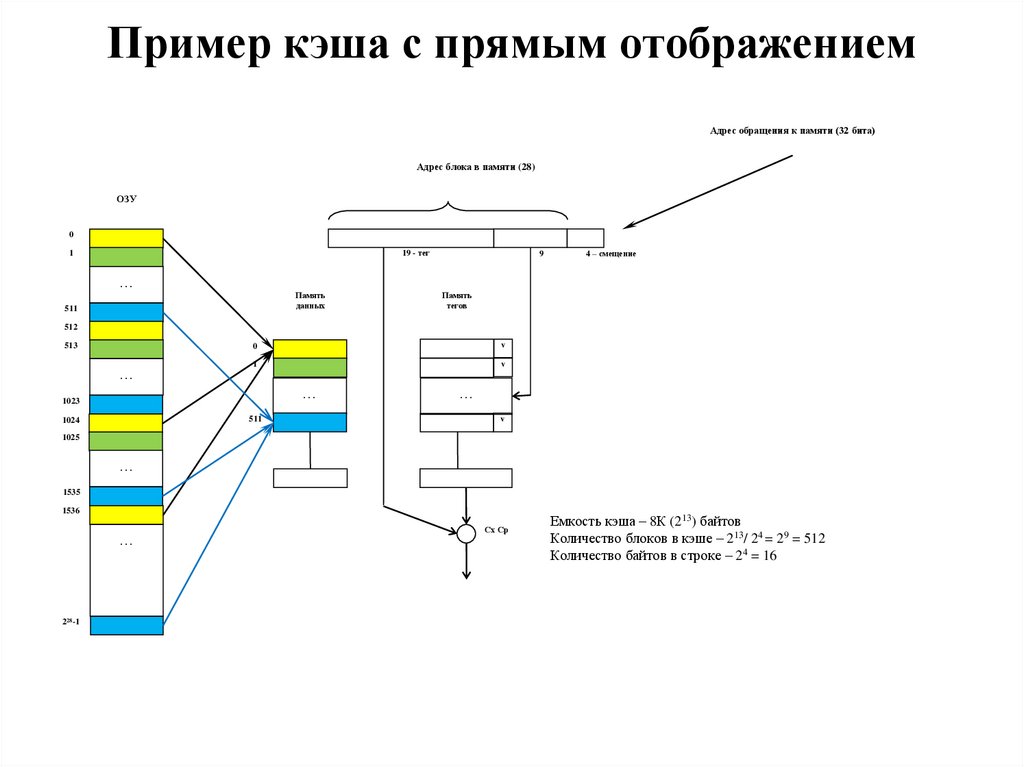

5. Пример кэша с прямым отображением

Адрес обращения к памяти (32 бита)Адрес блока в памяти (28)

ОЗУ

0

19 - тег

1

…

Память

данных

511

9

4 – смещение

Память

тегов

512

513

…

0

v

1

v

…

1023

511

1024

…

v

1025

…

1535

1536

…

228-1

Сх Ср

Емкость кэша – 8К (213) байтов

Количество блоков в кэше – 213/ 24 = 29 = 512

Количество байтов в строке – 24 = 16

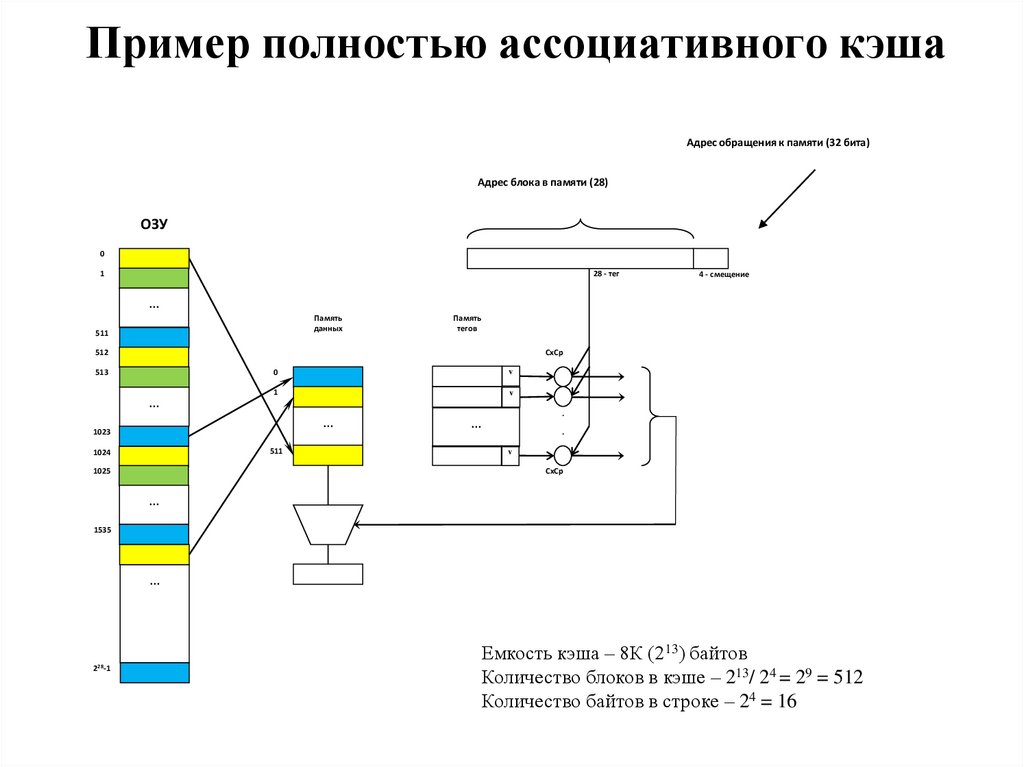

6. Пример полностью ассоциативного кэша

Адрес обращения к памяти (32 бита)Адрес блока в памяти (28)

ОЗУ

0

1

28 - тег

4 - смещение

…

Память

данных

511

Память

тегов

512

СхСр

513

…

0

v

1

v

…

1023

511

1024

1025

.

…

.

v

СхСр

…

1535

…

228-1

Емкость кэша – 8К (213) байтов

Количество блоков в кэше – 213/ 24 = 29 = 512

Количество байтов в строке – 24 = 16

7. Пример 4-канального множественно-ассоциативного кэша

Пример 4-канального множественноассоциативного кэшаЕмкость кэша – 8К (213) байтов)

Количество блоков в кэше – 213/ 24 = 29 = 512

Количество множеств в кэше –

Адрес обращения к памяти (32 бита)

27 = 128

Количество байтов в блоке – 24 = 16

Адрес блока в памяти (28)

ОЗУ

0

21 - тег

1

4 - смещение

7

…

Память данных

127

Память тегов

128

0

129

…

1

…

…

…

…

v

v

v

v

v

v

v

v

…

…

…

…

255

127

256

v

v

v

v

v

v

v

v

257

…

383

384

…

228-1

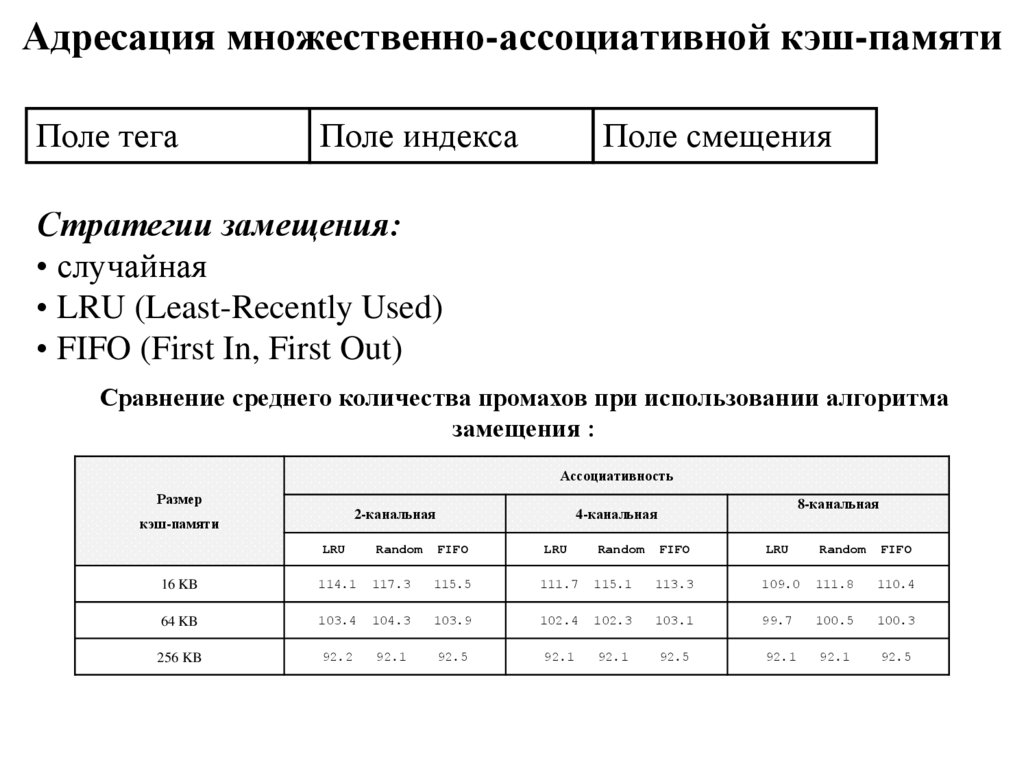

8. Адресация множественно-ассоциативной кэш-памяти

Поле тегаПоле индекса

Поле смещения

Стратегии замещения:

• случайная

• LRU (Least-Recently Used)

• FIFO (First In, First Out)

Сравнение среднего количества промахов при использовании алгоритма

замещения :

Ассоциативность

Размер

2-канальная

кэш-памяти

8-канальная

4-канальная

LRU

Random

FIFO

LRU

Random

FIFO

LRU

Random

FIFO

16 KB

114.1

117.3

115.5

111.7

115.1

113.3

109.0

111.8

110.4

64 KB

103.4

104.3

103.9

102.4

102.3

103.1

99.7

100.5

100.3

256 KB

92.2

92.1

92.5

92.1

92.1

92.5

92.1

92.1

92.5

9. Стратегия записи:

• сквозная запись (write through, store through)• отложенная запись с обратным копированием (write back, copy back,

store in)

При промахе во время записи:

• поместить запись в кэш-память (write allocate)

• не размещать запись в кэш-памяти (запись в окружение – write

around)

10. Причины промахов

Необходимость загрузки в кэш новых данных – Первое обращение кблоку, который отсутствует в кэш-памяти, определяет необходимость

его загрузки в кэш. Промахи такого рода называются также "промахами

холодного старта" или "промахами первого обращения".

Недостаточная емкость – Если в кэш-память не могут поместиться

все блоки, необходимые для выполнения программы, то из-за

необходимости замещения блоков и их повторной выборки возникают

промахи, связанные с недостаточной емкостью кэш-памяти.

Конфликты – Если для размещения блоков используется

множественно-ассоциативная стратегия или стратегия прямого

отображения, то, кроме двух указанных выше причин, в кэш-памяти

могут возникать промахи, связанные с конфликтами. Эти промахи

возникают из-за того, что некоторый блок может быть сначала

выброшен, а затем повторно вызван в кэш-память, когда на одно и то же

множество отображается слишком много блоков. Такие промахи

называются также "промахами, связанными с коллизиями" или

"промахами взаимовлияния".

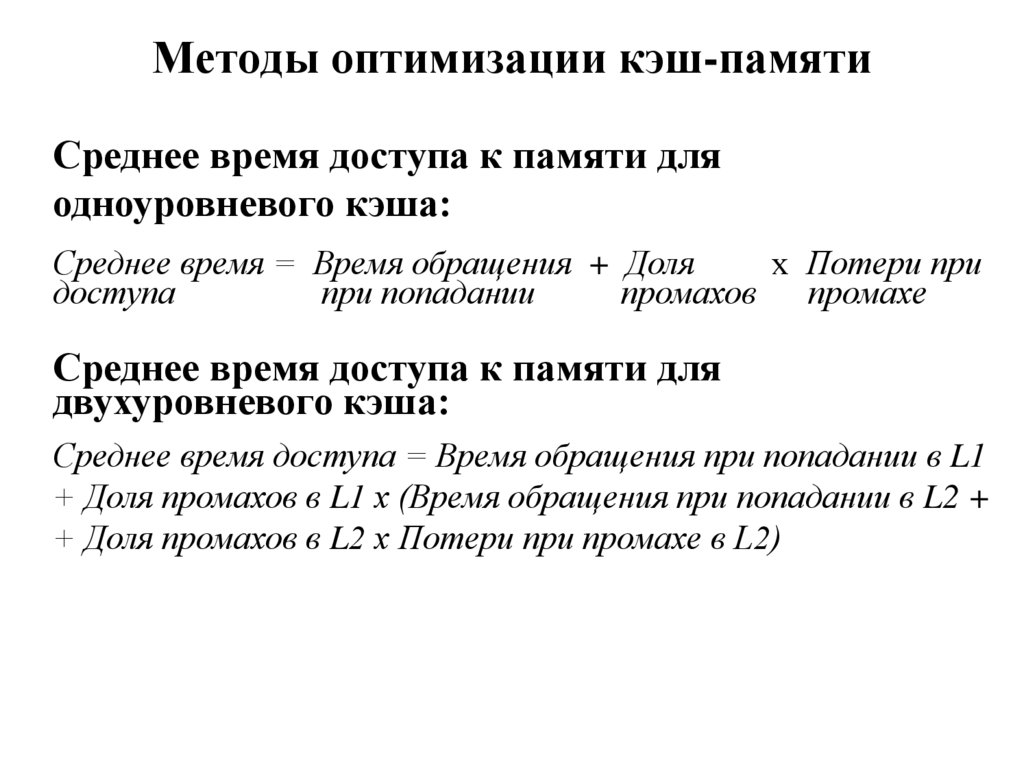

11. Методы оптимизации кэш-памяти

Среднее время доступа к памяти дляодноуровневого кэша:

Среднее время = Время обращения + Доля

х Потери при

доступа

при попадании

промахов промахе

Среднее время доступа к памяти для

двухуровневого кэша:

Среднее время доступа = Время обращения при попадании в L1

+ Доля промахов в L1 x (Время обращения при попадании в L2 +

+ Доля промахов в L2 x Потери при промахе в L2)

12. Увеличение производительности кэш-памяти

МетодВремя

обращения при

попадании

Сложность

аппаратуры

Доля

промахов

Потери

при

промахе

Увеличение размера блока

+

-

Повышение степени ассоциативности

+

Кэш-память с вспомогательным кэшем

+

2

Псевдо-ассоциативная кэш-память

+

2

Аппаратная предварительная выборка

команд и данных

+

2

Предварительная выборка данных

затруднена

Предварительная выборка под

управлением компилятора

+

3

Требует также неблокируемой

кэш-памяти

Специальные методы оптимизации для

уменьшения промахов

+

0

Вопрос ПО

1

Просто для однопроцессорных

систем

1

Сквозная запись + подблок

на 1 слово помогают записям

0

-

1

Установка приоритетов промахов по

чтению над записями

+

Использование подблоков

+

Пересылка требуемого слова первым

+

2

Не блокируемая кэш-память

+

3

Кэш-память второго уровня

+

2

Простой кэш малого размера

Обход преобразования адресов во время

индексации кэш-памяти

Конвейеризация операций записи для

быстрого попадания при записи

-

Примечания

+

+

0

+

2

+

1

Достаточно дорогое оборудование

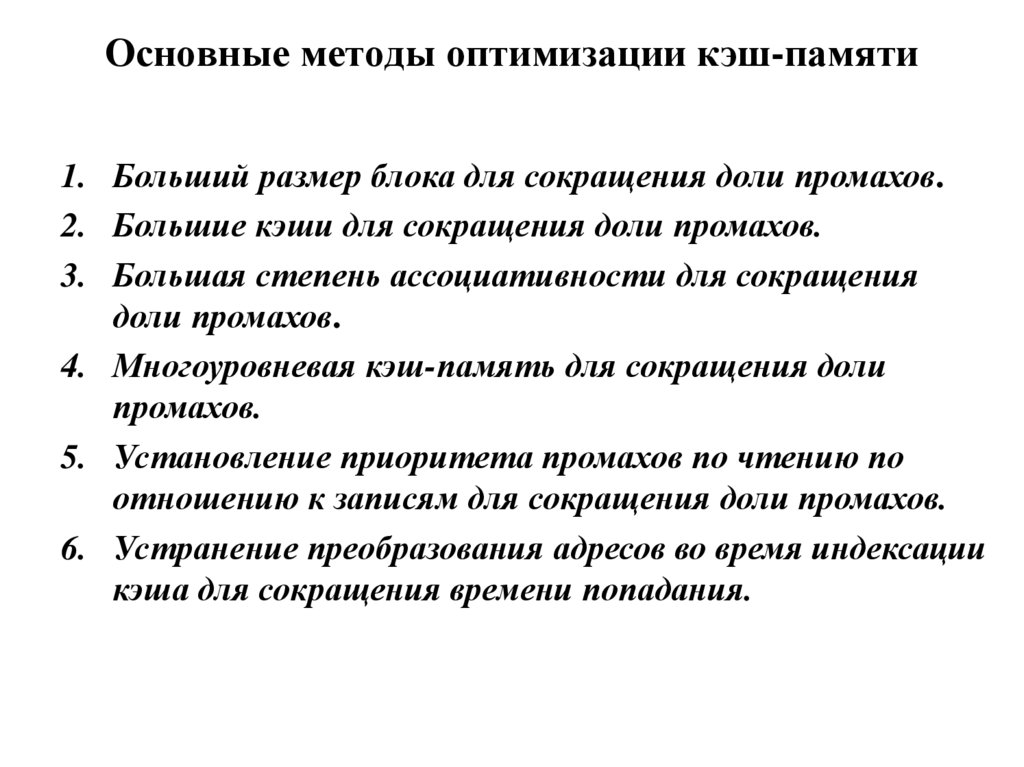

13. Основные методы оптимизации кэш-памяти

1. Больший размер блока для сокращения доли промахов.2. Большие кэши для сокращения доли промахов.

3. Большая степень ассоциативности для сокращения

доли промахов.

4. Многоуровневая кэш-память для сокращения доли

промахов.

5. Установление приоритета промахов по чтению по

отношению к записям для сокращения доли промахов.

6. Устранение преобразования адресов во время индексации

кэша для сокращения времени попадания.

14. Сравнение времени доступа к кэш-памяти при варьировании ее объема и степени ассоциативности

15. Пять категорий современных методов оптимизации кэш-памяти с точки зрения 5 метрик (времени попадания, доли промахов, потерь при

промахе, пропускной способности кэш-памяти ипотребляемой мощности)

1. Сокращение времени попадания – Небольшие и простые кэши

первого уровня и прогнозирование номера канала (использовалось в

Pentium 4). Оба метода в общем случае уменьшают также

потребляемую мощность.

2. Увеличение пропускной способности кэша – Конвейеризованные

кэши, кэши с несколькими банками и неблокируемые кэши.

3. Сокращение потерь при промахе – Критическое слово первым и

объединение буферов записи. Эти оптимизации мало влияют на

мощность.

4. Сокращение доли промахов – Оптимизации с помощью компилятора.

Очевидно, любое улучшение во время компиляции уменьшает

потребляемую мощность.

5. Сокращение потерь при промахе или доли промахов посредством

распараллеливания – Аппаратная предварительная выборка и

предварительная выборка под управлением компилятора. Эти

оптимизации в общем случае увеличивают потребляемую мощность,

главным образом из-за предварительно выбранных данных, которые

не используются.

16. Сравнение организации кэш-памяти Intel Nehalem и AMD Opteron X4 (Barcelona)

Intel NehalemAMD Opteron X4 (Barcelona)

Организация L1

Раздельный кэш команд и данных

Раздельный кэш команд и данных

Размер L1

По 32 Кб для команд и данных на ядро

По 64 Кб для команд и данных на ядро

Ассоциативность L1

4- канальный I, 8- канальный D

2- канальные

Стратегия замещения L1

Приближенный LRU

LRU

Размер блока L1

64 байта

64 байта

Стратегия записи L1

Обратная запись, запись в окружение

Обратная запись, запись в окружение

Время попадания L1

н/д

3 такта

Организация L2

Общий кэш команд и данных на ядро

Общий кэш команд и данных на ядро

Размер L2

256 Кб

512 Кб

Ассоциативность L2

8- канальный

16- канальный

Стратегия замещения L2

Приближенный LRU

Приближенный LRU

Размер блока L2

64 байта

64 байта

Стратегия записи L2

Обратная запись, запись в окружение

Обратная запись, запись в окружение

Время попадания L2

н/д

9 тактов

Организация L3

Общий кэш команд и данных

Общий кэш команд и данных

Размер L3

8 Мб, общий

2 Мб, общий

Ассоциативность L3

16- канальный

32 канальный

Стратегия замещения L3

н/д

Замещается блок, общий для наименьшего

количества ядер

Размер блока L3

64 байта

64 байта

Стратегия записи L3

Обратная запись, запись в окружение

Обратная запись, запись в окружение

Время попадания L3

н/д

38 тактов

17. Принципы организации основной памяти

Производительность основной памяти:• задержка

• полоса пропускания

Задержка памяти:

• время доступа (access time)

• длительность цикла (cycle time)

Основные типы ЗУПВ (RAM):

• СЗУПВ (SRAM)

• ДЗУПВ (DRAM)

Обращение к ДЗУПВ:

• RAS (row-access strobe) - строб адреса строки

• CAS (column-access strobe) - строб адреса столбца

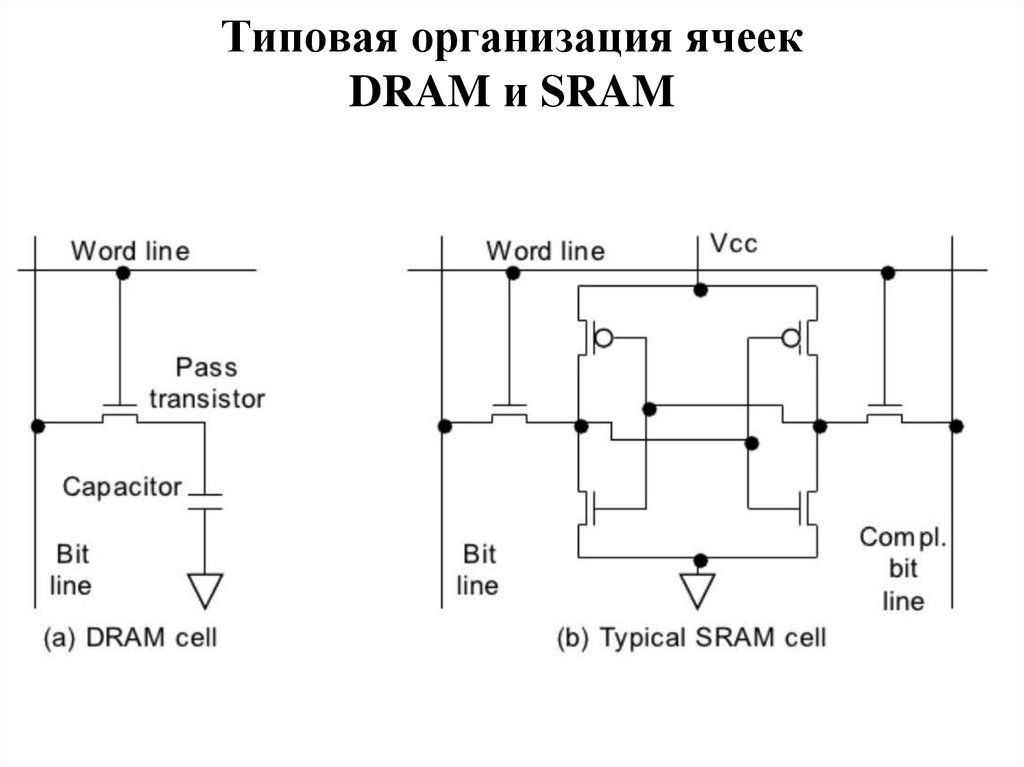

18. Типовая организация ячеек DRAM и SRAM

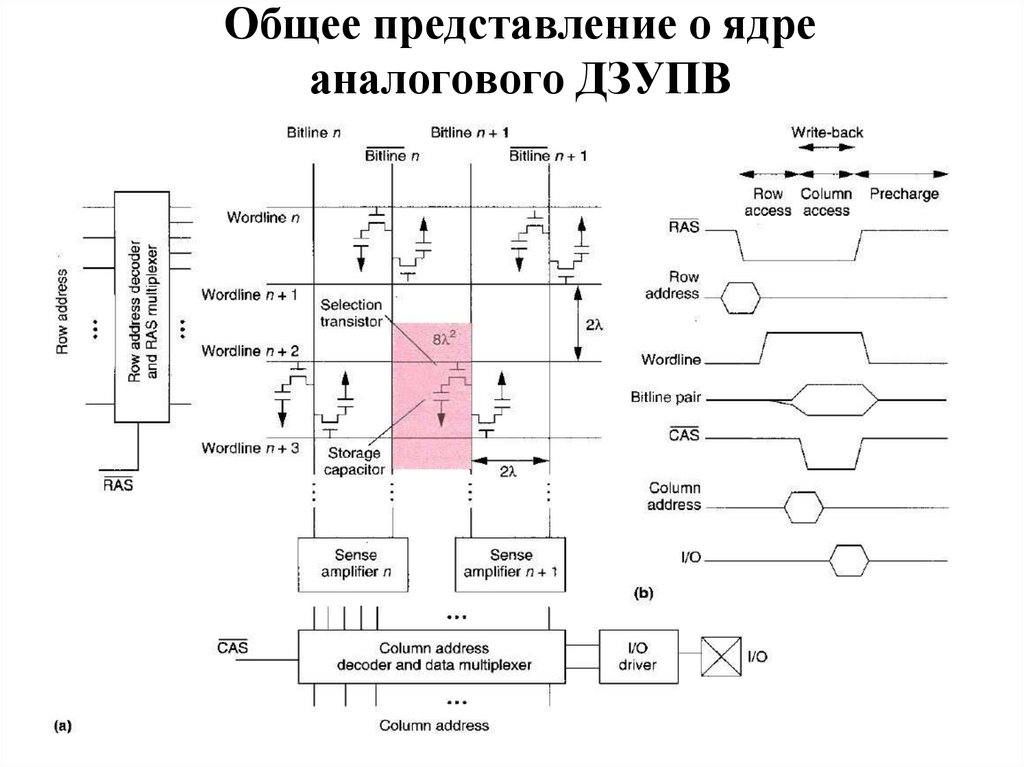

19. Общее представление о ядре аналогового ДЗУПВ

20. Упрощенная временная диаграмма режима чтения из асинхронного ДЗУПВ

21. Блок-схема асинхронного ДЗУВП

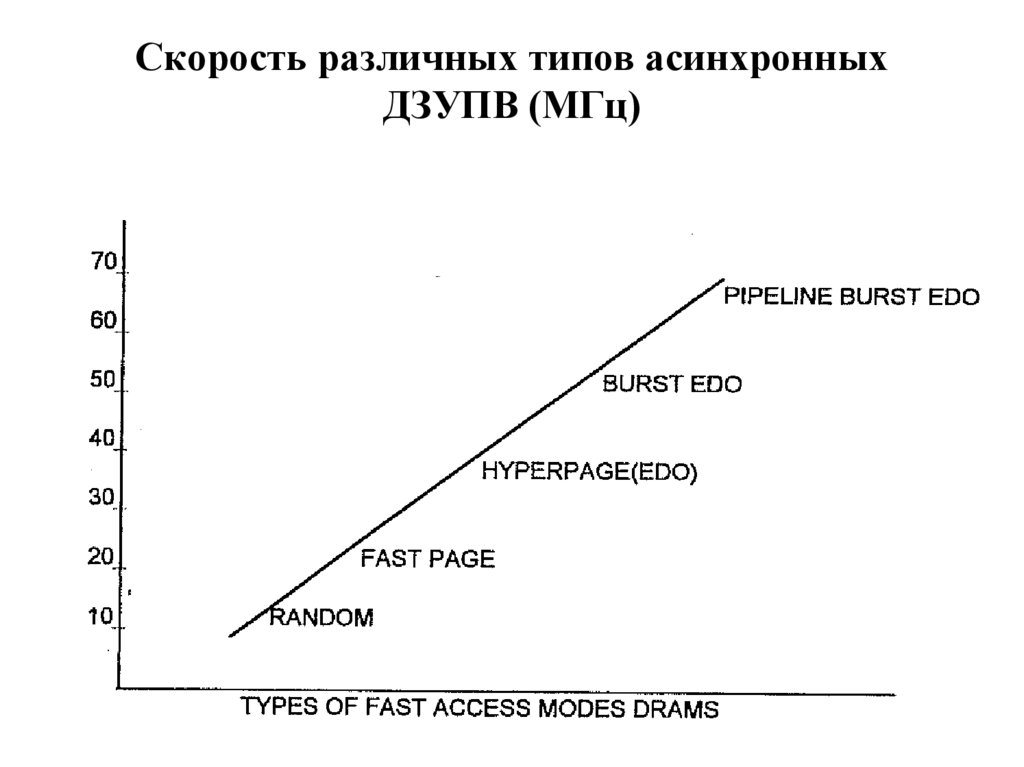

22. Скорость различных типов асинхронных ДЗУПВ (МГц)

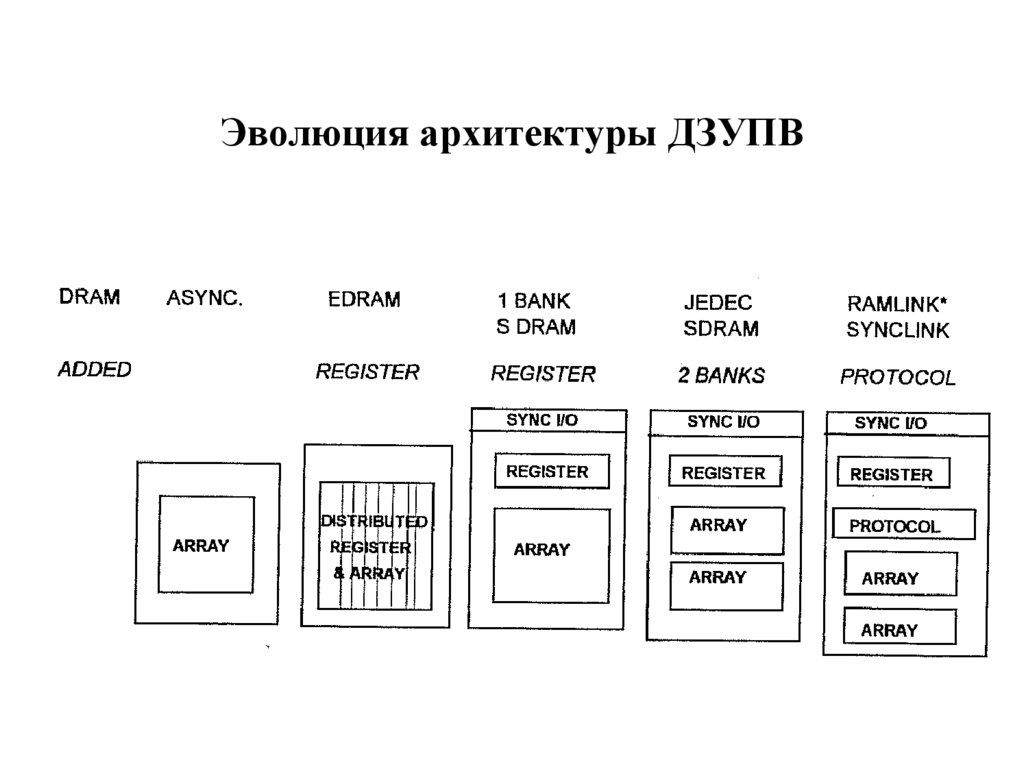

23. Эволюция архитектуры ДЗУПВ

24. Сравнение ДЗУПВ с асинхронным и синхронным управлением

25. Пример внутренней организации DDR3 SDRAM

26. Временные параметры ДЗУПВ

27. Взаимосвязь между тактовой частотой, пропускной способностью и названиями DDR SDRAM и DIMM

СтандартТактовая

частота

Миллионов

пересылок в

секунду

Название

DRAM

MB/sec/DIMM

Название

DIMM

DDR

133

266

DDR266

2128

PC2100

DDR

150

300

DDR300

2400

PC2400

DDR

200

400

DDR400

3200

PC3200

DDR2

266

533

DDR2-533

4264

PC4300

DDR2

333

667

DDR2-667

5336

PC530O

DDR2

400

800

DDR2-800

6400

PC6400

DDR3

533

1066

DDR3-1066

8528

PC8500

DDR3

666

1333

DDR3-1333

10,664

PC 10700

DDR3

800

1600

DDR3-1600

12,800

PC 12800

DDR4

1066-1600

2133-3200

DDR4-3200

17,056-25,600

PC25600

28. Скоростные характеристики DDR

СпецификацияТактовая частота

шины памяти

PC1600*

(DDR200)

Максимальная теоретическая пропускная

способность памяти

в одноканальном

режиме

в двухканальном

режиме

100 МГц

1600 Мбайт/сек

3200 Мбайт/сек

PC2100*

(DDR266)

133 МГц

2133 Мбайт/сек

4267 Мбайт/сек

PC2400

(DDR300)

150 МГц

2400 Мбайт/сек

4800 Мбайт/сек

PC2700*

(DDR333)

166 МГц

2667 Мбайт/сек

5333 Мбайт/сек

PC3200*

(DDR400)

200 МГц

3200 Мбайт/сек

6400 Мбайт/сек

PC3500

(DDR433)

217 МГц

3467 Мбайт/сек

6933 Мбайт/сек

PC3700

(DDR466)

233 МГц

3733 Мбайт/сек

7467 Мбайт/сек

PC4000

(DDR500)

250 МГц

4000 Мбайт/сек

8000 Мбайт/сек

29. Скоростные характеристики DDR2

Название модуляЧастота шины

Тип

Пиковая скорость

передачи данных

PC2-3200

200 МГц

DDR2-400

3200 МБ/с

PC2-4200

266 МГц

DDR2-533

4200 МБ/с

PC2-5300

333 МГц

DDR2-667

5300 МБ/с

PC2-5400

337 МГц

DDR2-675

5400 МБ/с

PC2-5600

350 МГц

DDR2-700

5600 МБ/с

PC2-5700

355 МГц

DDR2-711

5700 МБ/с

PC2-6000

375 МГц

DDR2-750

6000 МБ/с

PC2-6400

400 МГц

DDR2-800

6400 МБ/с

PC2-7100

444 МГц

DDR2-888

7100 МБ/с

PC2-7200

450 МГц

DDR2-900

7200 МБ/с

PC2-8000

500 МГц

DDR2-1000

8000 МБ/с

PC2-8500

533 МГц

DDR2-1066

8500 МБ/с

PC2-9200

575 МГц

DDR2-1150

9200 МБ/с

PC2-9600

600 МГц

DDR2-1200

9600 МБ/с

30. Скоростные характеристики DDR3, DDR4

Стандартное название

Частота

памяти

Время

цикла

Частота

шины

Эффективн

ая частота

Название

модуля

Пиковая

скорость

передачи

данных

DDR3-800

100 МГц

10.00 нс

400 МГц

800 МГц

PC3-6400

6400 МБ/с

DDR3-1066

133 МГц

7.50 нс

533 МГц

1066 МГц

PC3-8500

8533 МБ/с

DDR3-1333

166 МГц

6.00 нс

667 МГц

1333 МГц

PC3-10600

10667 МБ/с

DDR3-1600

200 МГц

5.00 нс

800 МГц

1600 МГц

PC3-12800

12800 МБ/с

DDR3-1866

233 МГц

4.29 нс

933 МГц

1866 МГц

PC3-14900

14930 МБ/с

DDR3-2000

250 МГц

4.00 нс

1000 МГц

2000 МГц

PC3-16000

16000 МБ/с

DDR3-2133

266 МГц

3.75 нс

1066 МГц

2133 МГц

PC3-17000

17066 МБ/с

DDR3-2200

275 МГц

3.64 нс

1100 МГц

2200 МГц

PC3-17600

17600 МБ/с

DDR3-2400

300 МГц

3.33 нс

1200 МГц

2400 МГц

PC3-19200

19200 МБ/с

DDR4-2133

2133 МГц

PC4-17000

17066 МБ/с

DDR4-4266

4266 МГц

PC4-34 128

34 128 МБ/c

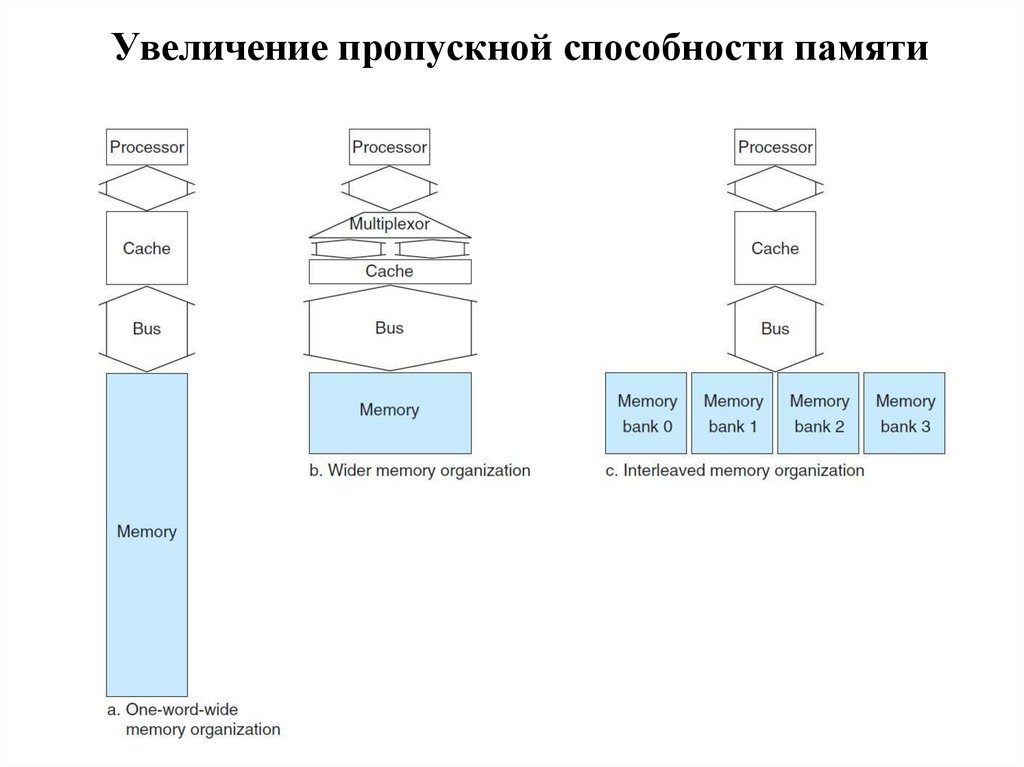

31. Увеличение пропускной способности памяти

• увеличение разрядности• расслоение памяти

32. Увеличение пропускной способности памяти

33. Пример четырехкратного расслоения памяти

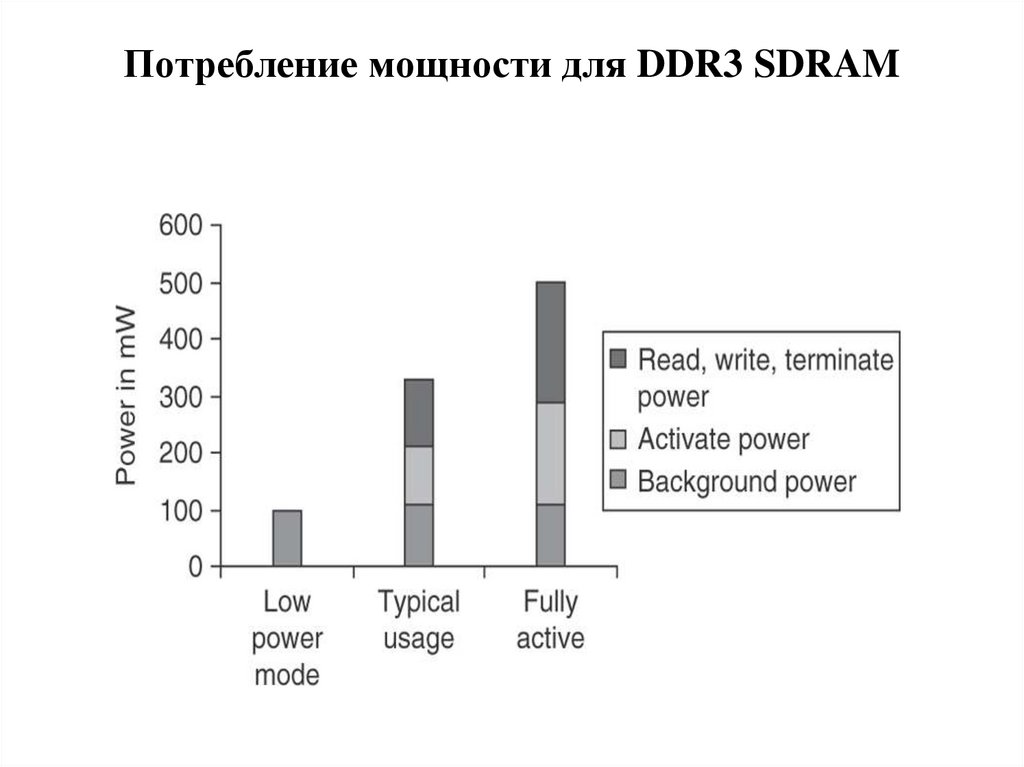

34. Потребление мощности для DDR3 SDRAM

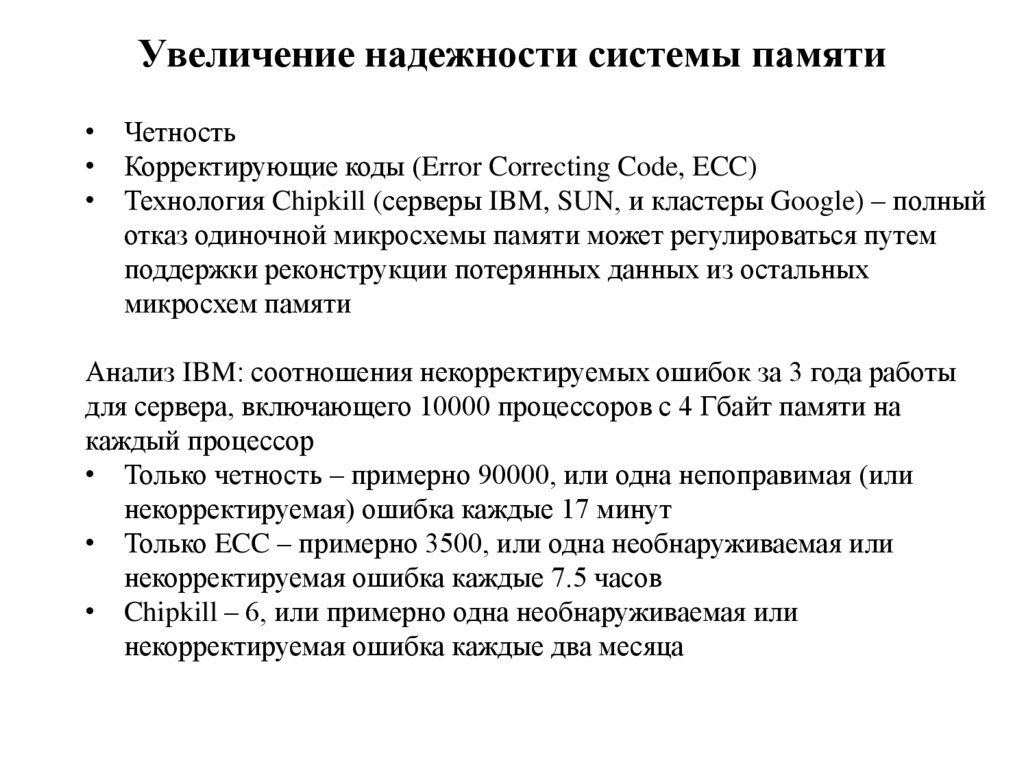

35. Увеличение надежности системы памяти

• Четность• Корректирующие коды (Error Correcting Code, ECC)

• Технология Chipkill (серверы IBM, SUN, и кластеры Google) – полный

отказ одиночной микросхемы памяти может регулироваться путем

поддержки реконструкции потерянных данных из остальных

микросхем памяти

Анализ IBM: соотношения некорректируемых ошибок за 3 года работы

для сервера, включающего 10000 процессоров с 4 Гбайт памяти на

каждый процессор

• Только четность – примерно 90000, или одна непоправимая (или

некорректируемая) ошибка каждые 17 минут

• Только ECC – примерно 3500, или одна необнаруживаемая или

некорректируемая ошибка каждые 7.5 часов

• Chipkill – 6, или примерно одна необнаруживаемая или

некорректируемая ошибка каждые два месяца

36. Защита программ без виртуальной памяти

37. Преобразование виртуальных адресов в физические

38. Страничная организация памяти

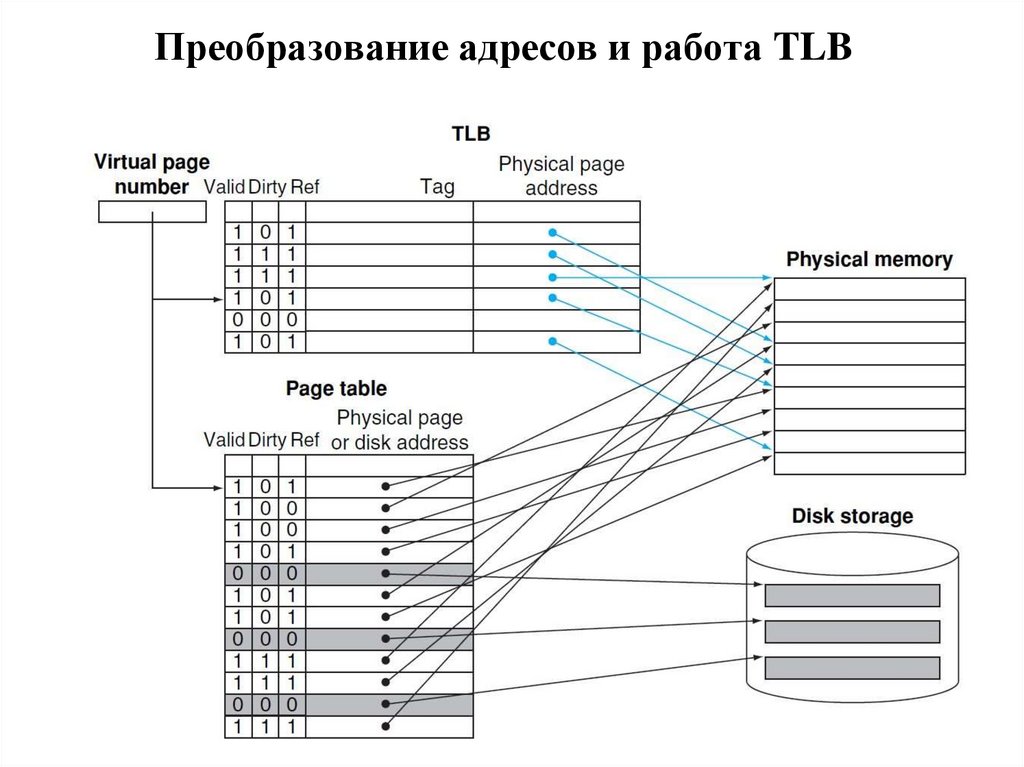

39. Преобразование адресов и работа TLB

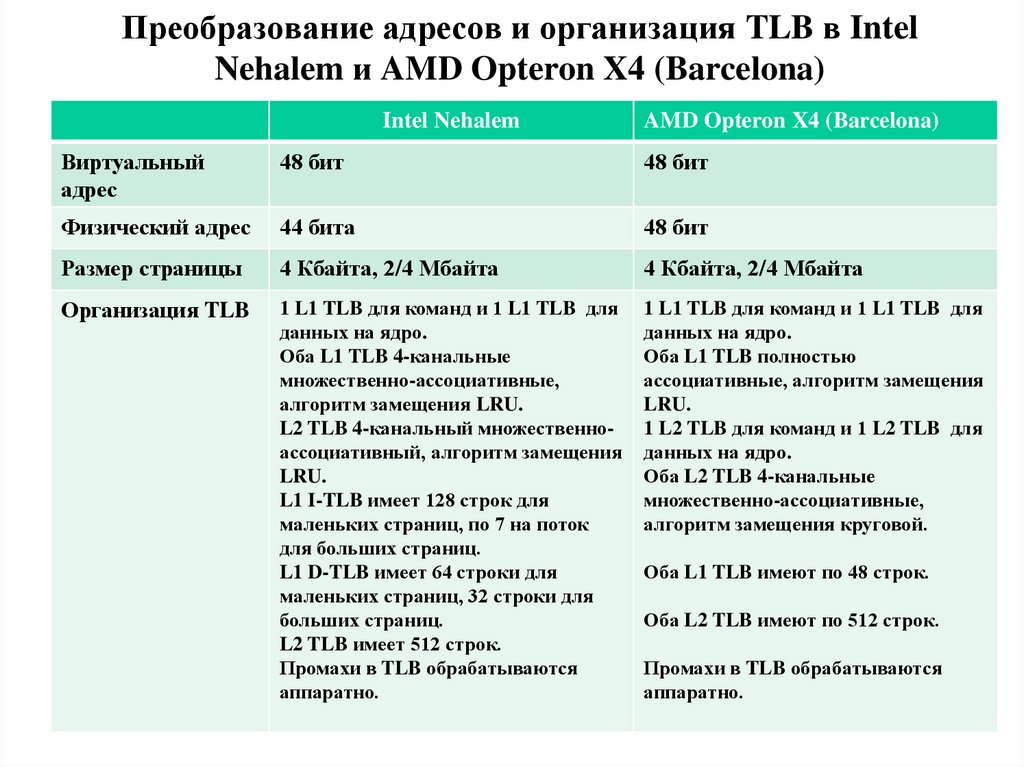

40. Преобразование адресов и организация TLB в Intel Nehalem и AMD Opteron X4 (Barcelona)

Intel NehalemAMD Opteron X4 (Barcelona)

Виртуальный

адрес

48 бит

48 бит

Физический адрес

44 бита

48 бит

Размер страницы

4 Кбайта, 2/4 Мбайта

4 Кбайта, 2/4 Мбайта

Организация TLB

1 L1 TLB для команд и 1 L1 TLB для

данных на ядро.

Оба L1 TLB 4-канальные

множественно-ассоциативные,

алгоритм замещения LRU.

L2 TLB 4-канальный множественноассоциативный, алгоритм замещения

LRU.

L1 I-TLB имеет 128 строк для

маленьких страниц, по 7 на поток

для больших страниц.

L1 D-TLB имеет 64 строки для

маленьких страниц, 32 строки для

больших страниц.

L2 TLB имеет 512 строк.

Промахи в TLB обрабатываются

аппаратно.

1 L1 TLB для команд и 1 L1 TLB для

данных на ядро.

Оба L1 TLB полностью

ассоциативные, алгоритм замещения

LRU.

1 L2 TLB для команд и 1 L2 TLB для

данных на ядро.

Оба L2 TLB 4-канальные

множественно-ассоциативные,

алгоритм замещения круговой.

Оба L1 TLB имеют по 48 строк.

Оба L2 TLB имеют по 512 строк.

Промахи в TLB обрабатываются

аппаратно.

41. Сегментация памяти

НСГ- номер сегментаНСТР - номер страницы

НСЛ - номер слова

БТС - база таблицы

сегментов задачи

ДТС - длина таблицы

сегментов

БТСТР - база таблицы

страниц

ИД - индикаторы режима

доступа

ФНСТР - физический

номер страницы

Н - индикатор наличия

42. Защита с помощью виртуальных машин

Причины популярности:• Все увеличивающаяся важность изоляции и безопасности в

современных системах.

• Недостаточная безопасность и надежность стандартных

операционных систем.

• Разделение одного компьютера между многими

несвязанными пользователями, работающими в центрах

обработки данных и в облаке.

• Существенное увеличение скорости процессоров, которая

делает накладные расходы, связанные с организацией

виртуальных машин более приемлемыми.

43. Термины

Виртуальная машина (VM) - все методы эмуляции, которые предоставляютстандартный программный интерфейс, например, Java VM.

VM обеспечивают полную среду уровня системы на уровне двоичной

архитектуры системы команд.

Программное обеспечение, которое поддерживает виртуальные машины,

называется монитором виртуальных машин (VMM - virtual machine

monitor) или гипервизором; VMM является сердцем технологии

виртуальных машин.

Нижележащая аппаратная платформа называется хостом, и ее ресурсы

разделяются гостевыми виртуальными машинами. VMM определяет, как

отображать виртуальные ресурсы на физические ресурсы. Физический

ресурс может использоваться с разделением времени, разбит на разделы

или даже эмулироваться программными средствами. VMM гораздо

меньше, чем традиционная ОС; часть VMM осуществляющая изоляцию,

возможно содержит всего 10000 строк кода.

44. Другие преимущества

• Управление программным обеспечением – VM предоставляютабстракцию, которая может выполнять полный программный

стек, включая даже старые операционные системы, такие как

DOS.

• Управление аппаратурой – Одной из причин развертывания

множества серверов является желание иметь каждое приложение

работающим со своей собственной совместимой для него версией

операционной системы на разных компьютерах, поскольку такое

разделение может повысить общую надежность. VM позволяют

этим разделенным программным стекам работать независимо и

все же разделять аппаратуру, тем самым консолидируя количество

серверов. Другим примером является то, что некоторые VMM

поддерживают миграцию работающих VM на другой компьютер,

либо для балансировки нагрузки, либо для эвакуации с

отказавшей аппаратуры.

45. Качественные требования к VMM

• Поведение гостевого программного обеспечения на VM должно бытьточно таким же, как если бы оно выполнялось на родной аппаратуре, за

исключением поведения, связанного с производительностью, или

ограничений фиксированных ресурсов, разделяемых несколькими VM

• Гостевое программное обеспечение не должно иметь возможность

изменять распределение ресурсов реальной системы непосредственно.

Требования:

• По крайней мере два режима работы процессора, системный и

пользовательский.

• Поднабор привилегированных команд, которые доступны только в

системном режиме, приводящие к прерыванию, если выполняются в

режиме пользователя. Все системные ресурсы должны контролироваться

только с помощью этих команд.

electronics

electronics