Similar presentations:

PDF-XCyange Editor DEMO

1.

4Ed

e

g

n

ha

D

r

o

it

2

2

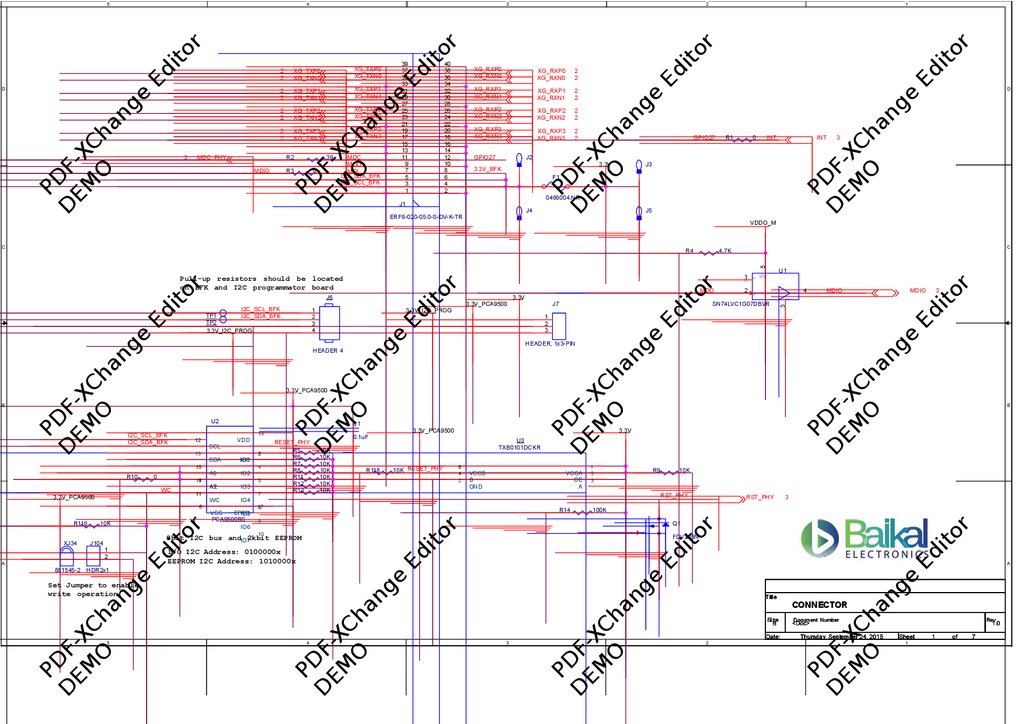

XG_TXP0

XG_TXN0

XG_TXP0

XG_TXN0

2

2

XG_TXP1

XG_TXN1

XG_TXP1

XG_TXN1

2

2

XG_TXP2

XG_TXN2

XG_TXP2

XG_TXN2

XG_TXP3

XG_TXN3

XG_TXP3

XG_TXN3

2

2

XC

F O

D

P EM

D

3

3

MDC_PHY

R2

MDIO

R3

39

37

35

33

31

29

27

25

23

21

19

17

15

13

11

9

7

5

3

1

e

g

n

ha

XC

F O

D

P EM

D

39

0

MDC

MDO

MDI

I2C_SDA_BFK

I2C_SCL_BFK

Ed

r

o

it

40

38

36

34

32

30

28

26

24

22

20

18

16

14

12

10

8

6

4

2

2

XG_RXP0

XG_RXN0

XG_RXP0

XG_RXN0

2

2

XG_RXP1

XG_RXN1

XG_RXP1

XG_RXN1

2

2

XG_RXP2

XG_RXN2

XG_RXP2

XG_RXN2

2

2

XG_RXP3

XG_RXN3

XG_RXP3

XG_RXN3

2

2

GPIO27

J2

e

g

n

ha

XC

F O

D

P EM

D

3.3V

3.3V_BFK

F1

Ed

1

r

o

it

GPIO27

R1

J3

J4

ERF8-020-05.0-S-DV-K-TR

J5

VDDO_M

C

r

Pull-up resistors should be located

on BFK and I2C programmator board

Ed

e

g

n

a

h

B

XC

F O

D

P EM

D

I2C_SCL_BFK

TP1

I2C_SDA_BFK

TP2

3.3V_I2C_PROG

12

13

0

16

1

WC

11

3.3V_PCA9500

6

A

881545-2

10K

J104

it

or

e

g

n

a

h

XC

F O

D

P EM

D

3.3V_PCA9500

I2C_SCL_BFK

I2C_SDA_BFK

e

g

n

a

h

HDR2x1

Ed

14

SCL

SDA

IO1

IO0

A0

IO2

A1

A2

IO3

WC

IO4

VSS

EPAD

IO5

PCA9500BS

IO6

2

3

4

5

7

RESET_PHY

R5

R6

R7

R8

R11

R12

R13

5

J7

1

2

3

10K

10K

10K

10K

10K

10K

10K

R118

10K RESET_PHY

r

e

g

n

a

h

XC

F O

D

P EM

D

Ed

it

1

2

NC

U1

VCC

Y

A

SN74LVC1G07DBVR

4

6

4

2

VCCB

B

GND

XC

F O

D

P EM

D

VCCA

OE

A

1

5

3

R9

R14

or

3

Ed

i to

r

B

10K

Q1

RST_PHY

i to

FDV305N

e

g

n

a

h

3

MDIO

XC

F O

D

P EM

D

100K

XC

F O

D

P EM

D

MDIO

GND

e

g

n

a

h

RST_PHY

10

4

Ed

3

C

3.3V

U3

TXB0101DCKR

9

I/O I2C Address: 0100000x

EEPROM I2C Address: 1010000x

e

g

n

a

h

HEADER, 1x3-PIN

3.3V_PCA9500

0.1uF

i to

MDO

3.3V

3.3V_PCA9500

17

8

Set Jumper to enable

write operation

XC

F O

D

P EM

D

r

C1

VDD

8bit I2C bus andIO72kbit EEPROM

1

2

Ed

i to

3.3V_I2C_PROG

HEADER 4

15

XJ34

1

2

3

4

U2

R10

R116

J6

D

4.7K

5

R4

i to

INT

0466004.NR

J1

Ed

r

o

it

XC

F O

D

P EM

D

INT

0

e

g

n

ha

3

5

Ed

3

r

Title

CONNECTOR

Size

B

Date:

2

XC

F O

D

P EM

D

Document Number

<Doc>

e

g

n

a

h

Thursday, September 24, 2015

Sheet

1

Ed

i to

r

A

Rev

1.0

1

of

7

2.

54

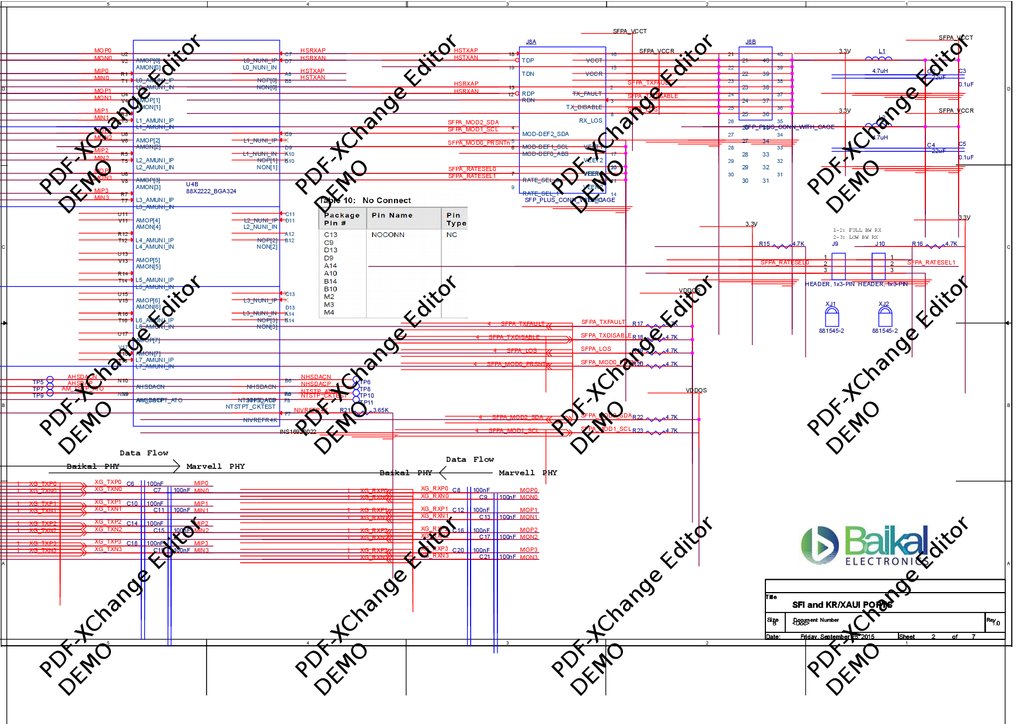

MOP0

MON0

U2

V2

MIP0

MIN0

R1

T1

MOP1

MON1

U4

V4

MIP1

MIN1

R3

T3

MOP2

MON2

XC

F O

D

P EM

D

U6

V6

MIP2

MIN2

R5

T5

MOP3

MON3

U8

V8

MIP3

MIN3

R7

T7

U11

V11

R12

T12

C

U13

V13

R14

T14

U15

V15

R16

T16

V17

R18

T18

TP5

TP7

TP9

B

XC

F O

D

P EM

D

AHSDACN

AHSDAP

AM_TSTP_ATO

N10

N11

N9

AMOP[2]

AMON[2]

L1_NUNI_IP

L1_NUNI_IN

NOP[1]

NON[1]

L2_AMUNI_IP

L2_AMUNI_IN

AMOP[3]

AMON[3]

D9

A10

B10

L3_AMUNI_IP

L3_AMUNI_IN

AMOP[4]

AMON[4]

L2_NUNI_IP

L2_NUNI_IN

L4_AMUNI_IP

L4_AMUNI_IN

AMOP[5]

AMON[5]

NOP[2]

NON[2]

e

g

n

ha

C11

D11

i

d

E

t

L5_AMUNI_IP

L5_AMUNI_IN

AMOP[6]

AMON[6]

Ed

r

ti o

L6_AMUNI_IP

L6_AMUNI_IN

J8A

HSTXAP

HSTXAN

18

19

HSRXAP

HSRXAN

13

12

TDP

VCCT

TDN

VCCR

RDP

RDN

TX_FAULT

TX_DISABLE

RX_LOS

4

SFPA_MOD0_PRSNTn 5

6

7

9

2

3

8

Ed

r

o

it

VEET1

VEER1

VEET3

VEER2

1

22

23

SFPA_TXDISABLE

24

SFPA_LOS

25

e

g

n

ha

26

27

28

17

29

10

20

30

11

21

40

22

39

23

38

24

37

25

36

3.3V

40

39

37

36

3.3V

28

33

29

32

30

31

L3_NUNI_IP

L3_NUNI_IN

NOP[3]

NON[3]

NHSDACN

AHSDACP

AM_TSTPT_ATO

NTSTPT_ATO

NHSDACP

NTSTPT_CKTEST

XC

F O

D

P EM

D

34

NIVREFR4K

F7

32

31

RATE_SEL_1

14

SFP_PLUS_CONN_WITH_CAGE

VEER3

e

g

n

a

h

Ed

NIVREFR4K

R21

4

4

XG_TXP0 C6

XG_TXN0

100nF

C7

MIP0

100nF MIN0

1

1

XG_TXP1

XG_TXN1

XG_TXP1 C10

XG_TXN1

100nF

C11

MIP1

100nF MIN1

1

1

XG_TXP2

XG_TXN2

XG_TXP2 C14

XG_TXN2

100nF

C15

MIP2

100nF MIN2

1

1

XG_TXP3

XG_TXN3

XG_TXP3 C18

XG_TXN3

100nF

C19

MIP3

100nF MIN3

Ed

i to

SFPA_TXDISABLE

4

4

4

SFPA_MOD2_SDA

SFPA_MOD1_SCL

Data Flow

D

SFPA_VCCR

C5

C4

22uF

0.1uF

3.3V

4.7K

J9

XG_RXP0

XG_RXN0

100nF

C9

MOP0

100nF MON0

XG_RXP1

XG_RXN1

XG_RXP1 C12

XG_RXN1

100nF

C13

MOP1

100nF MON1

1

1

XG_RXP2

XG_RXN2

XG_RXP2 C16

XG_RXN2

100nF

C17

MOP2

100nF MON2

1

1

XG_RXP3

XG_RXN3

100nF

C21

MOP3

100nF MON3

1

1

e

g

n

a

h

XC

F O

D

P EM

D

Ed

SFPA_TXFAULT

R17

e

g

n

a

h

Ed

4.7K

SFPA_LOS

R19

4.7K

SFPA_MOD0_PRSNTn

R20

4.7K

XC

F O

D

P EM

D

4.7K

SFPA_MOD1_SCL R23

4.7K

4.7K

XJ1

XJ2

881545-2

881545-2

C

SFPA_RATESEL1

e

g

n

a

h

Ed

i to

r

XC

F O

D

P EM

D

VDDOS

SFPA_MOD2_SDA R22

R16

1

2

3

HEADER, 1x3-PIN HEADER, 1x3-PIN

4.7K

SFPA_TXDISABLE R18

J10

1

2

3

B

Marvell PHY

XG_RXP0 C8

XG_RXN0

1

1

4

SFPA_LOS

SFPA_MOD0_PRSNTn

Baikal PHY

r

SFPA_TXFAULT

TP6

TP8

TP10

TP11

3.65K

Marvell PHY

r

ti o

VDDOS

4

XC

F O

D

P EM

D

NHSDACN

NHSDACP

NTSTP_ATO

NTSTP_CKTEST

r

ti o

INS16920022

Data Flow

0.1uF

4.7uH

33

R15

D13

A14

B14

E6

A6

F8

e

g

n

ha

1-2: FULL BW RX

2-3: LOW BW RX

AMON[7]

L7_AMUNI_IP

L7_AMUNI_IN

AHSDACN

C3

3.3V

C13

B6

Ed

C2

22uF

L2

35

34

L1

4.7uH

38

SFP_PLUS_CONN_WITH_CAGE

26

35

27

r

o

it

SFPA_VCCT

J8B

21

SFPA_TXFAULT

XC

F O

D

P EM

D

MOD-DEF1_SCL

MOD-DEF0_ABS

RATE_SEL_0

SFPA_VCCR

15

MOD-DEF2_SDA

VEET2

SFPA_RATESEL0

SFPA_RATESEL1

16

1

A12

B12

AMOP[7]

e

g

n

a

h

SFPA_VCCT

or

SFPA_MOD2_SDA

SFPA_MOD1_SCL

XC

F O

D

P EM

D

2

SFPA_RATESEL0

XG_TXP0

XG_TXN0

5

C9

U4B

88X2222_BGA324

1

1

XC

F O

D

P EM

D

HSTXAP

HSTXAN

A8

B8

L1_AMUNI_IP

L1_AMUNI_IN

Baikal PHY

A

NOP[0]

NON[0]

HSRXAP

HSRXAN

C7

D7

AMOP[1]

AMON[1]

e

g

n

a

h

U17

t

L0_NUNI_IP

L0_NUNI_IN

L0_AMUNI_IP

L0_AMUNI_IN

e

g

n

ha

D

i

d

E

AMOP[0]

AMON[0]

or

3

i to

r

XG_RXP3 C20

XG_RXN3

e

g

n

a

h

3

XC

F O

D

P EM

D

Ed

i to

r

Title

e

g

n

a

h

Ed

i to

r

A

SFI and KR/XAUI PORTS

Size

B

Date:

2

XC

F O

D

P EM

D

Document Number

<Doc>

Friday, September 25, 2015

Sheet

1

Rev

1.0

2

of

7

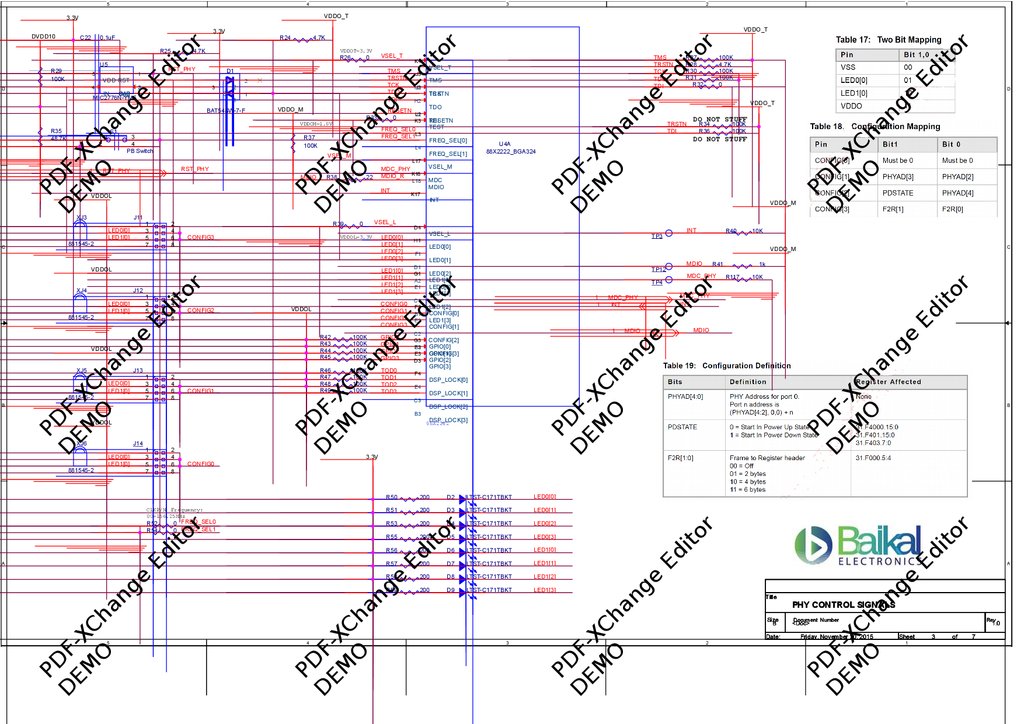

3.

54

3

DVDD10

C22

0.1uF

R25

U5

R29

100K

5

e

g

n

ha

IN

MR

Gnd

MIC2776N-YM5

R35

48.7K

S1

XC

F O

D

P EM

D

1

2

1

i

d

E

t

3.3V

or

3

2

VDDOT=3.3V

3

2

VDDO_M

R33

XC

F O

D

P EM

D

R37

100K

1

3

5

7

2

4

6

8

LED0[0]

LED1[0]

1

3

5

7

e

g

n

a

h

2

4

6

8

Ed

it

XC

F O

D

P EM

D

881545-2

B

J13

LED0[0]

LED1[0]

1

3

5

7

2

4

6

8

CONFIG2

CONFIG1

881545-2

A

LED0[0]

LED1[0]

J14

1

3

5

7

5

K3

L4

L18

INT

VSEL_L

VDDOL

LED0[0]

LED0[1]

LED0[2]

LED0[3]

K17

D4

H1

F1

LED1[0]

LED1[1]

LED1[2]

LED1[3]

D1

G1

A2

E1

CONFIG0

CONFIG1

CONFIG2

CONFIG3

C1

F2

B1

E2

e

g

n

a

h

R42

R43

R44

R45

100K

100K

100K

100K

GPIO0

GPIO1

GPIO2

GPIO3

R46

R47

R48

R49

100K

100K

100K

100K

TOD0

TOD1

TOD2

TOD3

F4

E4

C3

B3

TMS

TDO

RESETN

TDI

TEST

FREQ_SEL[0]

FREQ_SEL[1]

U4A

88X2222_BGA324

VSEL_M

MDC

MDIO

INT

1

TP12

or

LED0[2]

LED1[0]

LED0[3]

LED1[1]

it

1

1

LED1[2]

CONFIG[0]

LED1[3]

CONFIG[1]

DSP_LOCK[1]

DSP_LOCK[2]

DSP_LOCK[3]

88X2222

LTST-C171TBKT

LED0[0]

D3

LTST-C171TBKT

LED0[1]

R52

R54

R53

200

D4

LTST-C171TBKT

LED0[2]

R55

200

D5

LTST-C171TBKT

LED0[3]

R57

e

g

n

a

h

R58

R59

XC

F O

D

P EM

D

4

DO NOT STUFF

TRSTN

TDI

R34

R36

100K

100K

INT

R40

Ed

D6

LTST-C171TBKT

LED1[0]

200

D7

LTST-C171TBKT

LED1[1]

200

D8

LTST-C171TBKT

LED1[2]

200

D9

LTST-C171TBKT

LED1[3]

200

Ed

r

o

it

D

XC

F O

D

P EM

D

DO NOT STUFF

10K

MDIO

e

g

n

a

h

MDIO

R41

C

or

MDC_PHY

it

1k

R117

10K

MDC_PHY

INT

Ed

e

g

n

a

h

MDIO

XC

F O

D

P EM

D

DSP_LOCK[0]

it

MDC_PHY

INT

1

CONFIG[2]

GPIO[0]

GPIO[1]

CONFIG[3]

GPIO[2]

GPIO[3]

or

e

g

n

ha

VDDO_T

TP4

D2

R56

100K

4.7K

100K

100K

0

VDDO_M

LED0[1]

200

Ed

R27

R28

R30

R31

R32

VDDO_T

LED0[0]

200

it

t

or

VDDO_M

TP3

R51

or

XC

F O

D

P EM

D

VSEL_L

R50

0 FREQ_SEL0

0 FREQ_SEL1

e

g

n

ha

TCK

TRSTN

3.3V

CONFIG0

i

d

E

TMS

TRSTN

TCK

TDO

TDI

VSEL_T

Ed

C2

G3

F3

B2

E3

D3

t

or

CLKP/N Frequency:

00=156.25MHz

e

g

n

a

h

XC

F O

D

P EM

D

2

4

6

8

H2

MDC_PHY

MDIO_R K18

VDDOL=3.3V

XC

F O

D

P EM

D

J2

H3

L17

or

VDDOL

XJ6

0

J3

FREQ_SEL0

FREQ_SEL1L3

22

R39

CONFIG3

VDDOL

XJ5

R38

i

d

E

K4

RESETN

L2

J1

0

VSEL_M

MDIO

J12

e

g

n

ha

1

VDDOM=1.8V

VDDOL

881545-2

TMS

TRSTN

TCK

TDO

TDI

2

BAT54SW-7-F

RST_PHY

LED0[0]

LED1[0]

XJ4

3

1

RST_PHY

J11

VSEL_T

0

D1

VDDOL

881545-2

4.7K

R26

3

4

PB Switch

XJ3

R24

4.7K

RST_PHY

1

VDD RST

4

D

C

2

VDDO_T

3.3V

3

e

g

n

a

h

XC

F O

D

P EM

D

Ed

i to

r

XC

F O

D

P EM

D

Ed

i to

B

r

Title

e

g

n

a

h

Ed

i to

r

A

PHY CONTROL SIGNALS

Size

B

Date:

2

XC

F O

D

P EM

D

Document Number

<Doc>

Friday, November 20, 2015

Sheet

1

Rev

1.0

3

of

7

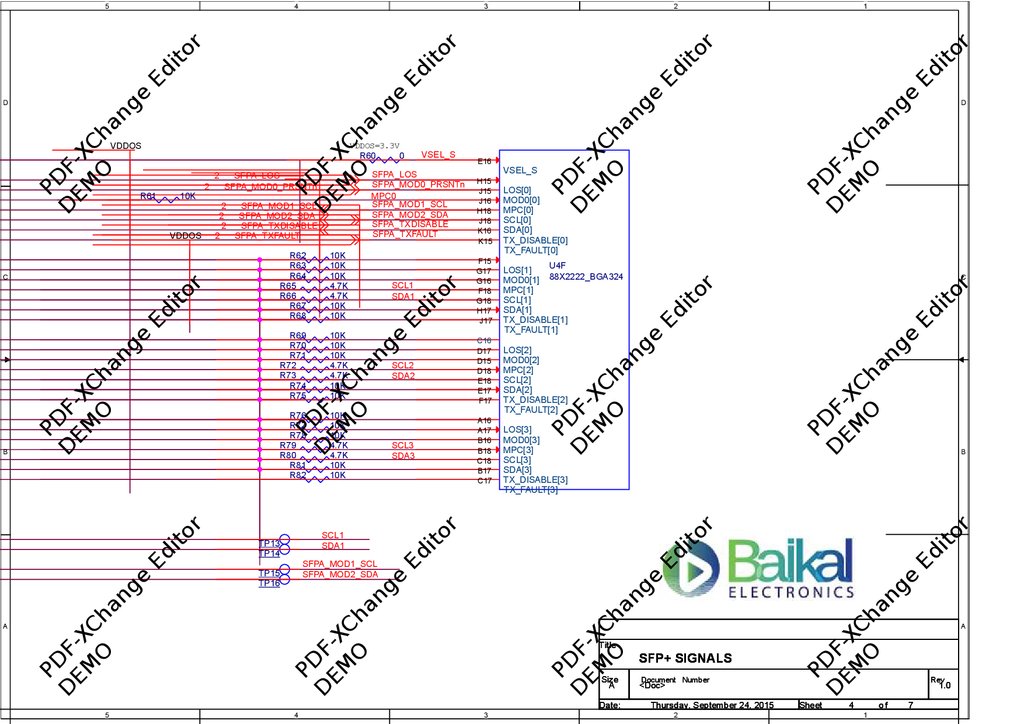

4.

5D

e

g

n

ha

4

Ed

C VDDOS

X

F- O

PD EM

R61

D

r

o

it

e

g

n

ha

10K

C

A

Ed

it

or

XC

F O

D

P EM

D

e

g

n

a

h

2

SFPA_TXDISABLE

SFPA_TXFAULT

SFPA_TXDISABLE

SFPA_TXFAULT

R62

R63

R64

R65

R66

R67

R68

10K

10K

10K

4.7K

4.7K

10K

10K

R69

R70

R71

R72

R73

R74

R75

10K

10K

10K

4.7K

4.7K

10K

10K

SCL1

SDA1

Ed

R81

R82

Ed

i to

r

10K

10K

SFPA_MOD1_SCL

SFPA_MOD2_SDA

e

g

n

a

h

TP15

TP16

Ed

E16

H15

J15

J16

H18

J18

K16

K15

F15

G17

G16

F18

G18

H17

J17

C16

D17

D15

D18

E18

E17

F17

A16

A17

B16

B18

C18

B17

C17

SCL3

SDA3

SCL1

SDA1

TP13

TP14

it

or

e

g

n SCL2

a

h SDA2

XC

F10K O

R76

R77 D 10K

R78P

10KM

E

R79

D4.7K

R80

4.7K

XC

F O

D

P EM

D

5

e

g

n

ha

VDDOS=3.3V

2

B

Ed

2

r

o

it

XCR60 0 VSEL_S

F O SFPA_LOS

2

SFPA_LOS

SFPA_MOD0_PRSNTn

2

SFPA_MOD0_PRSNTnD

P EM MPC0

SFPA_MOD1_SCL

2

SFPA_MOD1_SCL

SFPA_MOD2_SDA

2

SFPA_MOD2_SDA D

VDDOS

e

g

n

a

h

3

i to

e

g

n

ha

U4F

LOS[1]

MOD0[1] 88X2222_BGA324

MPC[1]

SCL[1]

SDA[1]

TX_DISABLE[1]

TX_FAULT[1]

LOS[2]

MOD0[2]

MPC[2]

SCL[2]

SDA[2]

TX_DISABLE[2]

TX_FAULT[2]

e

g

n

a

h

Ed

it

or

D

Ed

i to

XC

F O

D

P EM

D

LOS[3]

MOD0[3]

MPC[3]

SCL[3]

SDA[3]

TX_DISABLE[3]

TX_FAULT[3]

Ed

i to

Document Number

<Doc>

Thursday, September 24, 2015

2

B

r

SFP+ SIGNALS

r

C

e

g

n

a

h

XC

F O

D

P EM

D

XTitleC

F O

D

P EM

Size

A

D Date:

Ed

r

o

it

XC

F O

D

P EM

D

LOS[0]

MOD0[0]

MPC[0]

SCL[0]

SDA[0]

TX_DISABLE[0]

TX_FAULT[0]

e

g

n

a

h

3

r

o

it

XC

F O

D

P EM

D

r

XC

F O

D

P EM

D

4

VSEL_S

Ed

1

e

g

n

a

h

XC

F O

D

P EM

D4 of

Sheet

1

Ed

i to

A

Rev

1.0

7

r

5.

54

3

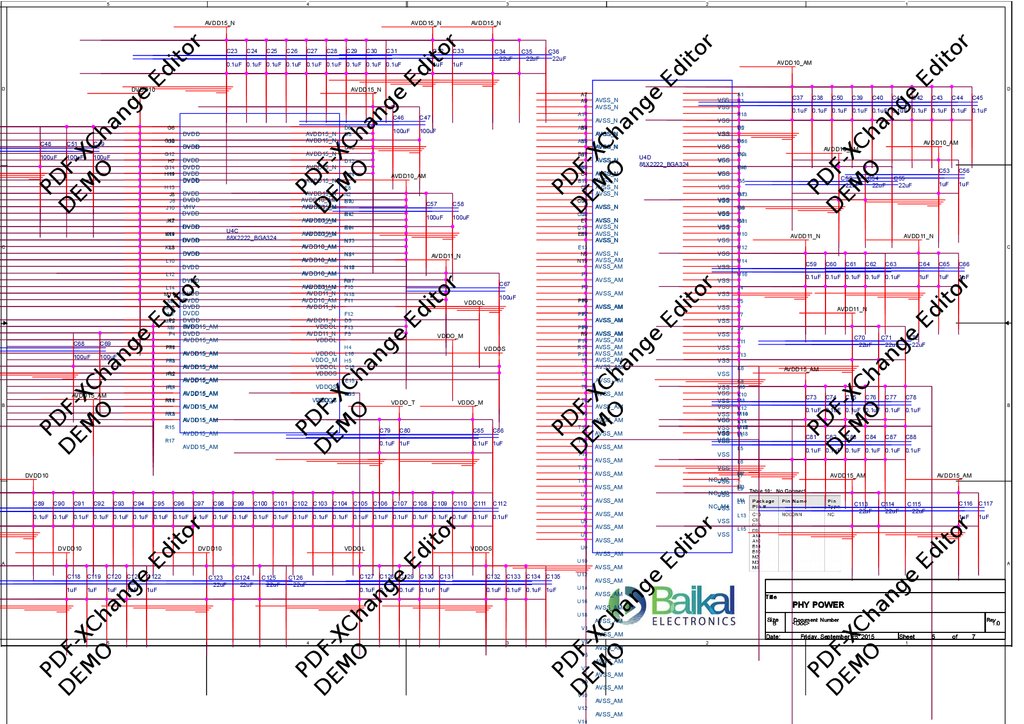

AVDD15_N

e

g

n

ha

DVDD10

D

Ed

C51

C49

100uF

100uF

100uF

G10

G8

G12

H7

G14

H11

H9

H13

J8

J6

J10

K7

J12

K11

K9

J14

C

K13

L8

L10

L12

L14

M11

M5

M13

M7

P2

M15

M9

P4

Ed

e

g

n

a

h

C68

C69

100uF

100uF

P11

P6

P13

P8

R2

P15

XC

F O

D

P EM

D

R4

P17

AVDD15_AM

B

C23

C24

C25

C26

C27

C28

C29

C30

C31

0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

e

g

n

ha

AVDD15_N

Ed

R11

R6

R13

R8

R15

R17

DVDD

AVDD15_N

AVDD15_N

AVDD15_N

DVDD

DVDD

DVDD

DVDD

AVDD15_N

AVDD15_N

DVDD

DVDD

VHV

DVDD

AVDD15_N

AVDD10_AM

AVDD10_AM

AVDD15_N

AVDD10_AM

AVDD15_N

DVDD

U4C

88X2222_BGA324

DVDD

AVDD10_AM

AVDD15_N

AVDD10_AM

DVDD

AVDD10_AM

DVDD

or

AVDD10_AM

DVDD

AVDD11_N

AVDD10_AM

AVDD11_N

AVDD10_AM

AVDD11_N

DVDD

DVDD

DVDD

DVDD

DVDD

AVDD15_AM

DVDD

DVDD

AVDD15_AM

AVDD11_N

VDDOL

AVDD11_N

VDDOL

AVDD15_AM

VDDOL

VDDO_M

VDDOL

VDDOS

AVDD15_AM

D10

VDDOS

AVDD15_AM

VDDO_T

VDDOS

AVDD15_AM

AVDD15_AM

AVDD15_AM

AVDD15_AM

C33

C34

22uF

1uF

C35

22uF

C36

22uF

A7

A9

A11

C47

A13

B4

100uF

B11

B7

D14

B13

B9

C4

B15

C5

AVDD10_AM

E8

N2

N3

E10

N4

E12

C10

C6

C57

C58

100uF

100uF

C12

C8

E7

C14

E11

E9

N6

E14

N13

N7

N14

N8

N16

N12

F12

D5

F13

F5

H4

L16

H5

C15

E15

E13

N5

N15

AVDD11_N

F9

N17

F10

N18

F11

e

g

n

a

h

Ed

it

or

P1

C67

100uF

VDDOL

P3

P10

P5

P12

P7

P14

P9

R9

P16

R10

P18

T2

VDDO_M

VDDOS

T4

K5

G15

T8

VDDO_M

T9

C79

C80

C85

0.1uF 1uF

T10

C86

T11

0.1uF 1uF

T13

T15

DVDD10

T17

U1

C89

C90

C91

C92

C93

C94

C95

C96

C97

C98

C99

C100 C101 C102 C103 C104 C105 C106 C107 C108 C109 C110

or

or

C111

C112

0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

DVDD10

A

e

g

n

a

h

Ed

C118

C119 C120 C121 C122

1uF

1uF

1uF

XC

F O

D

P EM

D

5

1uF

1uF

it

DVDD10

C123

22uF

VDDOL

C124

22uF

C125

22uF

C126

22uF

e

g

n

a

h

U5

U7

U9

VDDOS

U10

C127 C128 C129 C130 C131

C132 C133 C134 C135

U12

0.1uF 0.1uF 0.1uF 0.1uF 1uF

0.1uF 0.1uF 0.1uF 1uF

U14

XC

F O

D

P EM

D

4

Ed

it

U3

U16

U18

AVSS_N

VSS

AVSS_N

VSS

AVSS_N

AVSS_N

VSS

U4D

88X2222_BGA324

VSS

AVSS_N

AVSS_N

AVSS_N

AVSS_N

VSS

VSS

VSS

AVSS_N

VSS

AVSS_N

AVSS_N

AVSS_N

AVSS_N

VSS

VSS

AVSS_N

AVSS_AM

AVSS_AM

VSS

AVSS_AM

AVSS_AM

AVSS_AM

AVSS_AM

e

g

n

a

h

AVSS_AM

AVSS_AM

AVSS_AM

AVSS_AM

AVSS_AM

AVSS_AM

Ed

it

or

VSS

3

V3

V5

V7

V9

V10

V12

V14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AVSS_AM

AVSS_AM

VSS

AVSS_AM

VSS

AVSS_AM

NC_M2

VSS

AVSS_AM

NC_M3

VSS

AVSS_AM

NC_M4

VSS

AVSS_AM

AVSS_AM

e

g

n

a

h

VSS

VSS

AVSS_AM

AVSS_AM

VSS

VSS

AVSS_AM

AVSS_AM

VSS

VSS

AVSS_AM

AVSS_AM

VSS

VSS

AVSS_AM

Ed

it

or

VSS

VSS

A1

A3

C37

C38

C50

AVSS_AM

XC

F O

D

P EM

D

F6

D16

AVDD10_AM

G2

F14

G4

F16

C52

22uF

G5

G13

G7

H6

G9

H8

G11

H10

AVSS_AM

C44

C45

AVDD10_AM

C53

C56

1uF

1uF

C64

C65

C66

1uF

1uF

1uF

C

H16

0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

C60

C61

C62

C63

J4

J5

AVDD11_N

J7

e

g

n

a

h

J9

C70

22uF

J11

J13

K6

AVDD15_AM

K8

M6

K10

M8

K12

M10

M14

K14

M17

M12

M16

M18

L1

C73

C71

22uF

XC

F O

D

P EM

D

C74

C75

C76

C77

Ed

i to

r

C72

22uF

C78

B

0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

C81

L5

C82

C83

C84

C87

C88

0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

L6

M2

L7

AVDD15_AM

AVDD15_AM

M3

L9

M4

L11

C113

22uF

L13

C114

22uF

C116

C115

22uF

PHY POWER

XC

F O

D

P EM

D

Document Number

<Doc>

e

g

n

a

h

Friday, September 25, 2015

Sheet

1

r

1uF

L15

Date:

AVSS_AM

D

C43

AVDD11_N

C59

AVSS_AM

AVSS_AM

C42

C55

22uF

H14

Size

B

AVSS_AM

C54

22uF

AVDD11_N

AVSS_AM

AVSS_AM

C41

H12

Title

2

C40

Ed

r

o

it

0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

A18

AVSS_AM

AVSS_AM

e

g

n

ha

C39

E5

D2

AVSS_AM

XC

F O

D

P EM

D

V1

AVDD10_AM

VSS

VSS

XC

F O

D

P EM

D

T6

VDDO_T

e

g

n

ha

Ed

r

o

it

AVSS_N

AVSS_N

XC

F O

D

P EM

D

A15

B5

D12

XC

F O

D

P EM

D

AVDD15_AM

r

o

it

1uF

100uF

XC

F O

D

P EM

D

DVDD

it

D6

D8

1

AVDD15_N

C32

C46

G6

XC

F O

D

P EM

D

C48

r

o

it

AVDD15_N

2

Ed

i to

C117

1uF

A

Rev

1.0

5

of

7

6.

5D

4

e

g

n

ha

Ed

3

r

o

it

e

g

n

ha CLKP

CLKP

CLKN

XC

F O

D

P EM

D

r

o

it

XC

59 WAN_CLKN

F O

59 WAN_CLKP

D

P EM

D

A5

A4

CLKN

1

Ed

100, 1%

r

o

it

R83

M1

N1

R85

R86

Ed

2

U4E

88X2222_BGA324

RCLK0

RCLK1

RUNI_WAN_REF_CLKN

RUNI_WAN_REF_CLKP

e

g

RCLK0

RCLK1

an

h

C

X100,

R84

F O1%

PD EM

D

3.3V_CLK

K1

3.3V_CLK

B

A

R91

4.7K

6

1

0.01uF

0.1uF

e

g

n

a

hOUT(+)

Ed

it

Ed

i to

DNP

82

R90

R92

5

3

2

or

r

e

g

n

a

h

Ed

R93

R94

147

147

i to

49.9

C138 0.01uF

e

g

n

a

h

XC

F O

D

P EM

D

Ed

or

DNP

CLKP

R95

R96

127

127

XTitleC

F O

D

P EM

Size

A

D Date:

Ed

i to

DNP

Document Number

<Doc>

Friday, September 25, 2015

2

e

g

n

a

h

Ed

i to

XC

F O

D

P EM

D

B

r

CLOCK

r

C

82

CLKN

DNP

e

g

n

a

h

3

it

R88

C139 0.01uF

r

XC

F O

D

P EM

D

4

49.9

4

C OUT(-)

X

NC F

O

U6:

PD EM156.25MHZ_LVPECL

XUP535156.250JS6I8 - IDT

D

VDD

OE/ST

XC

F O

D

P EM

D

5

C137

U6

XC

F O

D

P EM

D

e

g

n

a

h

0.5VDD_CLK

C136

GND

e

g

n

a

h

ER89d

it

or

D

XC

F O

D

P EM

D

K2

R87

C

e

g

n

ha

Ed

r

o

it

e

g

n

a

h

XC

F O

D

P EM

D6 of

Sheet

1

Ed

i to

A

Rev

1.0

7

r

7.

54

3

2

1

3.3V

3.3V

1.1V @ 4A

3.3V

U7A

LTM4614 - CHANNEL 1

J1

C140

C141

C142

J2

10uF

10uF

0.1uF

J3

J4

J5

D

The RUN/SS1 pin has a 1M internal

resistor to VIN

C152

0.01uF

SW_1_1V

J6

K6

K1

L2

K2

L5

K3

H2

K4

PGOOD1

VIN1_1

VOUT1_0

VIN1_2

VOUT1_1

VIN1_3

VOUT1_4

VOUT1_2

VIN1_4

VOUT1_5

VOUT1_3

e

g

n

ha

VIN1_5

VIN1_11

VIN1_6

RUN/SS1

VIN1_7

COMP1

VIN1_8

XC

F O

D

P EM

D

H3

K5

H4

G1

H5

G2

H6

G3

G4

G5

G10

G6

G11

H1

G7

G12

H7

G8

H10

H8

G9

H9

SW1_0

VIN1_9

SW1_1

VIN1_10

VOUT1_8

VOUT1_6

VOUT1_10

VOUT1_7

VOUT1_9

VOUT1_11

VOUT1_12

VOUT1_15

VOUT1_13

TRACK1

FB1

VOUT1_14

1.1V

GND1_17

GND1_1

SW1_4

GND1_18

GND1_20

GND1_19

GND1_21

GND1_2

GND1_3

GND1_4

GND1_9

GND1_5

GND1_10

GND1_12

GND1_6

GND1_11

GND1_13

GND1_7

GND1_16

GND1_14

GND1_8

LTM4614

GND1_15

GND1_22

GND1_23

GND1_24

GND1_25

GND1_26

GND1_27

GND1_29

C

GND1_30

GND1_31

GND1_32

J9

J10

AVDD11_N

t

L4

C146

C148

22uF

100uF

K9

J11

120,

e

g

n

a

h

e

g

n

ha

L12

3.3V

FB_1_1V

R99

C149

22uF

DCR=15mOhm

L11

L10

K12

XC

F O

D

P EM

D

13.3k

H11

H12

J8

J7

K7

K8

L1

L7

i

d

E

t

3.3V

or

C143

C144

C145

C2

10uF

10uF

0.1uF

C3

C4

C5

C154

VIN2_1

VIN2_2

VOUT2_1

VIN2_3

VOUT2_4

VOUT2_2

B2

D4

VOUT2_8

VOUT2_6

VOUT2_10

VOUT2_7

VOUT2_9

VOUT2_11

VOUT2_14

VOUT2_12

XC

F O

D

P EM

D

SW2_0

VIN2_9

A2

B6

A3

A4

HOLE_MH_125_250

B10

B8

A9

M2

B9

GND2_0

SW2_3

GND2_17

GND2_1

SW2_4

GND2_18

GND2_2

GND2_19

GND2_22

GND2_20

GND2_23

GND2_21

GND2_24

GND2_3

A5

A10

A6

A11

B1

A7

A12

B7

A8

MH2

GND2_4

GND2_9

GND2_5

GND2_10

GND2_12

GND2_6

GND2_11

GND2_13

GND2_7

GND2_25

GND2_26

GND2_27

GND2_16

GND2_14

GND2_8

LTM4614

M3

GND2_28

GND2_15

GND2_29

M4

GND2_30

M5

M6

it

M7

M8

or

1.0V @ 8A

3.3V

C155 C157

10uF

R104

10uF

10K RUN_1V

E8

D9

D8

D7

D5

D4

D3

D1

C9

C8

C1

F1

F4

E5

B3

B5

B4

E3

B7

B8

C5

C4

C3

A1

A2

Ed

it

or

A3

A4

A5

A10

A6

A11

B9

A7

B1

B10

A8

A9

VIN-E8

VIN-D9

VIN-D8

VIN-D7

VIN-D5

VIN-D4

VIN-D3

VIN-D1

VIN-C9

VIN-C8

VIN-C1

LTM4608AEV

e

g

n

a

h

1.0V

U8

VOUT-C10

VOUT-C11

VOUT-D10

VOUT-D11

VOUT-E9

VOUT-E10

VOUT-E11

VOUT-F9

VOUT-F10

VOUT-F11

VOUT-G9

VOUT-G10

VOUT-G11

C10

C11

D10

D11

E9

E10

E11

F9

F10

F11

G9

G10

G11

SVIN

FB

TRACK

CLKIN

MODE

PHMODE

PLLLPF

BSEL

ITH

ITHM

PGOOD

MGN

SW1

SW2

SW3

CLKOUT

GND-A1

GND-G8

GND-A2

GND-G6

GND-G7

GND-G5

GND-G4

GND-G3

GND-G2

GND-G1

GND-F8

GND-F7

GND-F3

GND-B11

GND-A3

GND-A4

GND-A5

GND-A10

GND-A6

GND-A11

GND-B9

GND-A7

GND-B1

GND-B10

GND-A8

SGND

GND-A9

E7

FB_1V

C158

C159

100uF

100uF

R105

GND2_31

GND2_32

GND2_33

4.5A,

FBMH2016HM121NT

L10

FBMH2016HM121NT

L11

FBMH2016HM121NT

L12

FBMH2016HM121NT

DVDD10

C160

100uF

AVDD10_AM

4.5A,

L14

14.7K

F6

DCR=15mOhm

FBMH2016HM121NT

PG_1VR106

J22

10K

D10

C12

t

C147

AVDD15_AM

J15

L3

FBMH2016HM121NT

L5

FBMH2016HM121NT

C150

22uF

C151

22uF

100uF

120,

4.5A,

DCR=15mOhm

E9

D11

AVDD15_N

e

g

n

ha

Ed

r

o

it

D

J19

E11

E10

D12

E12

F11

F9

F12

F10

E3

E6

J18

3.3V

FB_1_5V

R100

L6

FBMH2016HM121NT

L7

FBMH2016HM121NT

C153

22uF

XC

F O

D

P EM

D

5.76k

B11

B12

C7

D8

C8

E1

D7

E7

E8

F1

F2

F3

F4

F5

F6

F7

F8

Ed

it

or

C

J20

VDDOL

VDDOL=3.3V

3.3V

R101

0

R102

0

R103

0

VDDOS

L8

VDDOS=3.3V

e

g

n

a

h

VDDO_T

MPZ1608S101ATAH0

VDDOT=3.3V

C156

22uF

3.3V

XC

F O

D

P EM

D

3.3V_CLK

L13

BLM15AX601SN1D

C161

C162

1uF

0.1uF

Ed

i to

r

B

1.8V @ 150mA

F2

3.3V

1

C164

G6

G7

G5

G4

G3

G2

G1

F8

F7

F3

B11

E1

3.3V

e

g

n

a

h

Ed

it

or

3.3V

LTST-C171GKT

D11

1.8V

U9

G8

XC

F O

D

P EM

D

4

D9

C11

XC

F O

D

P EM

D

2

1uF

OUT

NC/FB

EN

IN

GND

3.3V

LTST-C171GKT

D12

3.3V

R109

R110

R111

499

499

499

499

VDDO_M

1.8V

R107

3.3V

5

4

3

0

r

ti o

Power LEDS

C

X

F O

D

P EM

D

1.0V

1.1V

1.5V

e

g

n

a

h

1.8V

U10

1

2

3

4

5

6

3

VDDOM=1.8V

4.7uF

Ed

e

g

n

a

h

LTST-C171GKT

D13

R108

J24

C165

TPS76318DBVT

7

5

C10

or

C163

22uF

3.3V

F5

C7

J23

i

d

E

C9

e

g

n

a

h

DCR=15mOhm

L9

120,

LTST-C171GKT

D10

XC

F O

D

P EM

D

or

120,

J21

XC

F O

D

P EM

D

RUN/SS

Ed

it

PG_1_5V

SW2_2

A1

B5

1

VOUT2_15

VOUT2_13

TRACK2

FB2

SW2_1

VIN2_10

B4

E4

e

g

n

ha

VOUT2_5

VOUT2_3

RUN/SS2

VIN2_7

COMP2

VIN2_8

B3

D5

HOLE_MH_125_250

M1

PGOOD2

VOUT2_0

VIN2_5

VIN2_11

VIN2_6

E2

D2

E5

D3

SW_1_5V

VIN2_0

VIN2_4

C6

D6

D1

0.01uF

1

10K

1.5V

LTM4614 - CHANNEL 2

C1

The RUN/SS2 pin has a 1M internal

resistor to VIN

MH1

R98

U7B

L8

XC

F O

D

P EM

D

e

g

n

a

h

4.5A,

L9

K11

M9

M12

M10

L3

L6

M11

J16

FBMH2016HM121NT

K10

J12

Ed

GND1_33

A

J17

SW1_2

GND1_0

SW1_3

GND1_28

B

1.5V @ 4A

10K

PG_1_1V

L4

i

d

E

VIN1_0

or

R97

8

C1-1

C1-2

C2-1

C2-2

E1

B1

E2

B2

E3

B3

E4

16

15

14

13

12

11

10

R112

2K

R113

2K

R114

2K

R115

2K

Title

MMPQ2222A

C3-1

C

C4-1

C4-2

B4

XC

F O

D

P EM

D

A

POWER SUPPLIES

Size

C3-2

9

Ed

i to

Date:

2

Document Number

<Doc>

Thursday, September 24, 2015

1

Sheet

Rev

1.0

7

of

7

r

drafting

drafting