Similar presentations:

Цифроаналоговые преобразователи

1.

Цифроаналоговые преобразователи• Задание для всех бригад:

Ознакомится с типами ЦАП, приведенными в презентации;

Статические параметры для исследуемого ЦАП;

Динамические параметры для исследуемого ЦАП;

Исследовать принцип работы каждого типа ЦАП;

ЗАДАНИЯ ПО БРИГАДАМ типов ЦАП, приведенными в презентации

на соответствующих слайдах:

Бригада 1

слайд 6;

Бригада 2

слайд 7;

Бригада 3

слайд 8;

Бригада 4

слайд 9;

Бригада 5

слайд 10.

В отчете привести расчеты параметров, элементов схем

соответствующих ЦАП, привести графики изменения напряжения

при изменении кодов на входе ЦАП;

Сравнить по эффективности и затратам элементов схем.

2.

Цифроаналоговые преобразователиУсловное графическое обозначение:

XN (xn-1,… x0)

UN

N

A

n -разрядность ЦАП

3.

Классификация ЦАП.ЦАП

Последовательные ЦАП

ШИМ

на переключаемых

конденсаторах

Параллельные

ЦАП

1. ЦАП на декодирующих сетках

сопротивлений взвешенных по

двоичному закону.

2. ЦАП на декодирующих сетках

сопротивлений R - 2R.

3. ЦАП c токовыми ключами.

4. ЦАП со стабилизацией разрядных

токов транзисторными источниками

тока.

4.

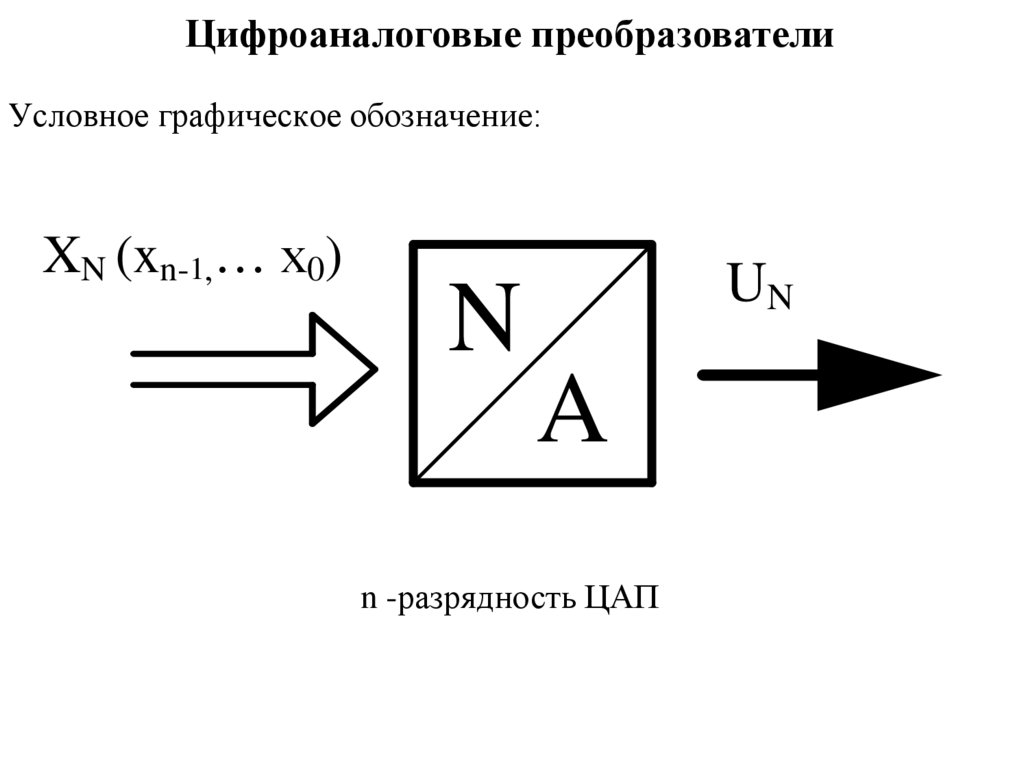

Статические параметры ЦАПUN

Uq

δΔUq

δUN0

1. Разрешающая способность.

Шаг квантования ΔUq или приращение выходного

напряжения UN при увеличении входного кода на

δU единицу младшего разряда (МЗР). Среднее значение

шага квантования:

N

Nmax

U q

(U N )max (U N )max

n

N max

2 1

n -разрядность ЦАП

2.Погрешность смещения нуля.

Значения напряжения δUN0 на выходе ЦАП при нулевом значении входного

кода. Погрешность аддитивная. Измеряется в % от ПШ или в долях МЗР.

3.Погрешность полной шкалы (интегральная нелинейность).

Разность между реальным и идеальным пределами шкалы при отсутствии

N

смещения нуля, измеряется в % от ПШ или долях МЗР :

δU N ΔUq ΔUqi

4.Дифференциальная нелинейность.

1

Максимальное отклонение реального шага квантования от номинального,

Измеряется в % от ПШ или в долях МЗР.

Uq ( Uq Uqi )max

5. Динамические параметры ЦАП

UN∆UN

∆t

0

tу

1МЗР

UN1

1. Время установления tу.

Интервал времени от момента изменения

входного кода до момента, когда выходной

аналоговый сигнал окончательно войдет в

зону заданной ширины, симметрично

расположенную относительно

установившегося значения UN1.

2. Частота обновления fmax.

Максимальная частота, с которой может

t происходить смена содержимого входных

регистров ЦАП. fmax ≤ 1/[(2….3)tуmax]

3. Скорость нарастания.

Максимальная скорость изменения UN(t) во время переходного процесса.

Определяется как отношение ∆UN ко времени ∆t, за которое произошло

это приращение.

6.

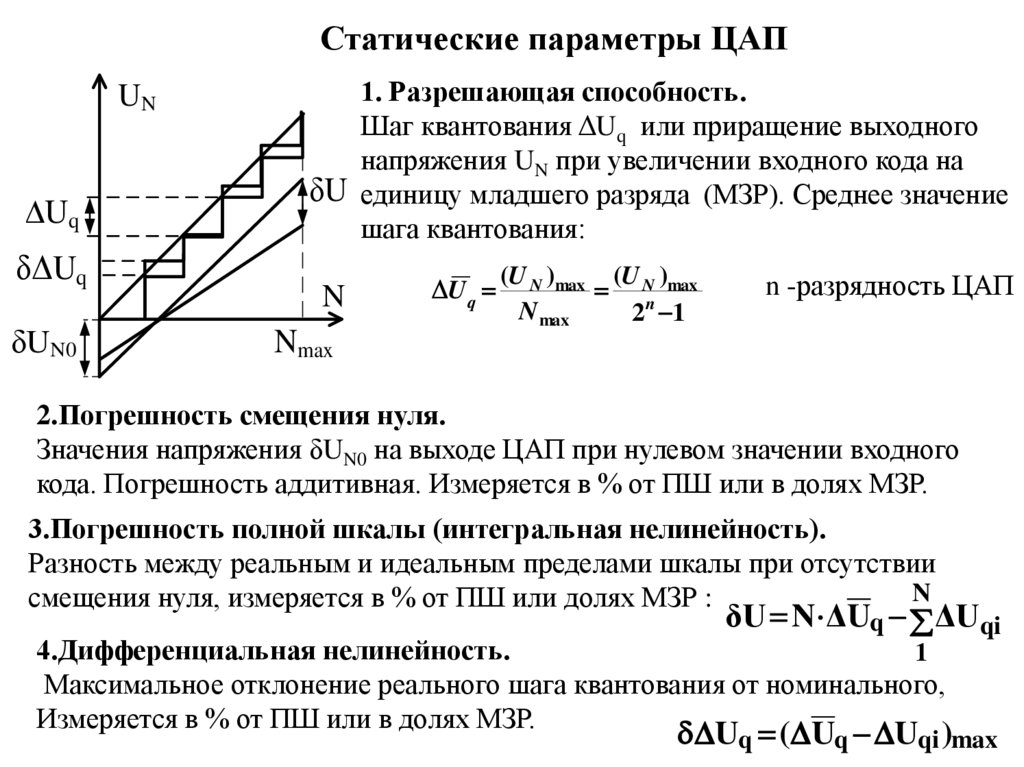

ЦАП последовательного типа унитарного кодаT tи

U1 E0 C1

C1 C2

Uобр

E0

UN

U2 E0 U1 C1

C1 C2

C1

N 1

R

C2

UN E0 U i C1

C1 C2

RC1 >> RC2

1

C1 >> C2

N

UN U i

(T-tи)>>RC1

1

T tи

VD

E0

U

U

N

N

ΔUi

C2

C1

K0

ΔU1

ΔUi=const

R

1 2 3

...

i

N

7.

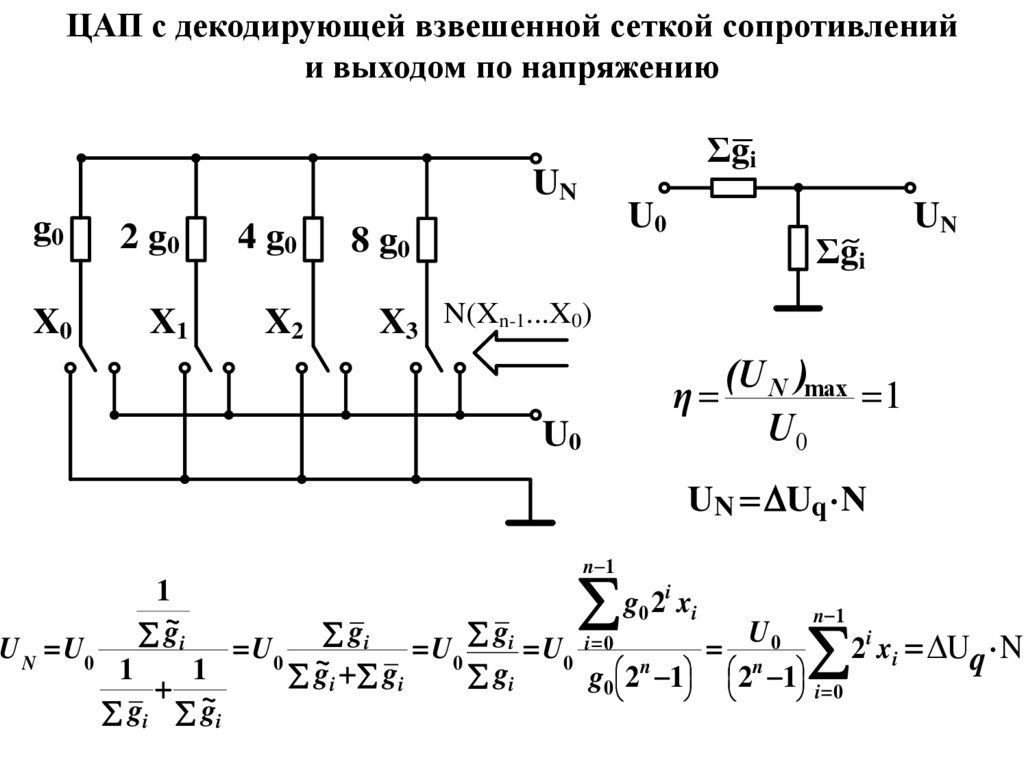

ЦАП с декодирующей взвешенной сеткой сопротивленийи выходом по напряжению

Σgi

UN

g0

2 g0

4 g0

X0

X1

X2

U0

8 g0

Σgi

UN

X3 N(Xn-1...X0)

(U N )max

η

1

U0

U0

UN Uq N

n 1

1

g~i

g0 2 i x i

n 1

g

g

U

U N U0

U0 ~ i U0 i U0 i 0 n

n0

2i xi ΔUq N

1

1

g

g

g

g

2 1

2 1

i

i

i

0

~

i 0

gi gi

8.

ЦАП с весовой декодирующей резистивной сеткой и токовыми ключами.U0

n-1

In-1= I0 2

R

2R

4R

Kn

Kn-1

Kn-2

Xn-1

Xn-2

Xn-3

I0

n-1

R2

K2

K1

X1

X0

Rос=R

K0

UN

R

UN

UN U0

U0

U0

U0

X

X .... i Xi n 1 X0

R 20 R n 1 21 R n 2

2 R

2 R

U 0 n 1

U 0 n 1 i

n 2

1

0

U N n 1 2 X n 1 2 X n 2 .... 2 X1 2 X 0 n 1 2 X i U q N

2

2 i 0

(U N ) max U 0 2 n 1

n 1

2

U0

2 U 0

*

Rвых

Rвых

1 K 0

1

2

U q

* 5 10 Ом

Rвых

U0

2 n 1

9.

Параллельный ЦАП каскадного типа.8R

U0

4R

2 I0

I0

X0

2R

4 I0

X1

R

8R

8 I0

X2

I1

R1

32R

16R

U0

7

4 I0

8 I0

X4

X5

X6

X7

Roc=R

K0

I2

R1=1 Ом

X i 2i

i=0

UN =

2 I0

R2=15 Ом

n-1

UN = 2n-1

U0

R

R2

I1

128R 64R

2R

I0

I2 = 16

X3

4R

7

2 i=0

n

(UN)max

U0 2 - 1

η=

=

U0

U0 2n-1

2

X i 2i

Делитель на сопротивлениях R1 и R2 уменьшает разрядные токи первого

каскада в 16 раз.

UN

10.

ЦАП с декодирующей сеткой R-2R и токовыми ключами.U0

R

Xn-1

2R

Xn-2

a

R

2R

Xn-3

R

R

X1

2R

X0

2R

2R

2R

R=10 кОМ

K0

Функция преобразования:

XN=1000 . . . 0

U0

XN=0100. . . 0

U0

2R

2R

UN1

UN [ X ( xn 1 , xn 2, x0) ]

R

K0

U0 U0

2 1

2

UN

UN1

2R

R

R

а 2R

2R

K0

UN2

UN2 U 0 1 U 0

2 2 22

n 1

U

U

U

U

U

UN 0 Xn 1 0 Xn 2 0 X1 0 X0 0 2i Xi Uq N

21

22

2n 1

2n

2n i 0

11.

10 разрядный ЦАП типа 572ПА1. (R-2R)НАЗНАЧЕНИЕ ВЫВОДОВ

Символ

Назначение

DIP, б/к

SOIC

DBO

Вход 9 разряда (СЗР)

4

9

DB1

Вход 8 разряда

5

10

DB2

Вход 7 разряда

6

11

DB3

Вход 6 разряда

7

12

DB4

Вход 5 разряда

8

13

DB5

Вход 4 разряда

9

14

DB6

Вход 3 разряда

10

15

DB7

Вход 2 разряда

11

16

DB8

Вход 1 разряда

12

1

DB9

Вход 0 разряда (МЗР)

13

2

GND

Общий вывод (земля)

3

8

OUTA1

Аналоговый выход 1

1

6

OUTA2

Аналоговый выход 2

2

7

RFB

Резистор обратной связи

16

5

VCC

Напряжение питания

14

3

VREF

Опорное напряжение

15

4

ЦОКОЛЕВКА КОРПУСОВ

572ПА1

КР572ПА1

OUTA1 1

OUTA2 2

GND 3

DB0 4

DB1 5

DB2 6

DB3 7

DB4 8

9

10

11

12

13

14

15

16

RFB

VREF

VCC

DB9

DB8

DB7

DB6

DB5

12.

Высокоточный ЦАП на источниках тока.R

X1

X0

Xn-1 Xn-2

R0

K0

U01

I0

VTn-1 VTn-2

K0

VT1

VT0

VTL

Uбэ = const

2R

2R

2R

U02

R

2R

2R

1)Площади эмиттеров транзисторов формируются в соответствии

с весовыми токами (многоэмиттерные).

2)Ток транзистора VT0 младшего разряда равен половине тока

через VT1 , т.к. токи VT0 и VTL равны.

3)Функция преобразования

n 1

U

UN 02 2i x i Uq N

2n

i 0

UN

13.

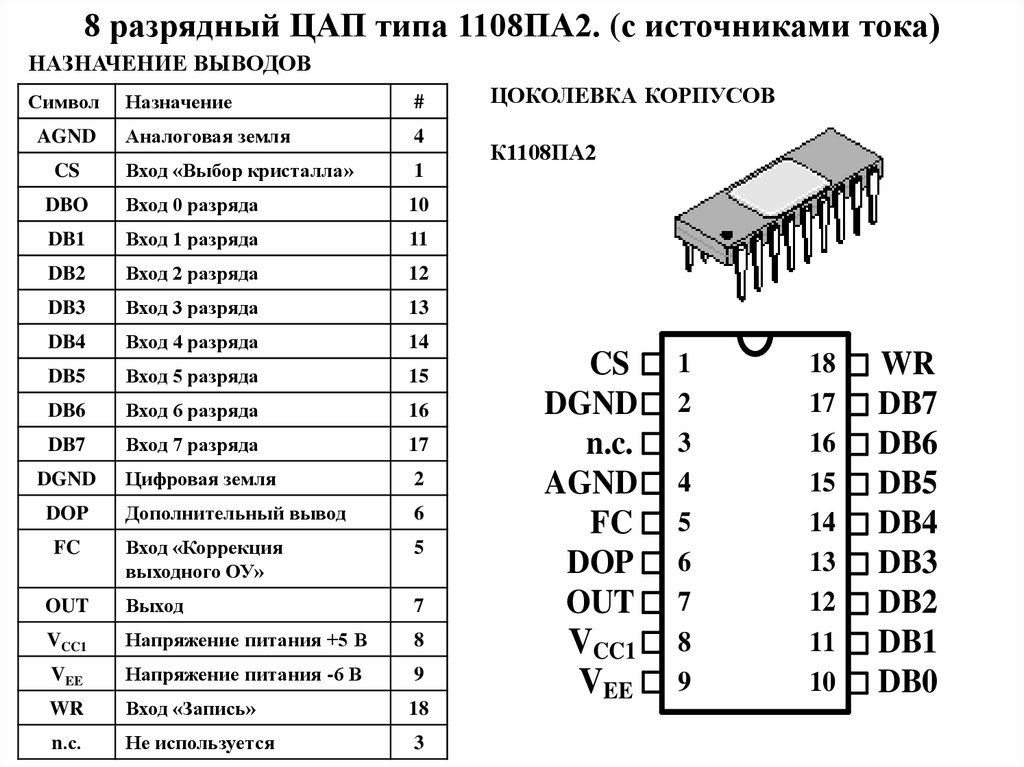

8 разрядный ЦАП типа 1108ПА2. (с источниками тока)НАЗНАЧЕНИЕ ВЫВОДОВ

Символ

Назначение

#

AGND

Аналоговая земля

4

CS

Вход «Выбор кристалла»

1

DBO

Вход 0 разряда

10

DB1

Вход 1 разряда

11

DB2

Вход 2 разряда

12

DB3

Вход 3 разряда

13

DB4

Вход 4 разряда

14

DB5

Вход 5 разряда

15

DB6

Вход 6 разряда

16

DB7

Вход 7 разряда

17

DGND

Цифровая земля

2

DOP

Дополнительный вывод

6

FC

Вход «Коррекция

выходного ОУ»

5

OUT

Выход

7

VCC1

Напряжение питания +5 В

8

VEE

Напряжение питания -6 В

9

WR

Вход «Запись»

18

n.с.

Не используется

3

ЦОКОЛЕВКА КОРПУСОВ

К1108ПА2

CS

DGND

n.c.

AGND

FC

DOP

OUT

VCC1

VEE

1

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

10

WR

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

14.

ЦАП – принцип токового интегрирования(тройное токовое интегрирование)

Xn

RG - n=16

20

24

C СТ–2–5

младш. р.

≤0 W

f0

29

210 215

C СТ–2–5

сред. р.

≤0 W

C СТ–2–6

старш. р.

≤0 W

25

Uвых(ЦАП)

W

tП

t

C1

T0

tC

0

К1

К2

К3

t

t1

0

I1

I2

I3

ОУ

Uвых

t

t2

0

t

I1= I0

1.

I2= I0 2

5

I3= I0 2

0

10

t3

t

В момент времени tО импульсом tП 16 разрядов входного регистра RG

переписываются в три счетчика – для 6 старших разрядов, для 5 средних разрядов и для 5 младших

разрядов. Одновременно включаются ключи K1, K2 и K3, подключая источники тока к заряду ёмкости С1

интегратора.

t1 T0 N1

t2 T0 N 2

t3 T0 N 3

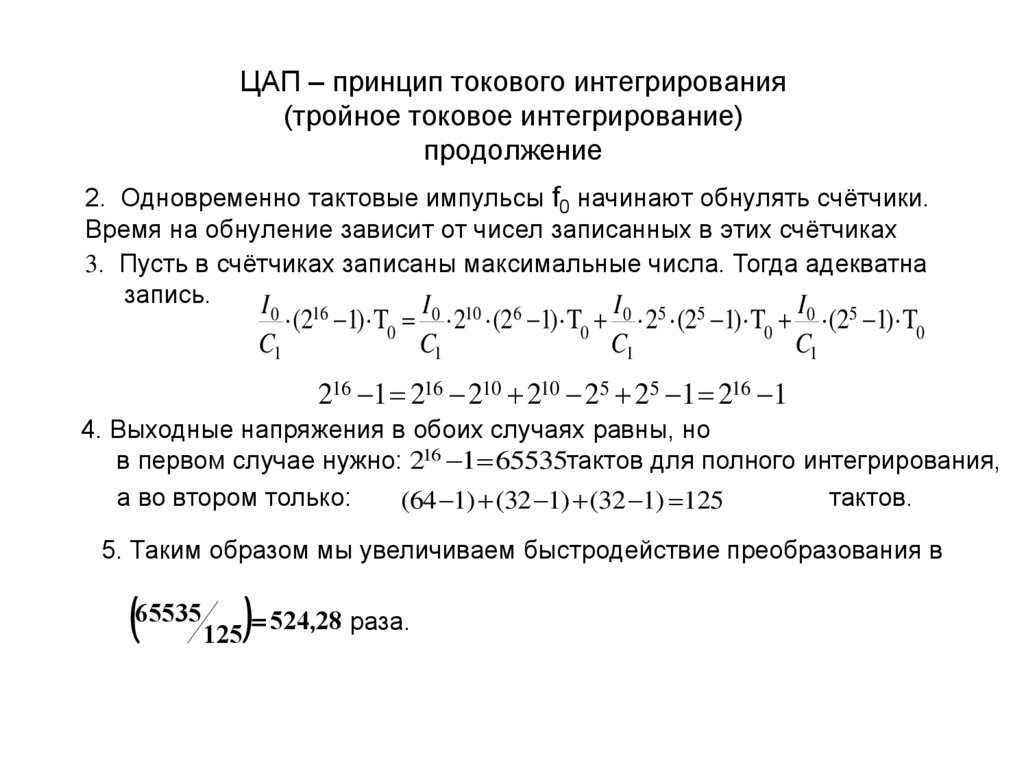

15. ЦАП – принцип токового интегрирования (тройное токовое интегрирование) продолжение

2. Одновременно тактовые импульсы f0 начинают обнулять счётчики.Время на обнуление зависит от чисел записанных в этих счётчиках

3. Пусть в счётчиках записаны максимальные числа. Тогда адекватна

запись.

I

I

I

I

0 (216 1) T 0 210 (26 1) T 0 25 (25 1) T 0 (25 1) T

0

0

0

0

C1

C1

C1

C1

216 1 216 210 210 25 25 1 216 1

4. Выходные напряжения в обоих случаях равны, но

в первом случае нужно: 216 1 65535тактов для полного интегрирования,

а во втором только:

тактов.

(64 1) (32 1) (32 1) 125

5. Таким образом мы увеличиваем быстродействие преобразования в

65535125 524,28 раза.

16.

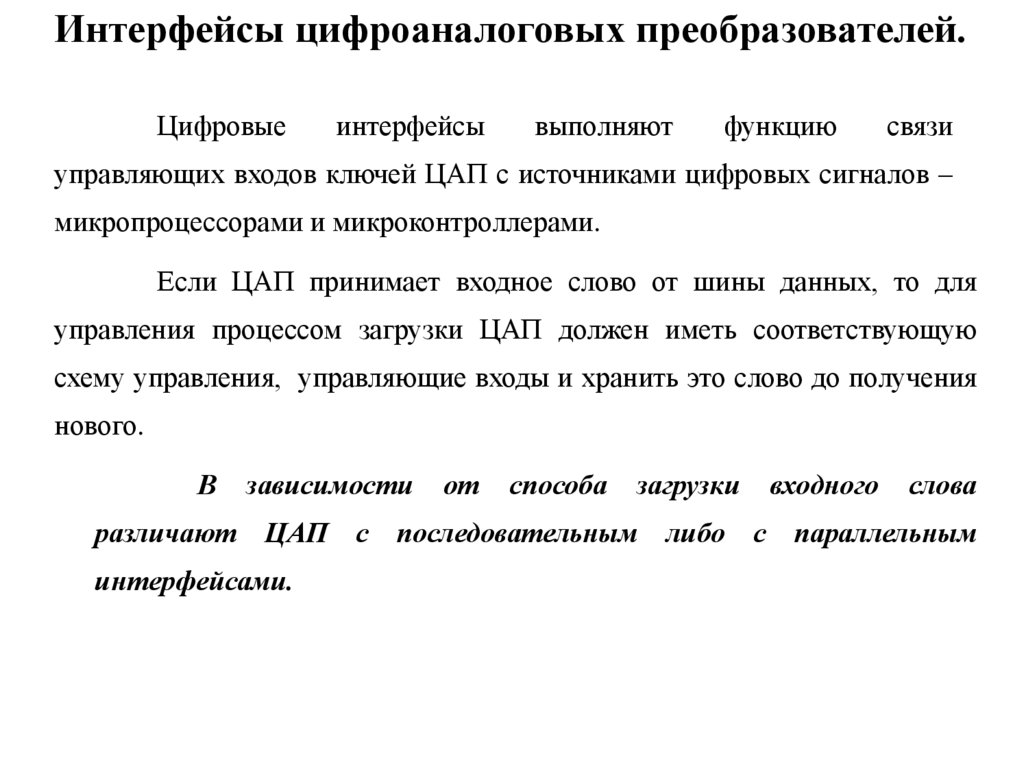

Интерфейсы цифроаналоговых преобразователей.Цифровые

интерфейсы

выполняют

функцию

связи

управляющих входов ключей ЦАП с источниками цифровых сигналов –

микропроцессорами и микроконтроллерами.

Если ЦАП принимает входное слово от шины данных, то для

управления процессом загрузки ЦАП должен иметь соответствующую

схему управления, управляющие входы и хранить это слово до получения

нового.

В

зависимости

от

способа

загрузки

входного

слова

различают ЦАП с последовательным либо с параллельным

интерфейсами.

17.

Временные диаграммы работы последовательного интерфейса.D1

Dn-1

0

t1

t2

CLK

t

t5

0

CS

D1 – загрузка входного слова;

D0

t3

t4

0

тактовые

импульсы

СS – разрешение на загрузку в

t регистр сдвига;

t6

LD - разрешение на запись в регистр

хранения;

0

LD

CLK

–

управления;

t

t7

–

минимальные

значения

интервалов

времени

в

последовательностях управляющих

t сигналов.

ti

Для ЦАП AD7233 эти интервалы близки к 50нс.

18.

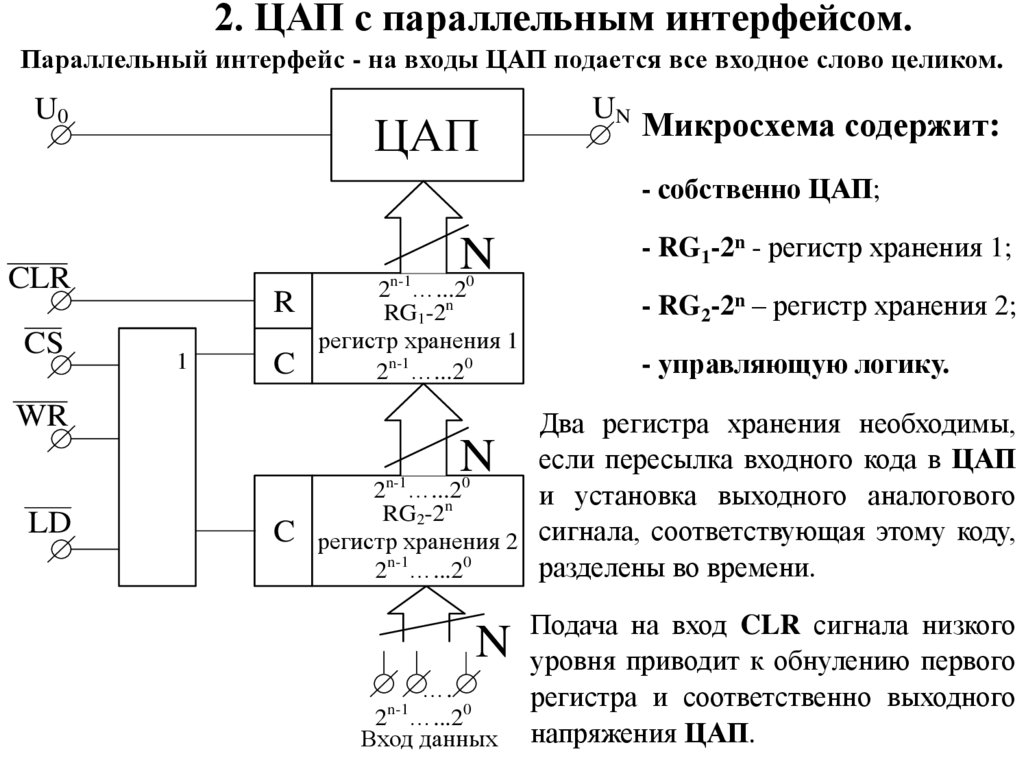

2. ЦАП с параллельным интерфейсом.Параллельный интерфейс - на входы ЦАП подается все входное слово целиком.

U0

ЦАП

UN

Микросхема содержит:

- собственно ЦАП;

CLR

CS

WR

n-1

R

1

C

N

2 …...20

RG1-2n

регистр хранения 1

2n-1…...20

- RG1-2n - регистр хранения 1;

- RG2-2n – регистр хранения 2;

- управляющую логику.

Два регистра хранения необходимы,

если пересылка входного кода в ЦАП

n-1

0

2 …...2

и установка выходного аналогового

RG2-2n

C регистр хранения 2 сигнала, соответствующая этому коду,

разделены во времени.

2n-1…...20

N

LD

N

….

2 …...20

Вход данных

n-1

Подача на вход CLR сигнала низкого

уровня приводит к обнулению первого

регистра и соответственно выходного

напряжения ЦАП.

19.

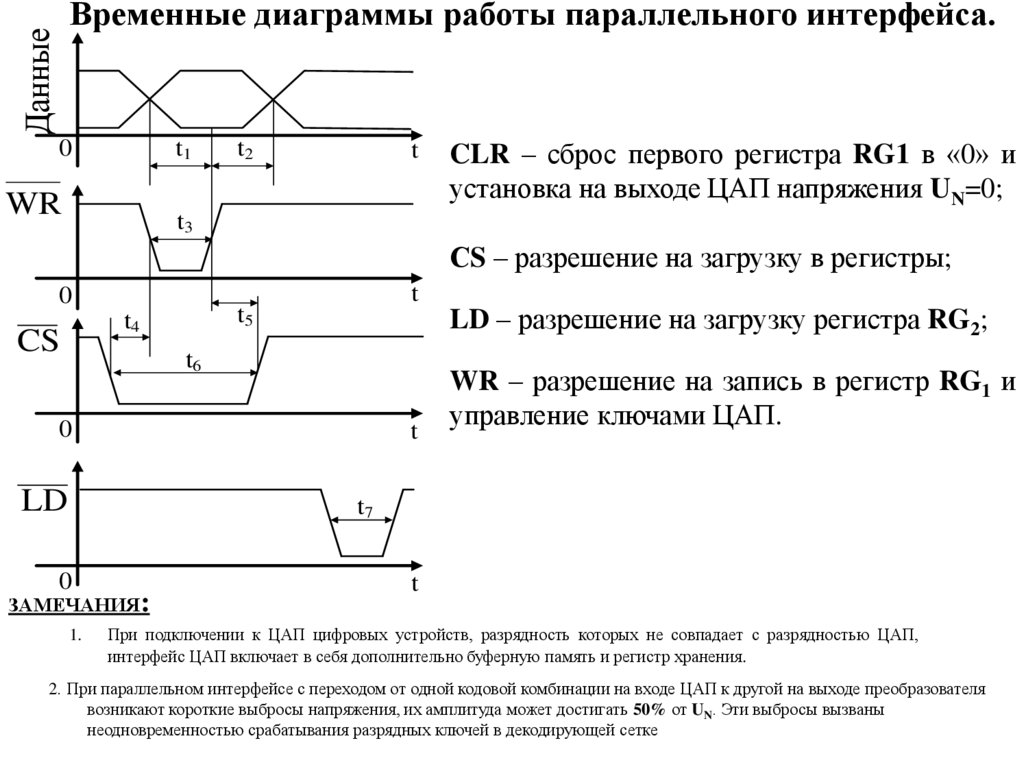

ДанныеВременные диаграммы работы параллельного интерфейса.

0

t1

WR

t2

t

CLR – сброс первого регистра RG1 в «0» и

установка на выходе ЦАП напряжения UN=0;

t3

СS – разрешение на загрузку в регистры;

0

t5

t4

CS

t

t6

0

t

LD

LD – разрешение на загрузку регистра RG2;

WR – разрешение на запись в регистр RG1 и

управление ключами ЦАП.

t7

0

ЗАМЕЧАНИЯ:

1.

t

При подключении к ЦАП цифровых устройств, разрядность которых не совпадает с разрядностью ЦАП,

интерфейс ЦАП включает в себя дополнительно буферную память и регистр хранения.

2. При параллельном интерфейсе с переходом от одной кодовой комбинации на входе ЦАП к другой на выходе преобразователя

возникают короткие выбросы напряжения, их амплитуда может достигать 50% от UN. Эти выбросы вызваны

неодновременностью срабатывания разрядных ключей в декодирующей сетке

20.

ЦАП в цифровой схемотехнике.1. Аттенюатор – точный цифровой делитель напряжения.

Uх=U0

Uх

UN=Uу

R, 2R, 4R ...

K0

R

ЦАП

Uу

N

Uу Ux n

2 1

U0

UN n N

2 1

N

Ux

Uу

N

ΔU

K

n

у

n

2

1

Ux 2 1

2. Точный цифровой умножитель напряжения.

IN

ЦАП

U0

R, 2R, 4R ...

R1 R

N

Uх R1

Ix

U0N

IN n

(2 1)R

K0

Uу=U0

Uу

U x I N R1

UуR N

2 1 R

n

2n 1

Uу Ux

N

2n 1

K

Ux

N

Uу

electronics

electronics