Similar presentations:

Триггеры с разрешением тактирования

1.

FPGA: ТРИГГЕРЫ С РАЗРЕШЕНИЕМТАКТИРОВАНИЯ

2.

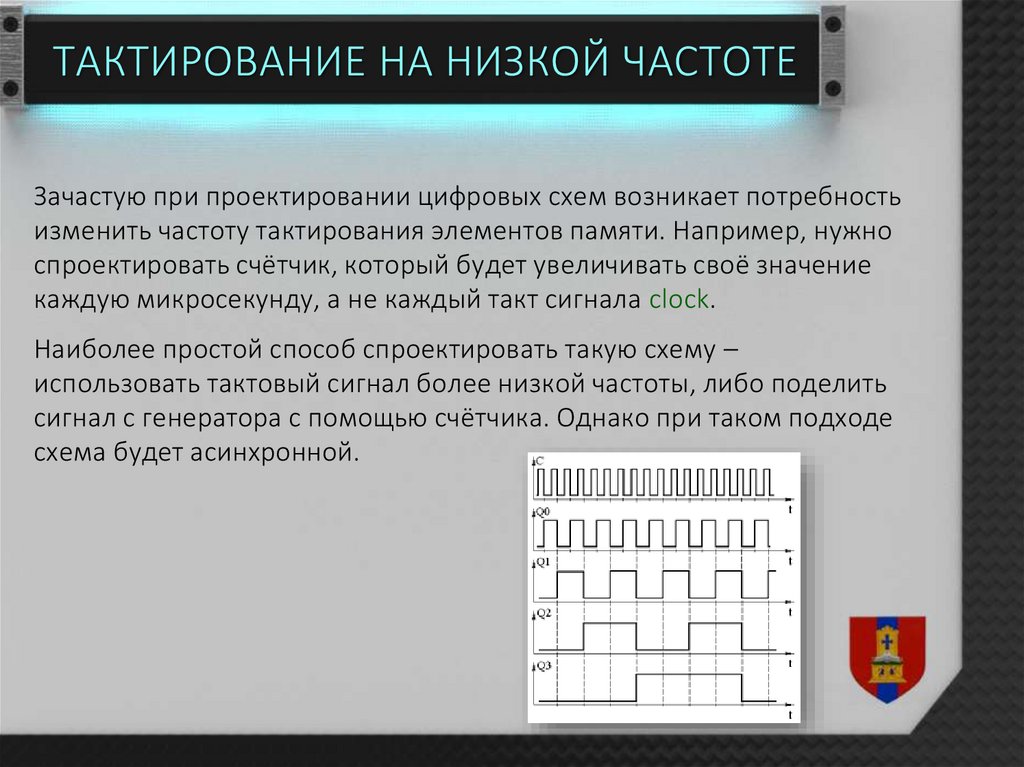

ТАКТИРОВАНИЕ НА НИЗКОЙ ЧАСТОТЕЗачастую при проектировании цифровых схем возникает потребность

изменить частоту тактирования элементов памяти. Например, нужно

спроектировать счётчик, который будет увеличивать своё значение

каждую микросекунду, а не каждый такт сигнала clock.

Наиболее простой способ спроектировать такую схему –

использовать тактовый сигнал более низкой частоты, либо поделить

сигнал с генератора с помощью счётчика. Однако при таком подходе

схема будет асинхронной.

3.

СИГНАЛ ENAВторой способ – использовать сигнал ena.

У каждого триггера имеется так называемый сигнал разрешения

тактирования – сигнал ena (от анг. enable – включить). Если этот

сигнал равен ‘1’, то триггер работает в обычном режиме. Если этот

сигнал равен ‘0’, то триггер не реагирует на тактовые сигналы

(выключается) и просто хранит предыдущее значение.

Используя данный сигнал, можно проектировать синхронные схемы,

работающие с частотой, кратной тактовой. Например, если сигнал

ena устанавливается в ‘1’ каждый пятый такт сигнала clock, то триггер

будет работать на частоте, в пять раз меньшей, чем частота тактового

сигнала. Т. е. частота работы будет определяться частотой сигнала

ena.

4.

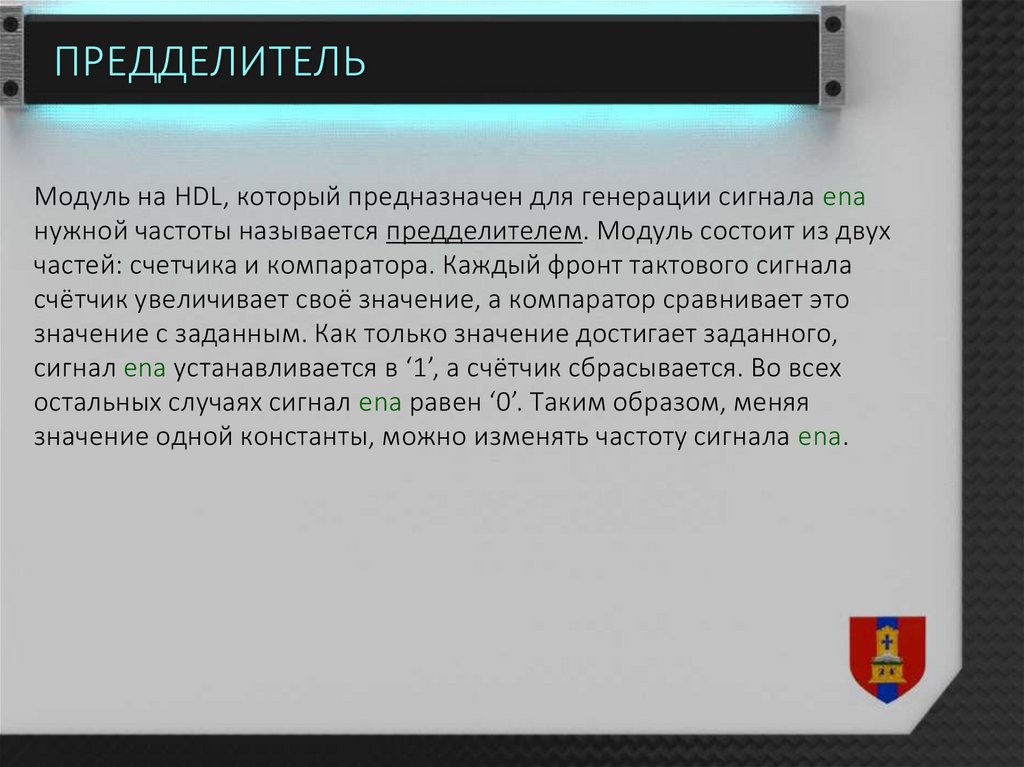

ПРЕДДЕЛИТЕЛЬМодуль на HDL, который предназначен для генерации сигнала ena

нужной частоты называется предделителем. Модуль состоит из двух

частей: счетчика и компаратора. Каждый фронт тактового сигнала

счётчик увеличивает своё значение, а компаратор сравнивает это

значение с заданным. Как только значение достигает заданного,

сигнал ena устанавливается в ‘1’, а счётчик сбрасывается. Во всех

остальных случаях сигнал ena равен ‘0’. Таким образом, меняя

значение одной константы, можно изменять частоту сигнала ena.

5.

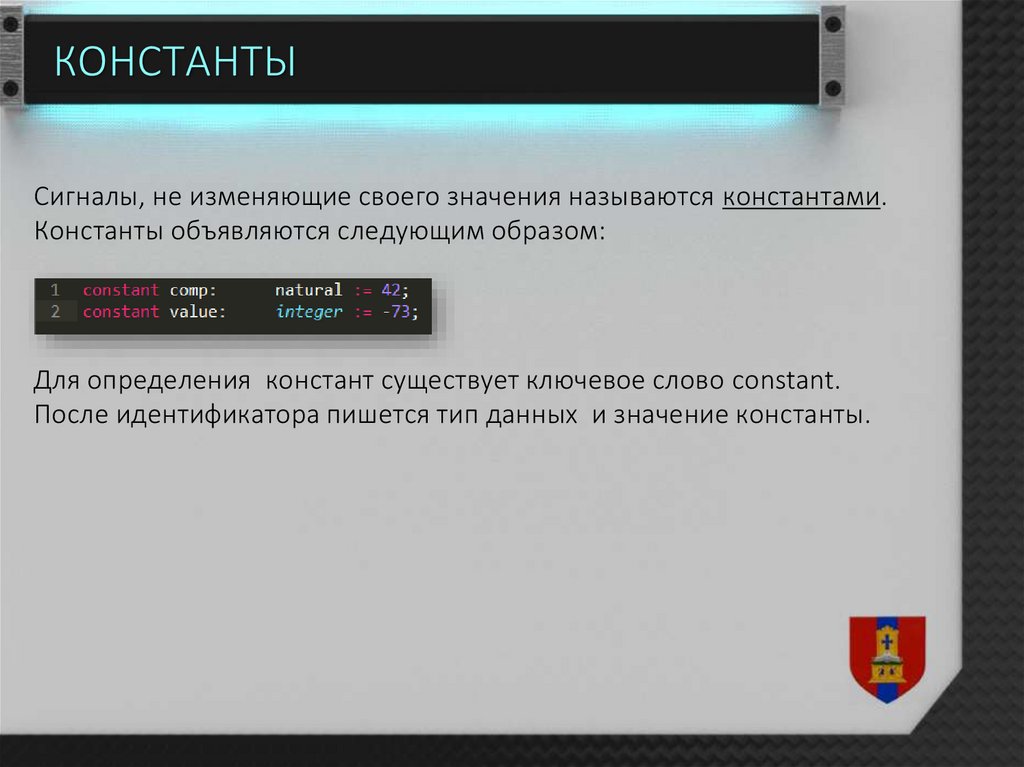

КОНСТАНТЫСигналы, не изменяющие своего значения называются константами.

Константы объявляются следующим образом:

Для определения констант существует ключевое слово constant.

После идентификатора пишется тип данных и значение константы.

6.

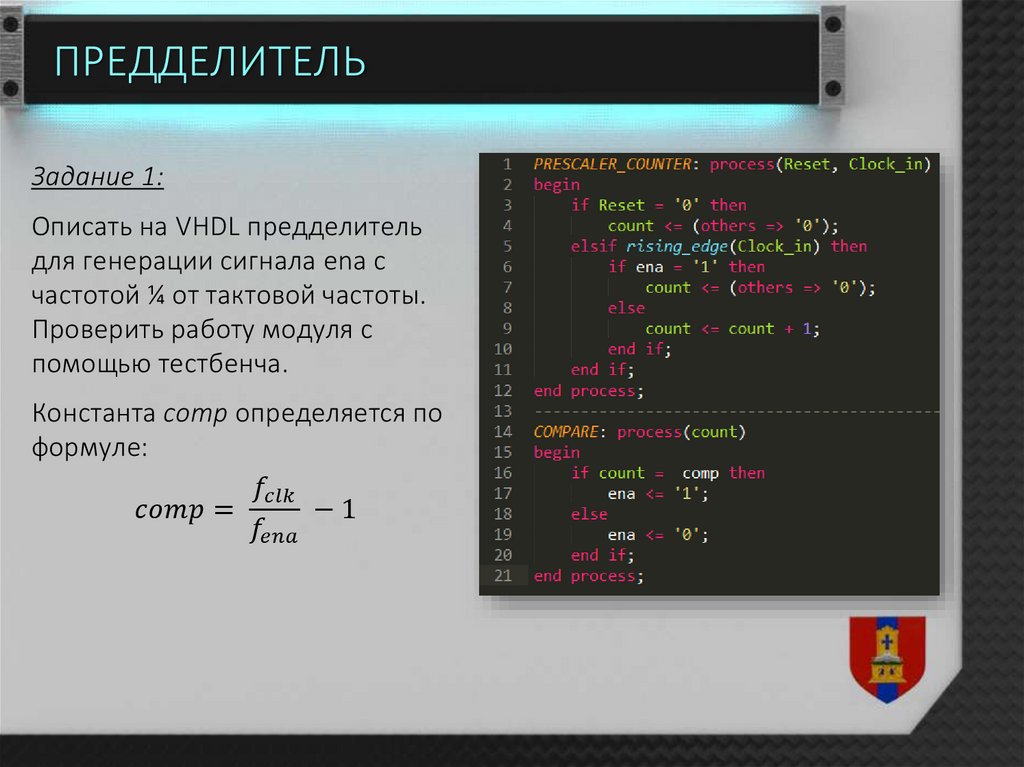

ПРЕДДЕЛИТЕЛЬЗадание 1:

Описать на VHDL предделитель

для генерации сигнала ena с

частотой ¼ от тактовой частоты.

Проверить работу модуля с

помощью тестбенча.

Константа comp определяется по

формуле:

electronics

electronics