Similar presentations:

Микроконтроллеры и Встраиваемые Системы Управления (базовый курс)

1.

Научный центр информационных технологийи искусственного интеллекта

Научно-образовательное направление

МАТЕМАТИЧЕСКАЯ РОБОТОТЕХНИКА

И ИСКУССТВЕННЫЙ ИНТЕЛЛЕКТ

20.11.2023 – 25.11.2023

2.

Шипатов Андрей Владимировичкандидат технических наук

доцент НТУ «Сириус», направление «Математическая робототехника»

доцент НИУ «МИЭТ» (Московский институт электронной техники)

начальник отдела разработки АО «Зеленоградский инновационно-технологический центр»

генеральный директор ООО «Электронные микросистемы» (ООО «ЭЛМИКС»)

Микроконтроллеры и Встраиваемые Системы Управления (базовый курс)

Microcontrollers and Embedded Control Systems (basic course)

www.elmics.com

3.

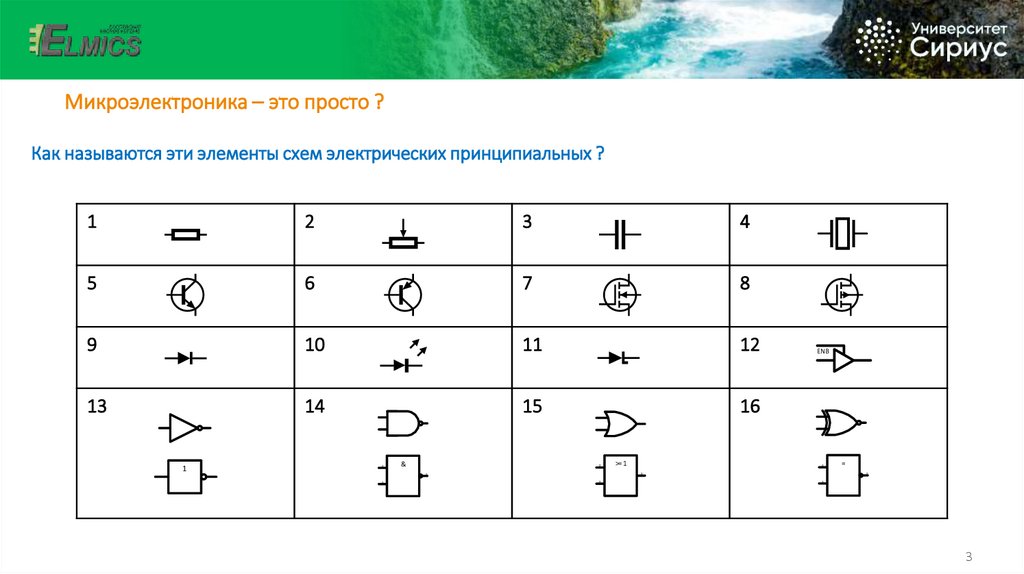

Микроэлектроника – это просто ?Как называются эти элементы схем электрических принципиальных ?

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

0

&

0

0

0

=

0

0

0

0

>=1

ENB

0

3

4.

Микроэлектроника – это просто ?Как называются эти элементы схем электрических принципиальных ?

1

резистор

биполярный

транзистор

n-p-n типа

5

9

диод

13

2

переменный

резистор

3

6

биполярный

транзистор

p-n-n типа

7

10

светодиод

14

1

логический

элемент

«НЕ»

(NOT)

конденсатор

полевой

n-канальный

транзистор

11

стабилитрон

15

0

&

0

0

логический

элемент

«2И-НЕ»

(AND)

4

кварцевый

резонатор

8

полевой

p-канальный

транзистор

12

буфер с 3-м

состоянием

ENB

16

0

>=1

0

0

логический

элемент

«ИЛИ»

(OR)

0

=

0

0

логический

элемент

«искл. ИЛИ»

(XOR)

4

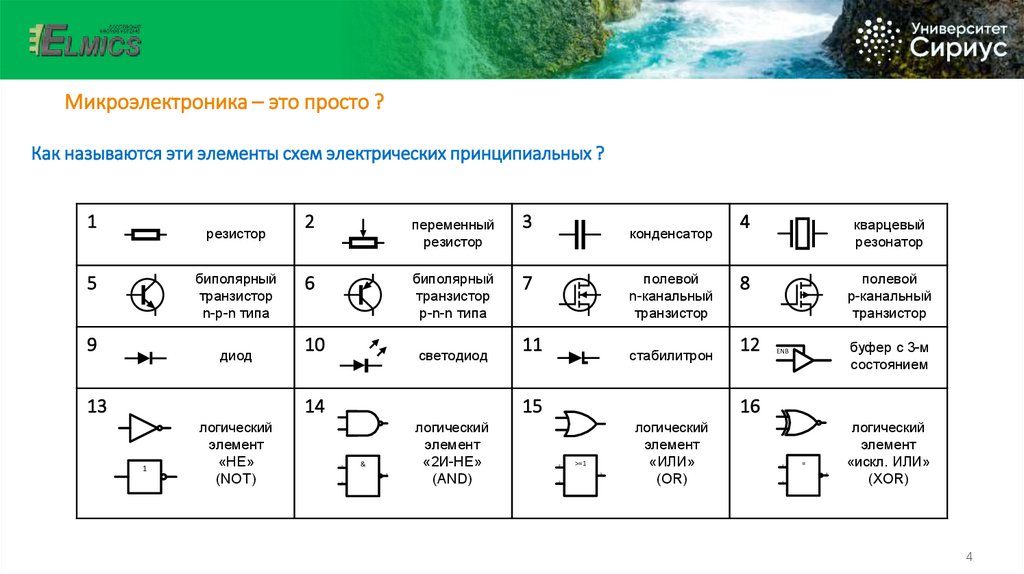

5.

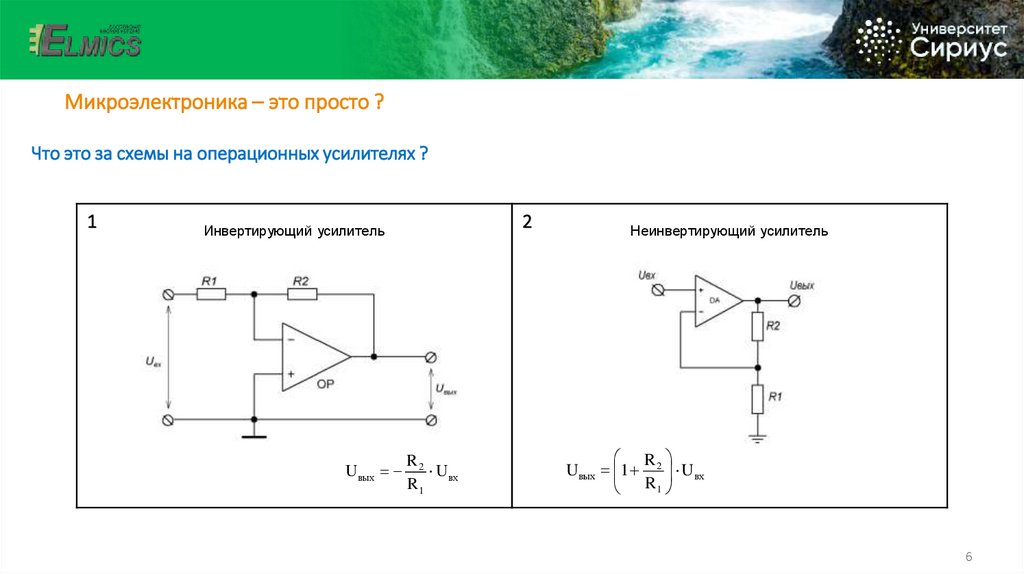

Микроэлектроника – это просто ?Что это за схемы на операционных усилителях ?

1

2

5

6.

Микроэлектроника – это просто ?Что это за схемы на операционных усилителях ?

1

2

Инвертирующий усилитель

U вых

R2

U вх

R1

Неинвертирующий усилитель

R

Uвых 1 2 Uвх

R1

6

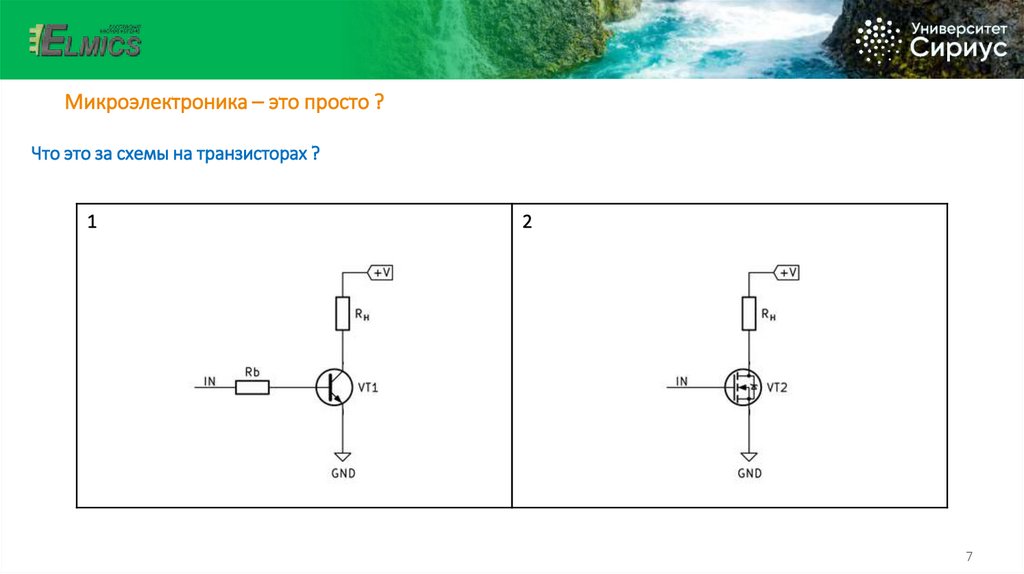

7.

Микроэлектроника – это просто ?Что это за схемы на транзисторах ?

1

2

7

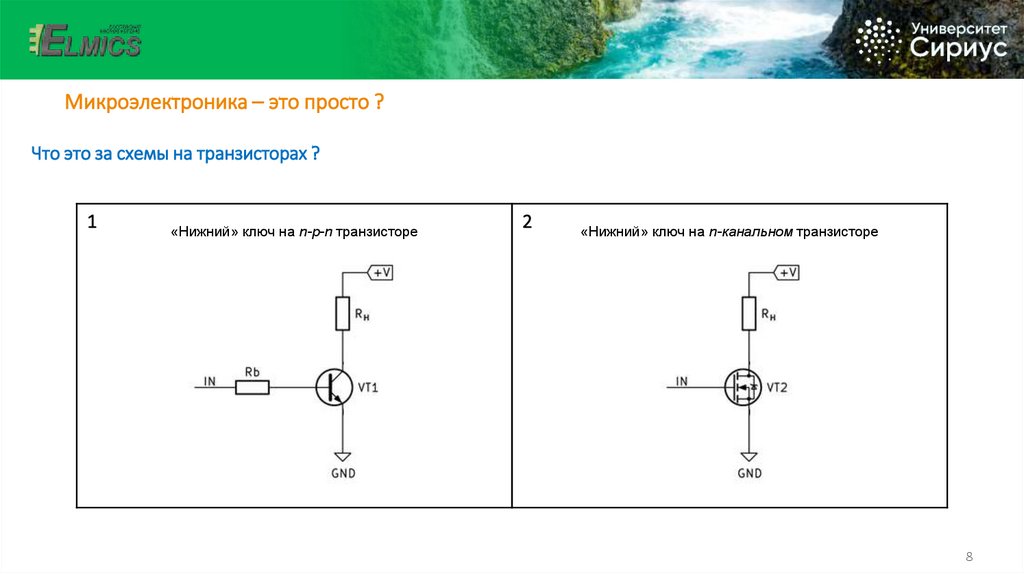

8.

Микроэлектроника – это просто ?Что это за схемы на транзисторах ?

1

«Нижний» ключ на n-p-n транзисторе

2

«Нижний» ключ на n-канальном транзисторе

8

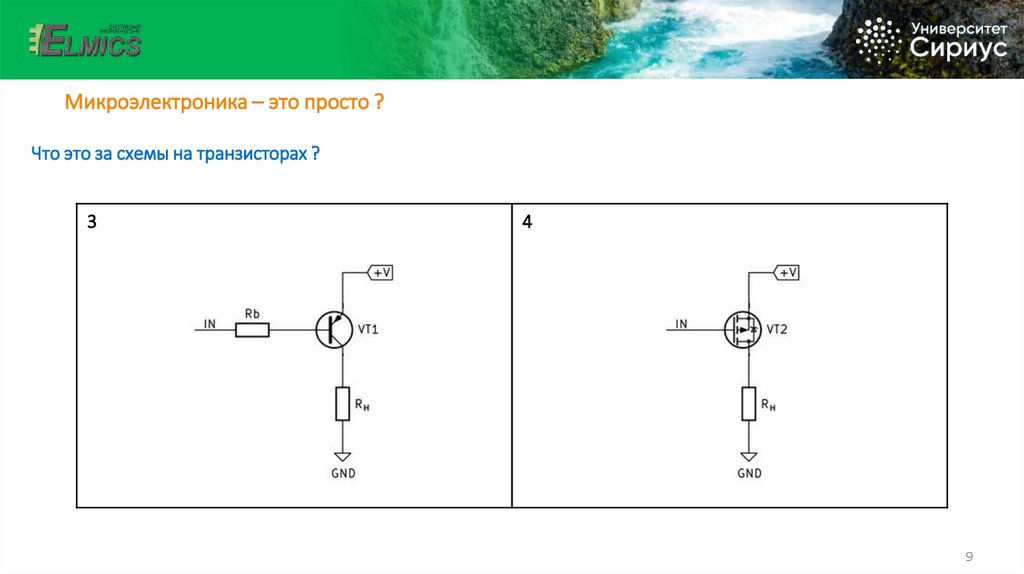

9.

Микроэлектроника – это просто ?Что это за схемы на транзисторах ?

3

4

9

10.

Микроэлектроника – это просто ?Что это за схемы на транзисторах ?

3

«Верхний» ключ на p-n-p транзисторе

4

«Верхний» ключ на p-канальном транзисторе

10

11.

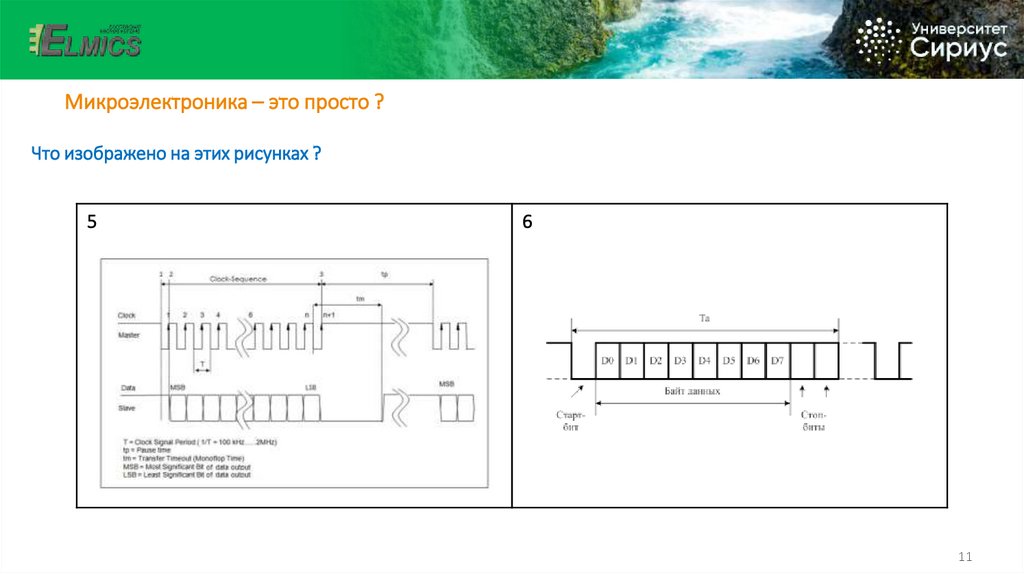

Микроэлектроника – это просто ?Что изображено на этих рисунках ?

5

6

11

12.

Микроэлектроника – это просто ?Что изображено на этих рисунках ?

5

Временная диаграмма синхронного обмена

6

Временная диаграмма асинхронного обмена

12

13.

Структура образовательного модуля – базовый курс (для студентов 1 курса)ПН

ВТ

СР

ЧТ

ПТ

СБ

ПН

ВТ

СР

ЧТ

ПТ

СБ

1 пара

Лекция

Лекция

Лекция

Лекция

Лекция

Лекция

Самост.

Самост.

Самост.

Самост.

Самост.

Инд.

2 пара

Лекция

Лекция

Лекция

Лекция

ЛБ

5

ЛБ

7

ЛБ

9

ЛБ

1

ЛБ

3

ЛБ

5

ЛБ

7

Инд.

3 пара

ЛБ

ЛБ

ЛБ

ЛБ

ЛБ

6

ЛБ

8

ЛБ

10

ЛБ

2

ЛБ

4

ЛБ

6

ЛБ

8

Зачет

4 пара

Самост.

Самост.

Самост.

Самост.

Самост.

1

Самост.

Самост.

Самост.

Самост.

Самост.

Самост.

13

14.

Структура образовательного модуля – базовый курс (для студентов 2 курса)ПН

ВТ

СР

ЧТ

ПТ

СБ

ПН

ВТ

СР

ЧТ

ПТ

СБ

1 пара

Лекция

Лекция

Лекция

Лекция

Лекция

Лекция

Лекция

Лекция

Лекция

Лекция

Лекция

Инд.

2 пара

Лекция

Лекция

Лекция

Лекция

ЛБ

5

ЛБ

7

ЛБ

9

ЛБ

1

ЛБ

3

ЛБ

5

ЛБ

7

Инд.

3 пара

ЛБ

ЛБ

ЛБ

ЛБ

ЛБ

6

ЛБ

8

ЛБ

10

ЛБ

2

ЛБ

4

ЛБ

6

ЛБ

8

Зачет

4 пара

Самост.

Самост.

Самост.

Самост.

Самост.

1

Самост.

Самост.

Самост.

Самост.

Самост.

Самост.

14

15.

Структура образовательного модуля – продвинутый курс (для студентов 2 курса)ПН

ВТ

9

21

ЛБ

2 пара

ЛБ 19/20

ЛБ 21/22

ЛБ 23/24

3 пара

ЛБ

ЛБ

ЛБ

4 пара

Самост.

22

Самост.

ЛБ

ЧТ

1 пара

20

ЛБ

СР

23

24

Самост.

ЛБ

ПТ

25

ПН

ВТ

СР

ЧТ

ПТ

СБ

27

ЛБ

ЛБ

30

ЛБ

31

ЛБ

32

ЛБ

34

ЛБ

35

Инд.

ЛБ 25/26

ЛБ 27/28

ЛБ

ЛБ

30

ЛБ

31

ЛБ 32/33

ЛБ

34

ЛБ 35/36

Инд.

ЛБ

ЛБ

ЛБ

ЛБ

30

ЛБ

31

ЛБ

ЛБ

34

ЛБ

26

Самост.

ЛБ

СБ

28

Самост.

29

Самост.

Самост.

Самост.

33

Самост.

Самост.

36

Экзамен

Самост.

Экзамен

15

16.

Учебный стенд ElmiCORE-H745-ЕК (Education Kit)16

17.

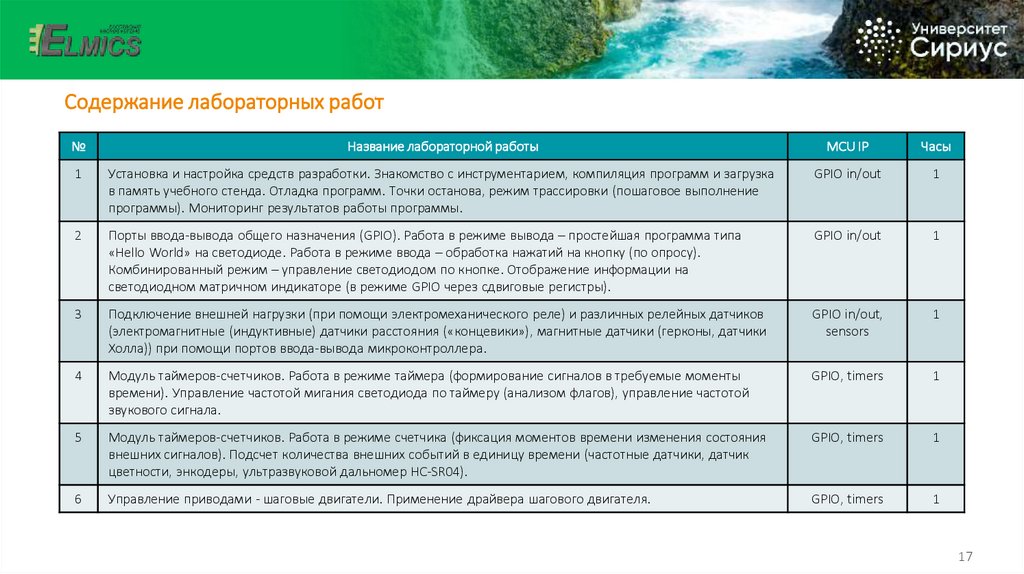

Содержание лабораторных работ№

Название лабораторной работы

MCU IP

Часы

1

Установка и настройка средств разработки. Знакомство с инструментарием, компиляция программ и загрузка

в память учебного стенда. Отладка программ. Точки останова, режим трассировки (пошаговое выполнение

программы). Мониторинг результатов работы программы.

GPIO in/out

1

2

Порты ввода-вывода общего назначения (GPIO). Работа в режиме вывода – простейшая программа типа

«Hello World» на светодиоде. Работа в режиме ввода – обработка нажатий на кнопку (по опросу).

Комбинированный режим – управление светодиодом по кнопке. Отображение информации на

светодиодном матричном индикаторе (в режиме GPIO через сдвиговые регистры).

GPIO in/out

1

3

Подключение внешней нагрузки (при помощи электромеханического реле) и различных релейных датчиков

(электромагнитные (индуктивные) датчики расстояния («концевики»), магнитные датчики (герконы, датчики

Холла)) при помощи портов ввода-вывода микроконтроллера.

GPIO in/out,

sensors

1

4

Модуль таймеров-счетчиков. Работа в режиме таймера (формирование сигналов в требуемые моменты

времени). Управление частотой мигания светодиода по таймеру (анализом флагов), управление частотой

звукового сигнала.

GPIO, timers

1

5

Модуль таймеров-счетчиков. Работа в режиме счетчика (фиксация моментов времени изменения состояния

внешних сигналов). Подсчет количества внешних событий в единицу времени (частотные датчики, датчик

цветности, энкодеры, ультразвуковой дальномер HC-SR04).

GPIO, timers

1

6

Управление приводами - шаговые двигатели. Применение драйвера шагового двигателя.

GPIO, timers

1

17

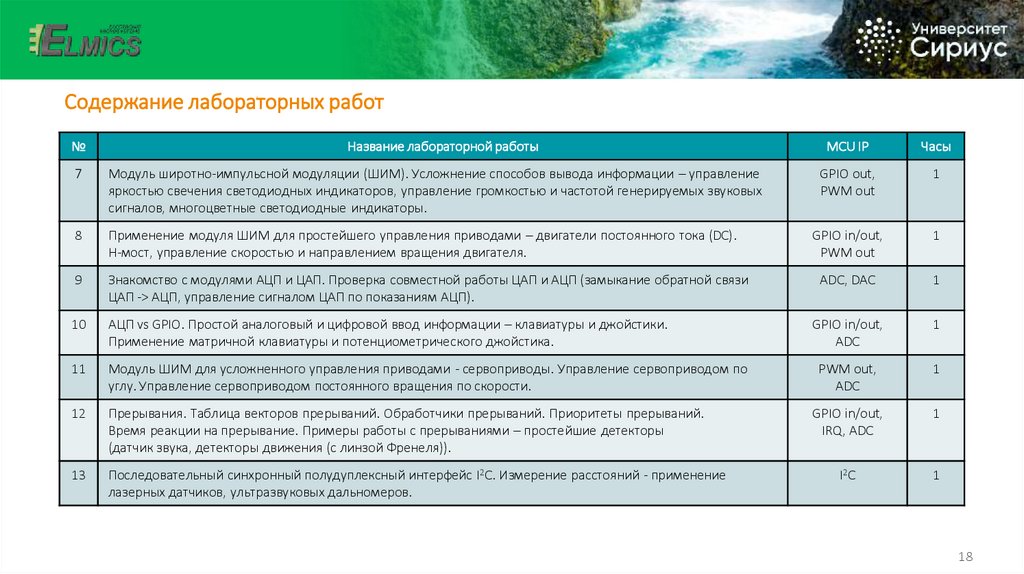

18.

Содержание лабораторных работ№

Название лабораторной работы

MCU IP

Часы

7

Модуль широтно-импульсной модуляции (ШИМ). Усложнение способов вывода информации – управление

яркостью свечения светодиодных индикаторов, управление громкостью и частотой генерируемых звуковых

сигналов, многоцветные светодиодные индикаторы.

GPIO out,

PWM out

1

8

Применение модуля ШИМ для простейшего управления приводами – двигатели постоянного тока (DC).

H-мост, управление скоростью и направлением вращения двигателя.

GPIO in/out,

PWM out

1

9

Знакомство с модулями АЦП и ЦАП. Проверка совместной работы ЦАП и АЦП (замыкание обратной связи

ЦАП -> АЦП, управление сигналом ЦАП по показаниям АЦП).

ADC, DAC

1

10

АЦП vs GPIO. Простой аналоговый и цифровой ввод информации – клавиатуры и джойстики.

Применение матричной клавиатуры и потенциометрического джойстика.

GPIO in/out,

ADC

1

11

Модуль ШИМ для усложненного управления приводами - сервоприводы. Управление сервоприводом по

углу. Управление сервоприводом постоянного вращения по скорости.

PWM out,

ADC

1

12

Прерывания. Таблица векторов прерываний. Обработчики прерываний. Приоритеты прерываний.

Время реакции на прерывание. Примеры работы с прерываниями – простейшие детекторы

(датчик звука, детекторы движения (с линзой Френеля)).

GPIO in/out,

IRQ, ADC

1

13

Последовательный синхронный полудуплексный интерфейс I2C. Измерение расстояний - применение

лазерных датчиков, ультразвуковых дальномеров.

I2C

1

18

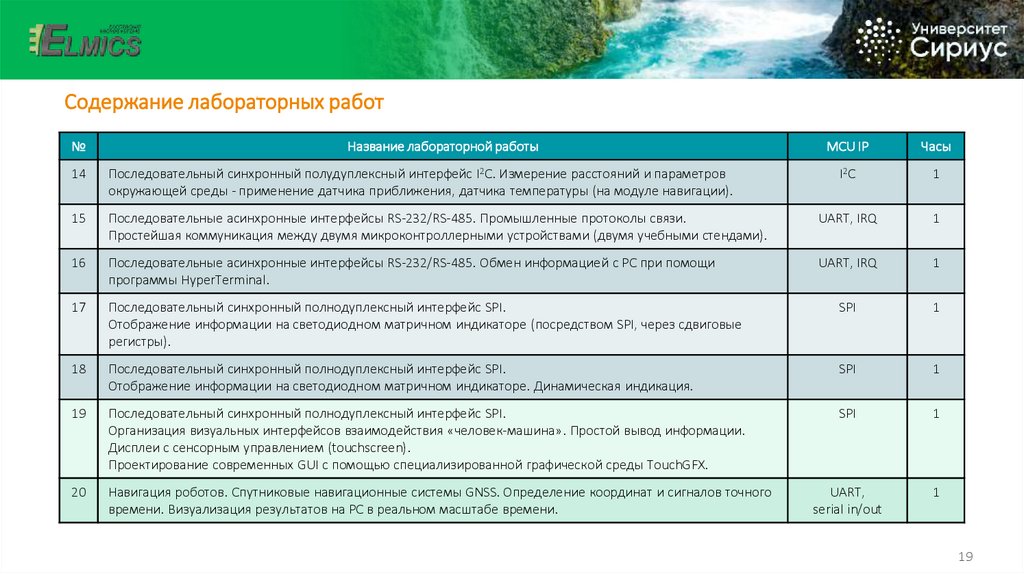

19.

Содержание лабораторных работ№

Название лабораторной работы

MCU IP

Часы

I2C

1

14

Последовательный синхронный полудуплексный интерфейс I2C. Измерение расстояний и параметров

окружающей среды - применение датчика приближения, датчика температуры (на модуле навигации).

15

Последовательные асинхронные интерфейсы RS-232/RS-485. Промышленные протоколы связи.

Простейшая коммуникация между двумя микроконтроллерными устройствами (двумя учебными стендами).

UART, IRQ

1

16

Последовательные асинхронные интерфейсы RS-232/RS-485. Обмен информацией с PC при помощи

программы HyperTerminal.

UART, IRQ

1

17

Последовательный синхронный полнодуплексный интерфейс SPI.

Отображение информации на светодиодном матричном индикаторе (посредством SPI, через сдвиговые

регистры).

SPI

1

18

Последовательный синхронный полнодуплексный интерфейс SPI.

Отображение информации на светодиодном матричном индикаторе. Динамическая индикация.

SPI

1

19

Последовательный синхронный полнодуплексный интерфейс SPI.

Организация визуальных интерфейсов взаимодействия «человек-машина». Простой вывод информации.

Дисплеи с сенсорным управлением (touchscreen).

Проектирование современных GUI с помощью специализированной графической среды TouchGFX.

SPI

1

20

Навигация роботов. Спутниковые навигационные системы GNSS. Определение координат и сигналов точного

времени. Визуализация результатов на PC в реальном масштабе времени.

UART,

serial in/out

1

19

20.

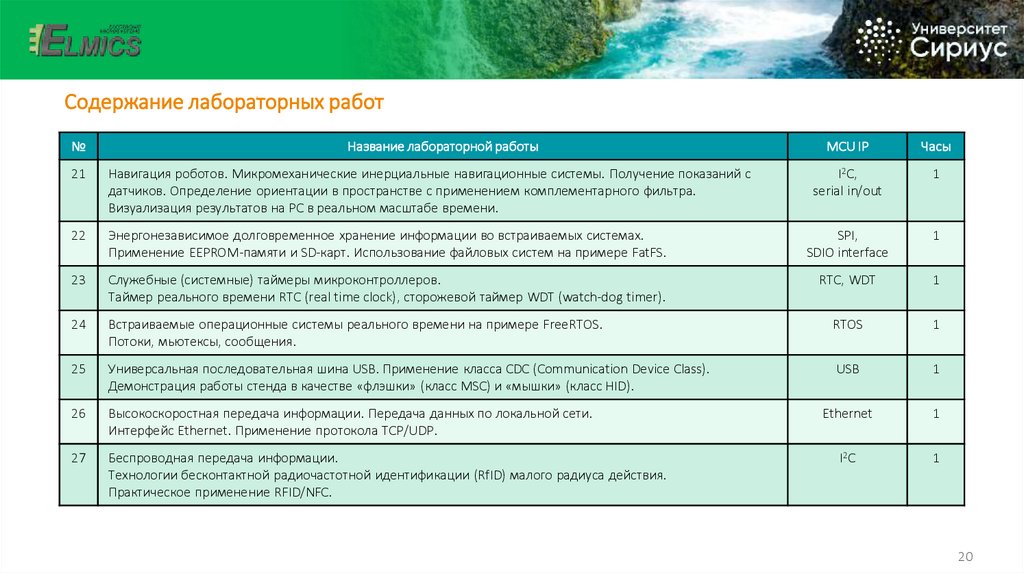

Содержание лабораторных работ№

Название лабораторной работы

MCU IP

Часы

21

Навигация роботов. Микромеханические инерциальные навигационные системы. Получение показаний с

датчиков. Определение ориентации в пространстве с применением комплементарного фильтра.

Визуализация результатов на PC в реальном масштабе времени.

I2C,

serial in/out

1

22

Энергонезависимое долговременное хранение информации во встраиваемых системах.

Применение EEPROM-памяти и SD-карт. Использование файловых систем на примере FatFS.

SPI,

SDIO interface

1

23

Служебные (системные) таймеры микроконтроллеров.

Таймер реального времени RTC (real time clock), сторожевой таймер WDT (watch-dog timer).

RTC, WDT

1

24

Встраиваемые операционные системы реального времени на примере FreeRTOS.

Потоки, мьютексы, сообщения.

RTOS

1

25

Универсальная последовательная шина USB. Применение класса CDC (Communication Device Class).

Демонстрация работы стенда в качестве «флэшки» (класс MSC) и «мышки» (класс HID).

USB

1

26

Высокоскоростная передача информации. Передача данных по локальной сети.

Интерфейс Ethernet. Применение протокола TCP/UDP.

Ethernet

1

27

Беспроводная передача информации.

Технологии бесконтактной радиочастотной идентификации (RfID) малого радиуса действия.

Практическое применение RFID/NFC.

I2C

1

20

21.

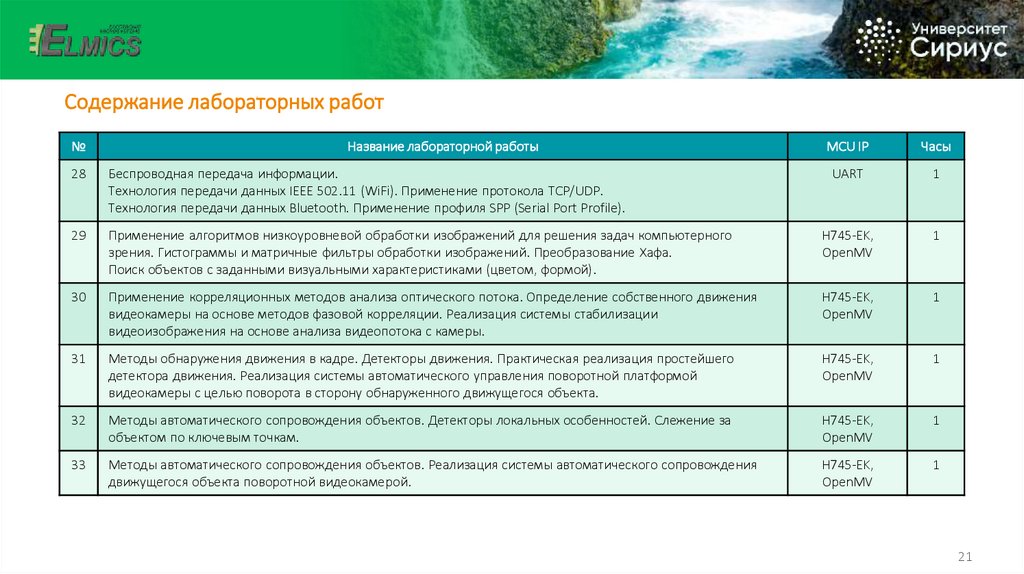

Содержание лабораторных работ№

Название лабораторной работы

MCU IP

Часы

UART

1

28

Беспроводная передача информации.

Технология передачи данных IEEE 502.11 (WiFi). Применение протокола TCP/UDP.

Технология передачи данных Bluetooth. Применение профиля SPP (Serial Port Profile).

29

Применение алгоритмов низкоуровневой обработки изображений для решения задач компьютерного

зрения. Гистограммы и матричные фильтры обработки изображений. Преобразование Хафа.

Поиск объектов с заданными визуальными характеристиками (цветом, формой).

H745-EK,

OpenMV

1

30

Применение корреляционных методов анализа оптического потока. Определение собственного движения

видеокамеры на основе методов фазовой корреляции. Реализация системы стабилизации

видеоизображения на основе анализа видеопотока с камеры.

H745-EK,

OpenMV

1

31

Методы обнаружения движения в кадре. Детекторы движения. Практическая реализация простейшего

детектора движения. Реализация системы автоматического управления поворотной платформой

видеокамеры с целью поворота в сторону обнаруженного движущегося объекта.

H745-EK,

OpenMV

1

32

Методы автоматического сопровождения объектов. Детекторы локальных особенностей. Слежение за

объектом по ключевым точкам.

H745-EK,

OpenMV

1

33

Методы автоматического сопровождения объектов. Реализация системы автоматического сопровождения

движущегося объекта поворотной видеокамерой.

H745-EK,

OpenMV

1

21

22.

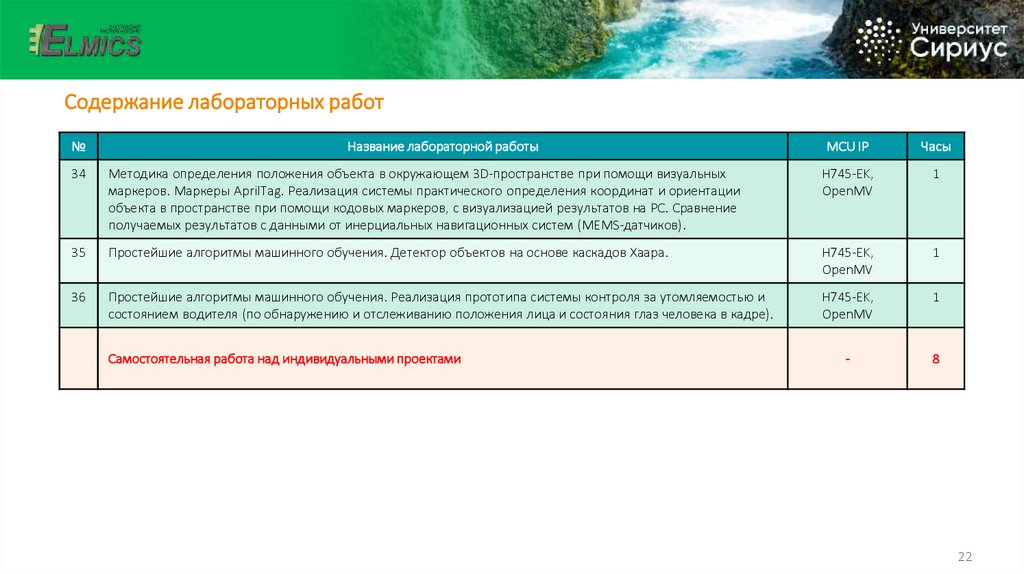

Содержание лабораторных работ№

Название лабораторной работы

MCU IP

Часы

34

Методика определения положения объекта в окружающем 3D-пространстве при помощи визуальных

маркеров. Маркеры AprilTag. Реализация системы практического определения координат и ориентации

объекта в пространстве при помощи кодовых маркеров, с визуализацией результатов на PC. Сравнение

получаемых результатов с данными от инерциальных навигационных систем (MEMS-датчиков).

H745-EK,

OpenMV

1

35

Простейшие алгоритмы машинного обучения. Детектор объектов на основе каскадов Хаара.

H745-EK,

OpenMV

1

36

Простейшие алгоритмы машинного обучения. Реализация прототипа системы контроля за утомляемостью и

состоянием водителя (по обнаружению и отслеживанию положения лица и состояния глаз человека в кадре).

H745-EK,

OpenMV

1

-

8

Самостоятельная работа над индивидуальными проектами

22

23.

Что такое «встраиваемая система управления» ?Встраиваемая система управления (Embedded Control System) :

Это любая механическая или электрическая система, имеющая в своем составе блок управления,

выполненный на основе специализированного вычислительного устройства (СВУ), и функционирующая,

будучи физически встроенной (интегрированной) непосредственно в объект управления (устройство),

которым она управляет.

Специализированное вычислительное устройство (СВУ) :

Это вычислительное устройство, предназначенное для решения заранее определенного узкого класса

задач, что достигается с помощью :

• аппаратной реализации вычислительных алгоритмов;

• использования серийных вычислительных средств совместно со специализированной подсистемой

ввода-вывода, учитывающей конкретный состав объекта управления и датчиков первичной информации;

• разработки специализированного программного обеспечения.

23

24.

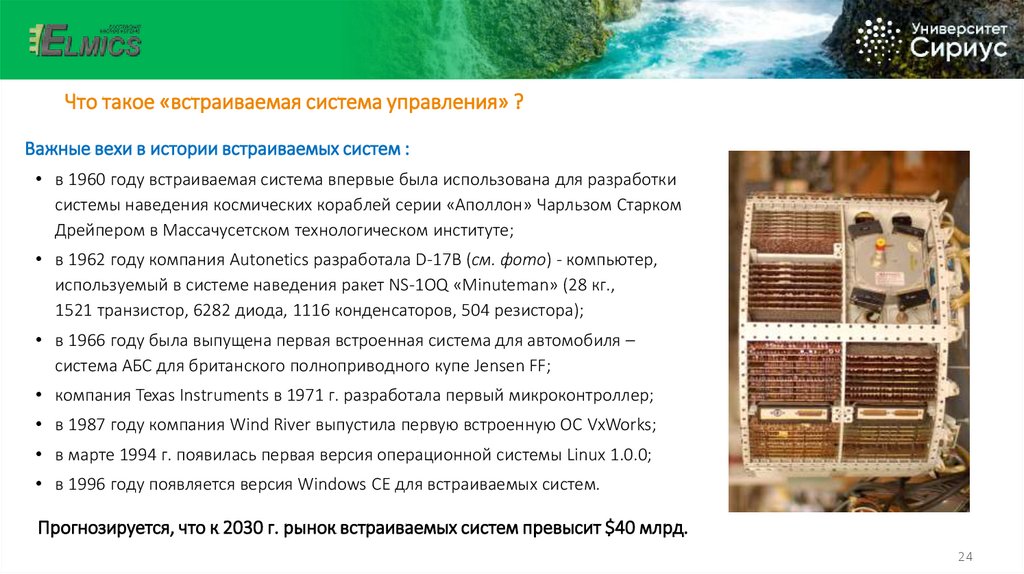

Что такое «встраиваемая система управления» ?Важные вехи в истории встраиваемых систем :

• в 1960 году встраиваемая система впервые была использована для разработки

системы наведения космических кораблей серии «Аполлон» Чарльзом Старком

Дрейпером в Массачусетском технологическом институте;

• в 1962 году компания Autonetics разработала D-17B (см. фото) - компьютер,

используемый в системе наведения ракет NS-1OQ «Minuteman» (28 кг.,

1521 транзистор, 6282 диода, 1116 конденсаторов, 504 резистора);

• в 1966 году была выпущена первая встроенная система для автомобиля –

система АБС для британского полноприводного купе Jensen FF;

• компания Texas Instruments в 1971 г. разработала первый микроконтроллер;

• в 1987 году компания Wind River выпустила первую встроенную ОС VxWorks;

• в марте 1994 г. появилась первая версия операционной системы Linux 1.0.0;

• в 1996 году появляется версия Windows CE для встраиваемых систем.

Прогнозируется, что к 2030 г. рынок встраиваемых систем превысит $40 млрд.

24

25.

Что такое «встраиваемая система управления» ?Основные характерные особенности встраиваемых систем :

• ориентирована на выполнение конкретной

задачи или набора задач;

• должна функционировать в соответствии с

темпом протекания физических процессов

в системе управления;

• обладает высокой отказоустойчивостью и

надежностью;

• отличается прогнозируемостью поведения и

стабильностью в процессе функционирования;

• энергоэффективная (малопотребляющая);

• имеет минимальный интерфейс с пользователем;

• оптимизирована по основным видам ресурсов и цене.

25

26.

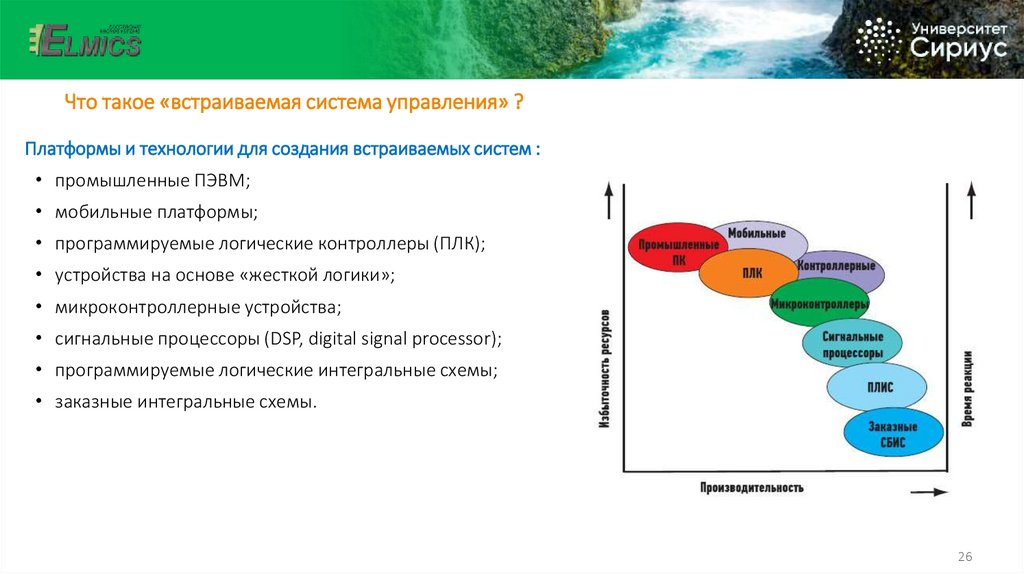

Что такое «встраиваемая система управления» ?Платформы и технологии для создания встраиваемых систем :

• промышленные ПЭВМ;

• мобильные платформы;

• программируемые логические контроллеры (ПЛК);

• устройства на основе «жесткой логики»;

• микроконтроллерные устройства;

• сигнальные процессоры (DSP, digital signal processor);

• программируемые логические интегральные схемы;

• заказные интегральные схемы.

26

27.

Системы на «жесткой логике»Системы на базе «жесткой логики» - являются традиционными вычислительными системами, в которых

алгоритмы обработки и хранения информации жестко связаны со схемотехнической реализацией системы.

Любая система, построенная на базе «жесткой логики», обязательно является узко специализированной,

предназначенной для решения исключительно одной или (реже) нескольких заранее определенных задач.

Изменение алгоритмов функционирования в системах на базе «жесткой логики» возможно только путем

изменения структуры самой системы, замены электронных узлов, входящих в нее, и / или связей между ними.

Современные системы на «жесткой логике» выполняются на основе :

• интегральных схем с различной степенью интеграции (ИС, IC – integrated circuit);

• базовых матричных кристаллов (БМК, ULA – uncommitted logic array);

• программируемых логических интегральных схем (ПЛИС : PAL – programmable array logic,

CPLD – complex programmable logic device, FPGA - field-programmable gate array);

• интегральных схем специализированного применения (ASIC, application-specific integrated circuit).

27

28.

Системы на «жесткой логике»Основные преимущества систем на «жесткой логике» :

• отсутствие избыточности;

Система на «жесткой логике», если она грамотно спроектирована – практически не имеет аппаратурной

избыточности (в отличие от универсальных систем), так как каждый ее элемент работает в полную силу.

• максимально высокое быстродействие;

Скорость выполнения алгоритмов обработки информации в системах на «жесткой логике» определяется

только быстродействием отдельных логических элементов и выбранной схемой путей прохождения и

обработки информации.

Основным значительным недостатком систем на «жесткой логике» является то, что для каждой новой

задачи их надо проектировать и изготавливать заново, что является достаточно длительным и дорогостоящим

процессом, требующем высокой квалификации исполнителей.

И если решаемая задача вдруг изменяется, то вся аппаратура должна быть полностью заменена.

28

29.

Системы на «жесткой логике»Примеры вычислительных устройств на основе «жесткой логики» :

29

30.

Программируемые системыПрограммируемые системы - являются универсальными вычислительными системами, которые могут

адаптироваться под любую задачу, перестраиваться с одного алгоритма работы на другой без необходимости

в изменении аппаратуры или схемотехники системы.

Современные встраиваемые системы чаще всего выполнены как раз на основе аппаратных платформ,

подразумевающих возможность их программируемости (программного управления) и построенных на базе :

• микроконтроллеров (МК, MCU - microcontroller unit);

• микропроцессоров (МП, MPU - microprocessor unit);

• цифровых сигнальных процессоров (ЦСП, DSP - digital signal processor);

• «систем на кристалле» (СнК, SoC - system-on-chip);

• «систем в одном корпусе» (SiP - system-in-package).

30

31.

Программируемые системыОсновными недостатками программируемых систем, по сравнению с «жесткой логикой», являются :

• избыточность;

Чем проще решаемая задача, тем больше будет избыточность и тем менее оправданной становится

универсальность. Избыточность приводит к увеличению стоимости системы, снижению надежности,

увеличению потребляемой мощности и массогабаритных характеристик, и т.д.

• снижение быстродействия;

Чем больше универсальность и гибкость системы, тем меньше ее быстродействие.

Оптимизировать универсальную систему так, чтобы каждая новая задача решалась в ней максимально

быстро - невозможно. Для универсальных систем не существует таких задач (пусть даже и самых простых),

которые они решали бы с максимально возможным быстродействием.

Основным значительным достоинством программируемых систем является возможность решения

различных задач без необходимости в изменении архитектуры или схемотехники системы.

31

32.

Программируемые системыПримеры программируемых вычислительных устройств :

32

33.

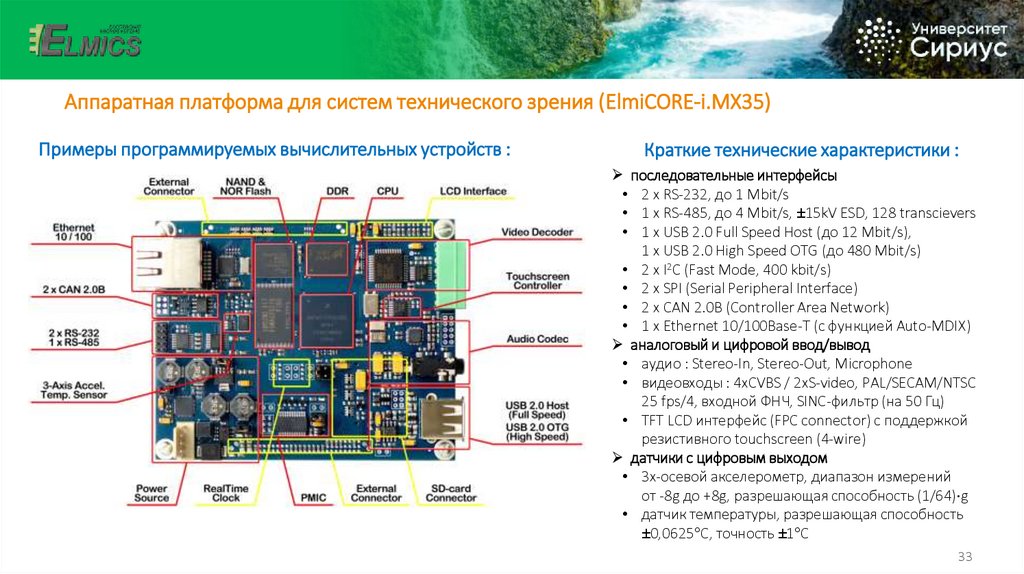

Аппаратная платформа для систем технического зрения (ElmiCORE-i.MX35)Примеры программируемых вычислительных устройств :

Краткие технические характеристики :

последовательные интерфейсы

• 2 x RS-232, до 1 Mbit/s

• 1 x RS-485, до 4 Mbit/s, ±15kV ESD, 128 transcievers

• 1 x USB 2.0 Full Speed Host (до 12 Mbit/s),

1 x USB 2.0 High Speed OTG (до 480 Mbit/s)

• 2 x I2C (Fast Mode, 400 kbit/s)

• 2 x SPI (Serial Peripheral Interface)

• 2 x CAN 2.0B (Controller Area Network)

• 1 x Ethernet 10/100Base-T (с функцией Auto-MDIX)

аналоговый и цифровой ввод/вывод

• аудио : Stereo-In, Stereo-Out, Microphone

• видеовходы : 4xCVBS / 2xS-video, PAL/SECAM/NTSC

25 fps/4, входной ФНЧ, SINC-фильтр (на 50 Гц)

• TFT LCD интерфейс (FPC connector) с поддержкой

резистивного touchscreen (4-wire)

датчики с цифровым выходом

• 3х-осевой акселерометр, диапазон измерений

от -8g до +8g, разрешающая способность (1/64) g

• датчик температуры, разрешающая способность

±0,0625 С, точность ±1 С

33

34.

Аппаратная платформа для систем технического зрения (ElmiCORE-i.MX35)NAND

Flash

2 GByte

MCU

PIC16F883

NOR

Flash

64 MByte

1.8V

3.3V

buffer

MobileDDR

SDRAM

128 MByte

Real Time

Clock &

NV RAM

контроллер

управления

ВИП

VBAT

t°C

sensor

NAND Flash

Addr / Data

Bus

NOR Flash

Data

Bus

Memory interface

Address

Bus

Accelerometer

SDRAM

Data Bus

ВИП

CPU

+3 ,3 В

+3 ,3 B

(I/O )

+1 ,8 В

+1 ,8 B

(MEM)

+1 ,55 В

+1 ,55 B

(CORE)

+1 ,5 В

+1 ,5 B

(PL L)

+1 ,3 В

+1 ,3 B

(SRAM)

Входное

напр яжение

питания

CVBS

Decoder

Data Bus

вторичные

источники

питания

ARM1136JF-S

I2S

interface

Line Ou t

TFT LCD

controller

CAN 2.0B

controller

SD-card

connector

Etherne t

PHY

CAN 2.0B

PHY

UART

controller

Etherne t

RJ-45

2x

CAN 2.0B

Audio

Line In

Codec

Headp hones

MIC

USB 2.0

controller

USB HS OTG

USB

Typ e A

USB FS Host

PLD-6

TouchScreen

controller

4-Wire

1 x RS-485

2 x RS-232

+12V, DC

SD/MMC

card

CVBS

CVBS

532 MHz

Ethernet

10/100

CVBS

Decoder

I2C

interface

Freescale i.MX356

SD-card

controller

Video

1x

RS-485

2x

RS-232

TFT LCD

interface

Краткие технические характеристики :

процессорный элемент

• Freescale i.MX35, ядро ARM1136JF-S, 532 МГц, 32-bit;

• 16kB L1 кэш данных, 16kB L1, 128kB L2 кэш команд;

• сопроцессор работы с плавающей точкой FPU;

• модуль обработки графики OpenVG 1.1 GPU;

• модуль аппаратной обработки видеоизображений

IPU (Image Processing Unit);

• режимы wait, doze, sleep, power-down;

устройства памяти

• 128kB внутренней памяти SRAM (Static RAM) в CPU;

• до 128MB памяти программ типа NOR Flash;

• до 2GB памяти программ типа NAND Flash;

• до 256MB Mobile DDR SDRAM;

периферийные устройства SoC

• часы реального времени (RTC) с NV RAM;

• таймер-толкач Watch-Dog-Timer (WDT);

поддерживаемые устройства хранения информации

• карты памяти типа SD/MMC/RS-MMC/MMCplus;

системное программное обеспечение

• ОС Linux 2.6.38, ОС QNX Neutrino 6.4.x

34

35.

Особенности СВУ для встраиваемых систем управления1. Работа в реальном масштабе времени (система должна производить определенные вычисления и выработку сигналов

управления за строго детерминированные временные интервалы, соответствующие темпу протекания процессов в

объекте управления).

2. Наличие интерфейса взаимодействия с пользователем и интерфейсов сопряжения с объектом управления.

3. Формирование выходных сигналов с определенной точностью, с целью обеспечения качества управления и

устойчивости системы (контура управления).

4. Минимальное собственное энергопотребление (возможно, автономное питание).

5. Предусмотренные способы отвода тепла (охлаждения) обеспечивают минимум требований тепловых режимов

(минимизация плотности теплового потока).

6. Собственная защита (корпус) - минимальна, определяется примененными элементами, прочностью и жесткостью

конструкции, обеспечивая минимальные габаритные размеры и массу.

7. Предъявляются требования по стойкости к внешним воздействующим факторам (механические, климатические

(природные), биологические, радиационные, химические (специальные среды) факторы и электромагнитные поля).

8. Предъявляются жесткие требования по надежности и безотказности функционирования (к средней наработке на

отказ, MTBF – mean operating time between failures).

35

36.

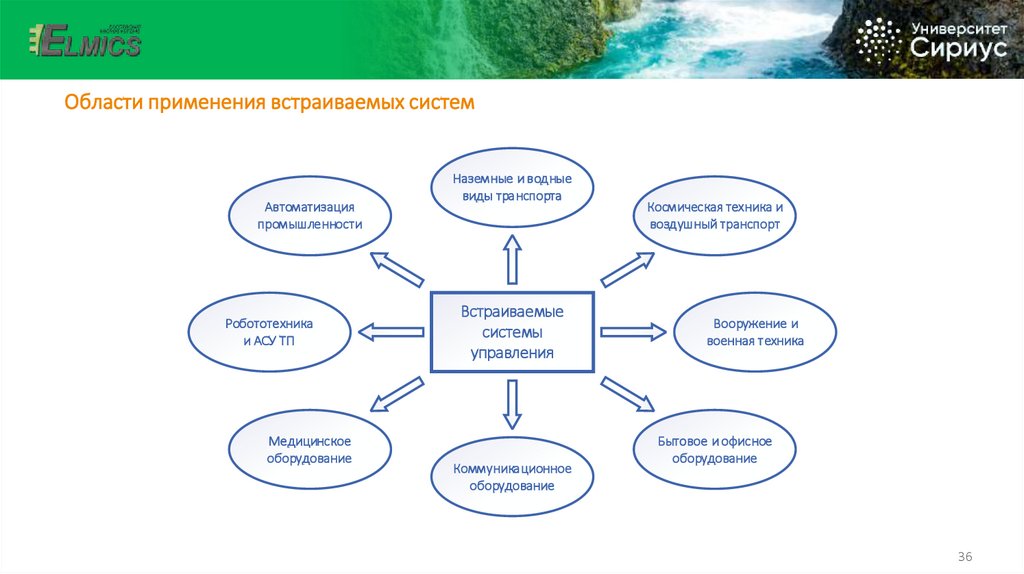

Области применения встраиваемых системАвтоматизация

промышленности

Робототехника

и АСУ ТП

Медицинское

оборудование

Наземные и водные

виды транспорта

Встраиваемые

системы

управления

Коммуникационное

оборудование

Космическая техника и

воздушный транспорт

Вооружение и

военная техника

Бытовое и офисное

оборудование

36

37.

Примеры встраиваемых системАвтоматизация

промышленности

Робототехника

и АСУ ТП

Медицинское

оборудование

Наземные и водные

виды транспорта

Встраиваемые

системы

управления

Коммуникационное

оборудование

Космическая техника и

воздушный транспорт

Вооружение и

военная техника

Бытовое и офисное

оборудование

37

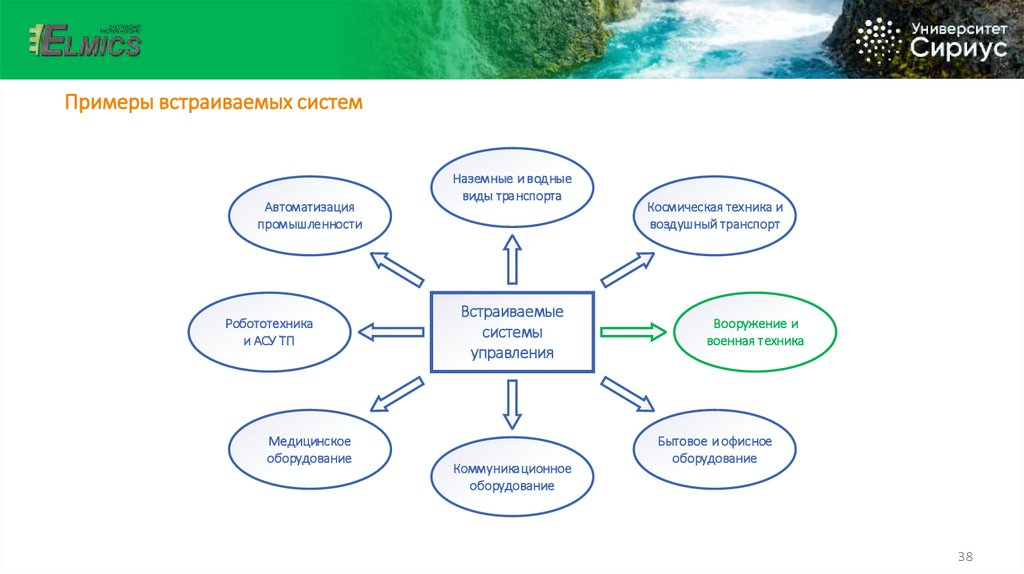

38.

Примеры встраиваемых системАвтоматизация

промышленности

Робототехника

и АСУ ТП

Медицинское

оборудование

Наземные и водные

виды транспорта

Встраиваемые

системы

управления

Коммуникационное

оборудование

Космическая техника и

воздушный транспорт

Вооружение и

военная техника

Бытовое и офисное

оборудование

38

39.

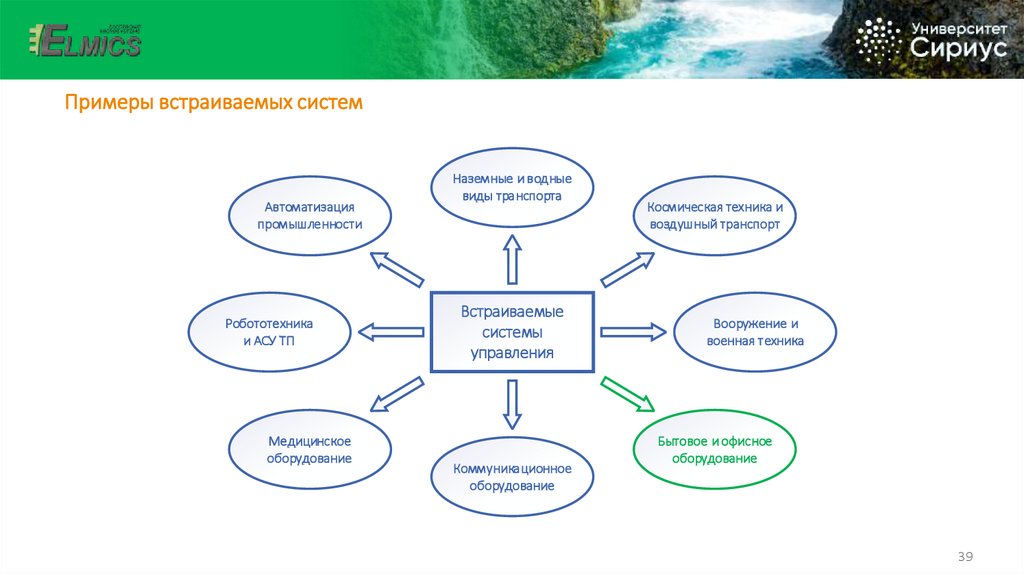

Примеры встраиваемых системАвтоматизация

промышленности

Робототехника

и АСУ ТП

Медицинское

оборудование

Наземные и водные

виды транспорта

Встраиваемые

системы

управления

Коммуникационное

оборудование

Космическая техника и

воздушный транспорт

Вооружение и

военная техника

Бытовое и офисное

оборудование

39

40.

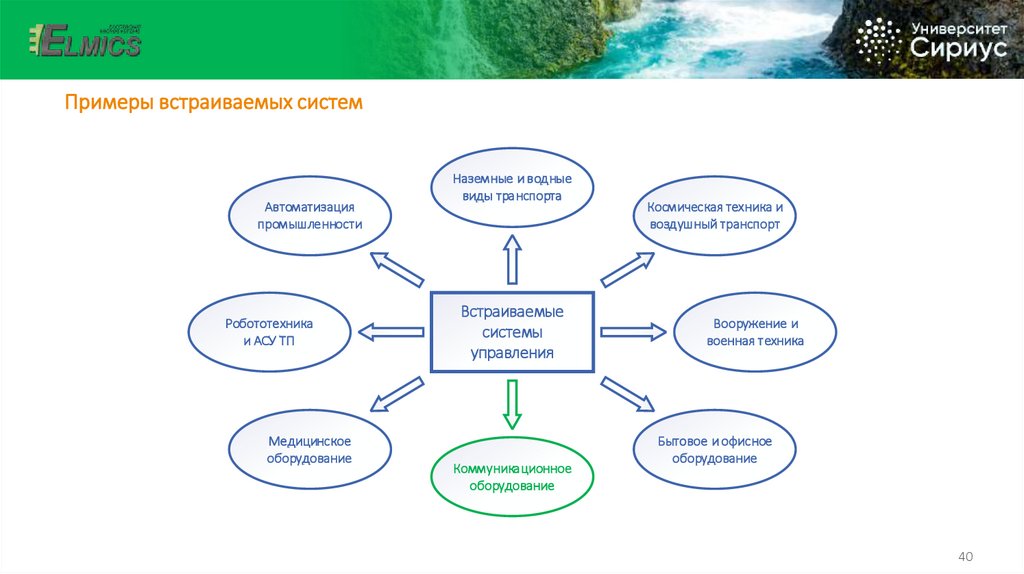

Примеры встраиваемых системАвтоматизация

промышленности

Робототехника

и АСУ ТП

Медицинское

оборудование

Наземные и водные

виды транспорта

Встраиваемые

системы

управления

Коммуникационное

оборудование

Космическая техника и

воздушный транспорт

Вооружение и

военная техника

Бытовое и офисное

оборудование

40

41.

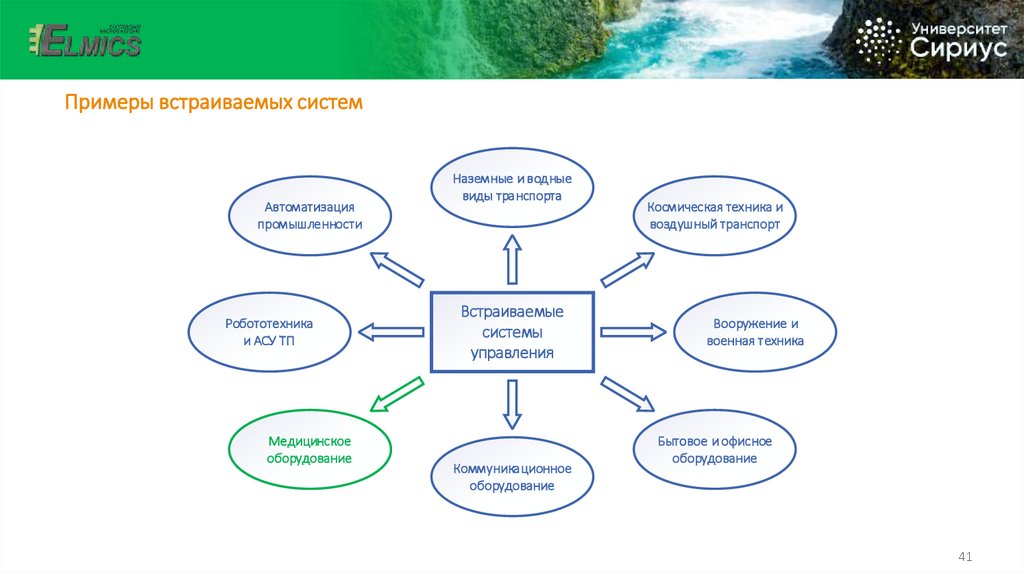

Примеры встраиваемых системАвтоматизация

промышленности

Робототехника

и АСУ ТП

Медицинское

оборудование

Наземные и водные

виды транспорта

Встраиваемые

системы

управления

Коммуникационное

оборудование

Космическая техника и

воздушный транспорт

Вооружение и

военная техника

Бытовое и офисное

оборудование

41

42.

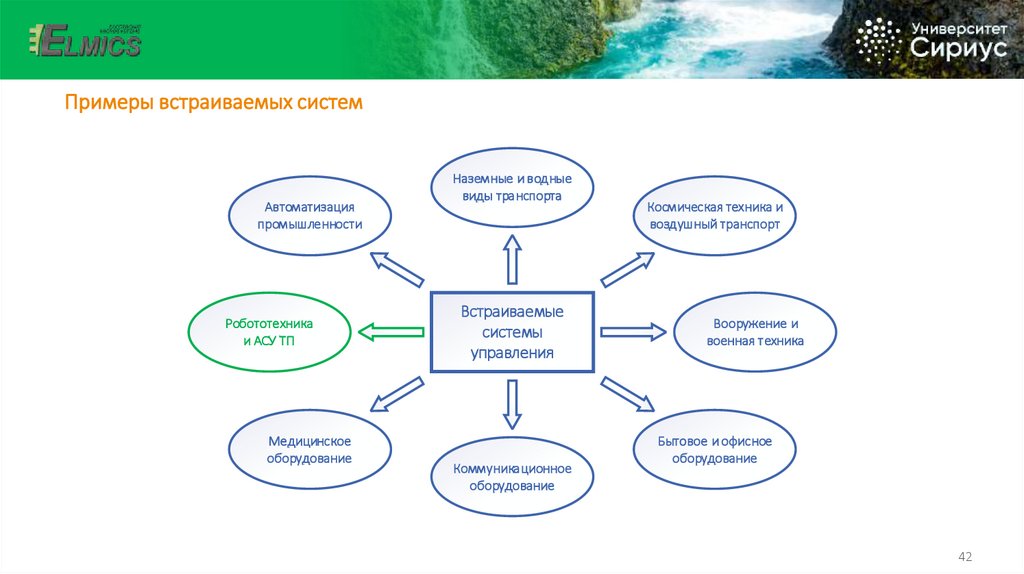

Примеры встраиваемых системАвтоматизация

промышленности

Робототехника

и АСУ ТП

Медицинское

оборудование

Наземные и водные

виды транспорта

Встраиваемые

системы

управления

Коммуникационное

оборудование

Космическая техника и

воздушный транспорт

Вооружение и

военная техника

Бытовое и офисное

оборудование

42

43.

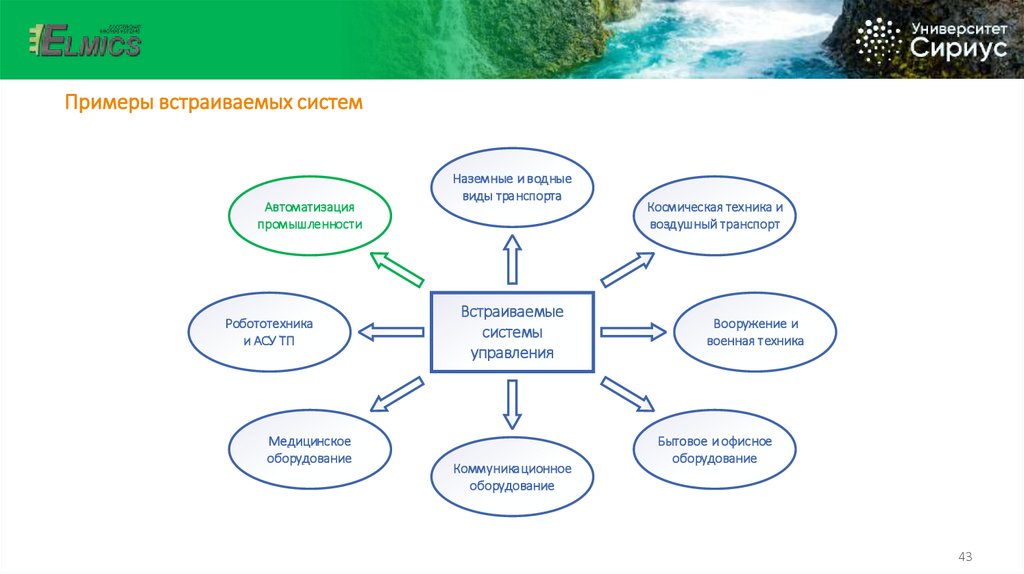

Примеры встраиваемых системАвтоматизация

промышленности

Робототехника

и АСУ ТП

Медицинское

оборудование

Наземные и водные

виды транспорта

Встраиваемые

системы

управления

Коммуникационное

оборудование

Космическая техника и

воздушный транспорт

Вооружение и

военная техника

Бытовое и офисное

оборудование

43

44.

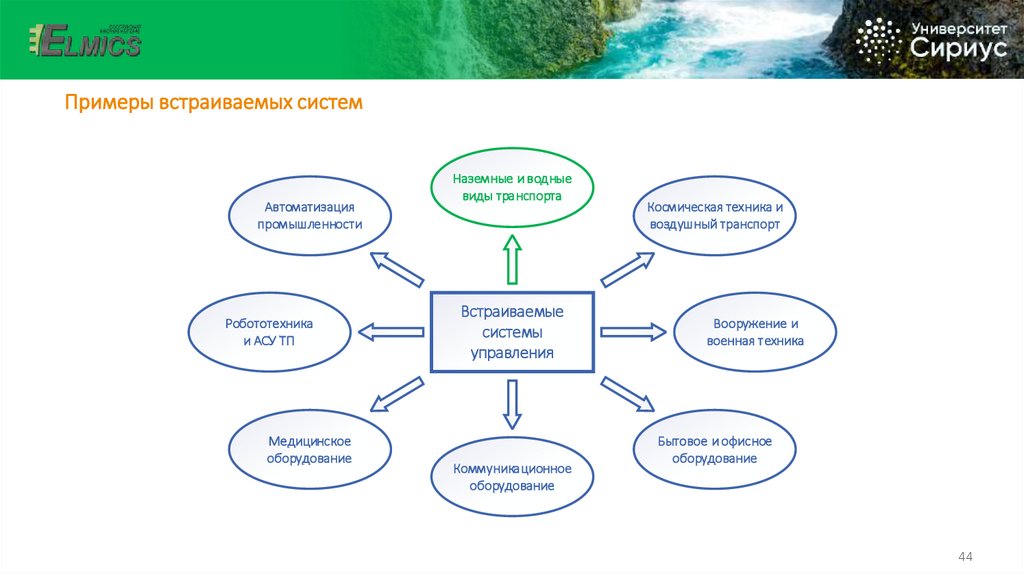

Примеры встраиваемых системАвтоматизация

промышленности

Робототехника

и АСУ ТП

Медицинское

оборудование

Наземные и водные

виды транспорта

Встраиваемые

системы

управления

Коммуникационное

оборудование

Космическая техника и

воздушный транспорт

Вооружение и

военная техника

Бытовое и офисное

оборудование

44

45.

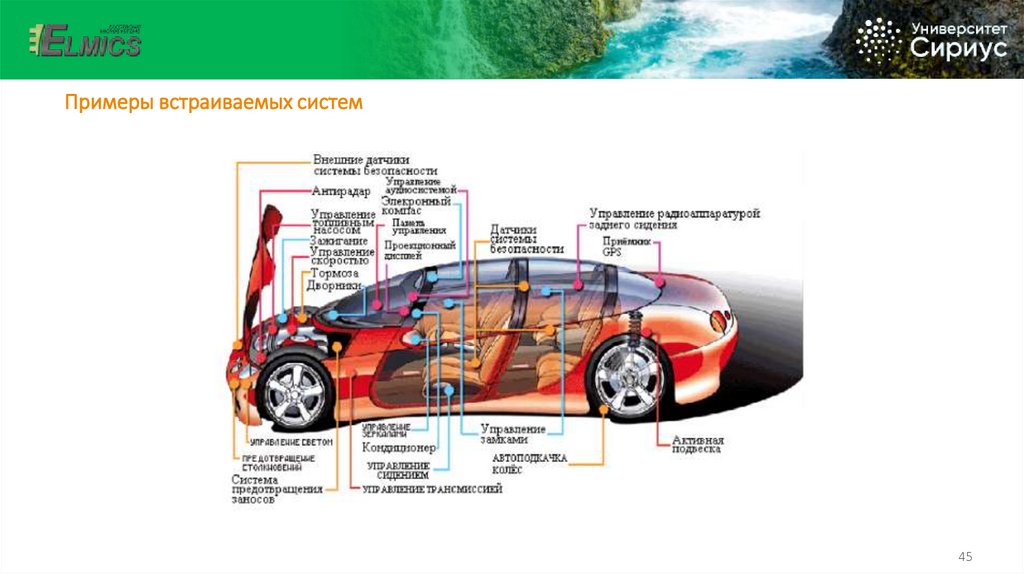

Примеры встраиваемых систем45

46.

Системный подход к проектированию встраиваемых системВо всем должна быть систематизированная систематическая система.

Ярослав Гашек, «Похождения бравого солдата Швейка», 1921 г.

При проектировании отдельных элементов встраиваемой системы управления (в т.ч. и вычислительных

средств) необходимо учитывать их взаимное влияние друг на друга в составе всего комплекса, т.е. применять

системный подход.

Требуется учитывать такие особенности современных сложных систем, как :

• многофункциональный характер управления;

• большое количество составных частей, действия которых в значительной мере взаимообусловлены;

• наличие общей цели функционирования, сложным образом связанной с частными целями функционирования

отдельных подсистем;

• воздействие большого числа случайных факторов на процессы проектирования, изготовления и эксплуатации;

• сложный характер эксплуатации, в ходе которой, возможно, изменяются условия функционирования;

• необходимость учета экономических факторов при построении системы.

46

47.

Системный подход к проектированию встраиваемых системОсновные принципы системного подхода :

• проектирование системы должно быть комплексным (т.е. необходимо максимальным образом

анализировать связи, существующие как в объекте управления, так и в управляющей системе);

• процесс проектирования должен иметь иерархическую структуру (это определяет последовательность

анализа объекта и системы управления при проектировании : анализ системы должен начинаться с выхода

системы, рассматриваемой как единое целое; затем система разбивается на небольшое количество

достаточно крупных подсистем и исследуется вклад каждой из них в выход системы).

Такой подход позволяет устанавливать требования к характеристикам элементов системы управления

по заданным требованиям к качеству функционирования всего комплекса в целом;

• проектирование системы должно осуществляться при помощи метода декомпозиции (разбиение целого

на отдельные составные части с целью исследования этих частей независимо друг от друга);

47

48.

Системный подход к проектированию встраиваемых системОсновные принципы системного подхода :

• проектирование системы - итерационный процесс (на первом этапе не рассматриваются второстепенные

факторы; применяются приближенные методы и оценки, чтобы изучить и понять главные характеристики

системы; затем второстепенные факторы учитываются, что позволяет сделать некоторые уточнения, и т.д.).

Необходимость этого принципа объясняется неполным объемом исходных данных в начале проектирования,

а также их частичной недостоверностью.

Эти обстоятельства - следствие новизны разработки и чем больше изменений закладывается в систему по

сравнению с предыдущими модификациями, тем дольше будет выполняться этот итерационный процесс;

• при проектировании следует предусмотреть свойство открытости системы (не стоит стремиться делать

систему абсолютно и навсегда законченной; ее стоит сделать подходящей для решения текущих

поставленных задач, но необходимо также предусмотреть возможность ее дальнейшего развития,

совершенствования и модернизации).

48

49.

Системный подход к проектированию встраиваемых системВ первую очередь, необходима правильная постановка задачи, состоящая из следующих элементов :

• описание окружения задачи;

В процессе разработки системы управления проектировщик изучает материалы, не связанные с разработкой только лишь

специализированного вычислительного устройства, а описывающие те предметные области, от понимания законов которых

будет зависеть качество разрабатываемой системы.

• интересы, которым должна служить задача;

Задача проектирования системы управления является практической задачей, возникающей вследствие потребности в такого

рода системах для тех или иных объектов. Поэтому разработчик в начале своей работы должен решить, в чем же заключается

основная потребность в такого рода комплексах.

• область допустимых и желательных решений;

В процессе поиска решения разработчик системы выделяет для себя определенный класс допустимых решений из всего

множества существующих вариантов, и именно среди элементов этого класса и производится дальнейший поиск желательных

решений, так как в силу тех или иных обстоятельств не все из допустимых вариантов построения системы являются

желательными.

• критерий эффективности, согласно которому должна производиться оценка предлагаемых решений;

Критерием качества системы управления является эффективность выполнения этой системой своей основной задачи.

49

50.

Системный подход к проектированию встраиваемых системЗатем, необходимо решение задач анализа и синтеза (проектирования) структуры системы управления,

как единого целого.

При анализе системы :

Определяются составляющие ее элементы и некоторый набор исходных параметров.

При синтезе системы :

Определяются взаимосвязи отдельных блоков системы и обобщенные показатели ее качества.

Для определения многоуровневой модели структуры системы управления используются основные

положения общей теории систем и теории иерархических многоуровневых систем.

При таком подходе, система управления представляется в виде совокупности взаимосвязанных элементов

(подсистем), технические средства рассматриваются как элементы системы, а совокупность выполняемых ими

функций – как цель их функционирования.

50

51.

Проектирование СВУ для встраиваемых систем – алгоритмический синтезНа основании требований к условиям применения объекта, алгоритмов, подлежащих к реализации

на проектируемом вычислительном устройстве, заданной точности решения задач и условий взаимосвязи

вычислительного устройства с объектом управления - разрабатываются математические описания задач,

подлежащих к реализации на проектируемом вычислительном устройстве, а также определяются основные

характеристики этого устройства.

На этапе алгоритмического синтеза предварительно определяется структура входной информации и

последовательность ее преобразования в вычислительном устройстве, что позволяет задать и описать функции

подсистемы ввода-вывода, количество каналов информационного обмена между внешними источниками и

вычислительным устройством, а также количество каналов связи проектируемого вычислительного устройства

с исполнительными механизмами комплекса.

Далее, разрабатывается математическая модель системы управления, которая определяет состав отдельных

подсистем, а также функциональные связи между ними.

51

52.

Проектирование СВУ для встраиваемых систем – алгоритмический синтезНа этапе алгоритмического синтеза выполняется :

• анализ условий и способов применения объекта управления;

• выбор и обоснование состава функциональных задач, подлежащих решению;

• разработка математического описания решаемых задач;

• анализ состава оборудования системы управления объектом;

• выбор временной последовательности решения задач;

• разработка общего алгоритма, описанного математическим языком;

• выбор структуры системы управления объектом и определение структуры подсистемы ввода-вывода

вычислительного устройства;

• оценка точности измерения исходных данных;

• разработка алгоритма функционирования вычислительного устройства.

52

53.

Проектирование СВУ для встраиваемых систем – логический синтезНа этапе логического синтеза разрабатывается функциональная схема вычислительного устройства,

наилучшим образом удовлетворяющая основным характеристикам, полученным при алгоритмическом синтезе.

Производится выбор элементов и операционных устройств (сумматоров, счетчиков, регистров,

элементов памяти, процессоров, аналого-цифровых и цифро-аналоговых преобразователей), а также

составляются временные диаграммы работы основных блоков вычислительного устройства.

Основой логического синтеза является выбор структуры вычислительного устройства, максимально

удовлетворяющей требованиям, предъявляемым к ней алгоритмами, подлежащими к реализации.

53

54.

Проектирование СВУ для встраиваемых систем – конструктивный синтезНа этапе конструктивного синтеза решаются задачи, связанные с физической реализацией логической

структуры вычислительного устройства с учетом существующих технологических возможностей, путем генерации

допустимых вариантов структуры и выбора среди них наиболее рационального по заданным критериям.

В результате решения задачи конструктивного синтеза должны быть определены и выбраны :

• количество процессорных элементов и способ их соединения;

• способы распределения задач между ними;

• типы, количество и способы подключения подсистем взаимодействия с объектами к системному

интерфейсу вычислительного блока;

• способы подключения различных устройств ввода-вывода к системному интерфейсу;

• типы различных устройств ввода-вывода и устройств связи в каждой подсистеме ввода-вывода;

• типы модулей памяти для каждого процессорного элемента вычислительного устройства,

а также количество устройств каждого выбранного типа в каждой подсистеме.

54

55.

Проектирование СВУ для встраиваемых систем – конструктивный синтезВ качестве критерия оценки возможных вариантов должен быть выбран показатель, зависящий от исходных

данных и критичный к вышеперечисленным характеристикам структуры вычислительного устройства.

Основной задачей и результатом выполнения конструктивного синтеза является разработка комплекта

конструкторской документации (конструкторская документация (КД) – графические и текстовые документы,

которые, в совокупности или в отдельности, определяют состав и устройство изделия, и содержат необходимые

данные для его разработки, изготовления, контроля, эксплуатации, ремонта и утилизации).

Некоторые полезные межгосударственные стандарты (ГОСТ) :

• ГОСТ 2.001 – ЕСКД. Общие положения.

• ГОСТ 2.102 – ЕСКД. Виды и комплектность конструкторских документов.

• ГОСТ 2.103 – ЕСКД. Стадии разработки.

• ГОСТ 2.109 – ЕСКД. Основные требования к чертежам.

• ГОСТ 2.201 – ЕСКД. Обозначение изделий и конструкторских документов.

• ГОСТ 2.105 – ЕСКД. Общие требования к текстовым документам.

• ГОСТ 2.601 – ЕСКД. Эксплуатационные документы.

55

56.

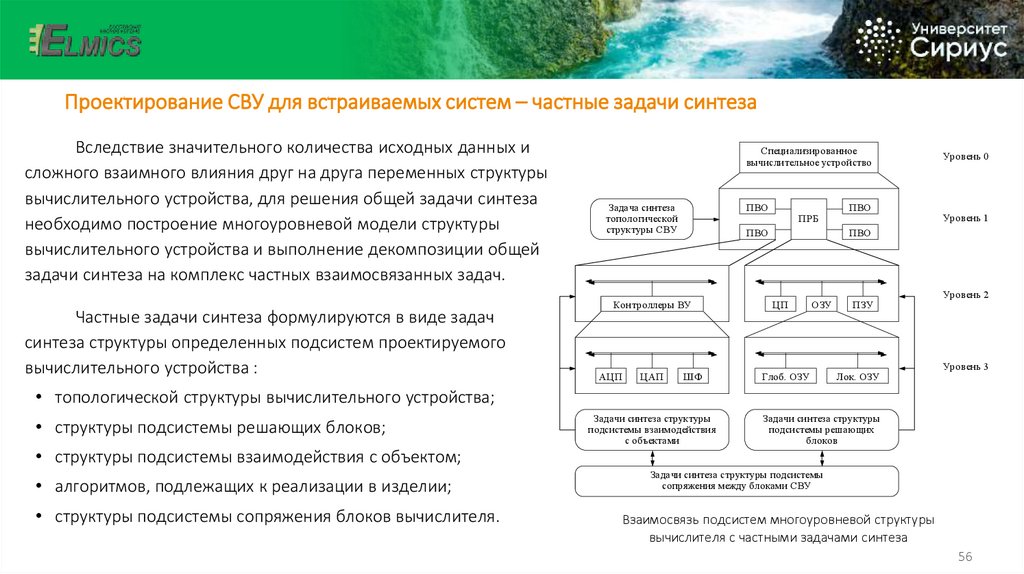

Проектирование СВУ для встраиваемых систем – частные задачи синтезаВследствие значительного количества исходных данных и

сложного взаимного влияния друг на друга переменных структуры

вычислительного устройства, для решения общей задачи синтеза

необходимо построение многоуровневой модели структуры

вычислительного устройства и выполнение декомпозиции общей

задачи синтеза на комплекс частных взаимосвязанных задач.

Частные задачи синтеза формулируются в виде задач

синтеза структуры определенных подсистем проектируемого

вычислительного устройства :

Специализированное

вычислительное устройство

Задача синтеза

топологической

структуры СВУ

ПВО

ПВО

Контроллеры ВУ

АЦ П

Ц АП

ПВО

ПРБ

ШФ

Уровень 0

Уровень 1

ПВО

ЦП

ОЗУ

Глоб. ОЗУ

ПЗУ

Лок. ОЗУ

Уровень 2

Уровень 3

• топологической структуры вычислительного устройства;

• структуры подсистемы решающих блоков;

• структуры подсистемы взаимодействия с объектом;

• алгоритмов, подлежащих к реализации в изделии;

• структуры подсистемы сопряжения блоков вычислителя.

Задачи синтеза структуры

подсистемы взаимодействия

с объектами

Задачи синтеза структуры

подсистемы решающих

блоков

Задачи синтеза структуры подсистемы

сопряжения между блоками СВУ

Взаимосвязь подсистем многоуровневой структуры

вычислителя с частными задачами синтеза

56

57.

Проектирование СВУ для встраиваемых систем – частные задачи синтезаКаждая из указанных задач решается по собственному алгоритму, однако все алгоритмы в процессе

решения задач между собой взаимодействуют - задают следующим задачам начальные условия, при которых

они должны решаться, и используют результаты решения предыдущих задач в качестве исходных данных для

своего решения.

Синтез топологической

структуры вычислительного

устройства

Синтез структуры

подсистемы взаимодействия

с объектами

Синтез алгоритмов,

подлежащих к реализации в

вычислительном устройстве

Синтез структуры

подсистемы решающих

блоков вычислителя

Синтез структуры

подсистемы сопряжения

блоков вычислителя

Взаимодействие алгоритмов решения частных задач синтеза подсистем специализированного вычислительного устройства.

57

58.

Особенности проектирования СВУ для встраиваемых системСпециализированное вычислительное устройство выполняет функцию одного из основных звеньев

встраиваемой системы управления, поэтому на состав такого устройства и на процедуру его проектирования

накладывается ряд специфических требований.

Методика проектирования подобных вычислительных устройств имеет несколько особенностей :

• проектирование вычислительного устройства обычно ведется одновременно с разработкой системы

управления в условиях неполной информации и возможных корректировок как самой системы, так и

требований к вычислителю;

• работа вычислительного устройства по фиксированному алгоритму расширяет диапазон поиска его

возможных структур за счет необходимости анализа аналоговых и аналого-цифровых устройств;

• условия применения вычислительных устройств на объектах и в системах с жесткими требованиями к

эксплуатационным характеристикам и высоким показателям надежности, особенно остро ставят задачи

разработки наиболее рациональной структуры, при наличии ограничений по времени готовности, массе,

габаритам, энергопотреблению и т.д.

58

59.

Этапы проектирования СВУ для встраиваемых системСтадии разработки конструкторской документации на изделия всех отраслей промышленности и этапы

выполнения работ регламентируются государственным стандартом ГОСТ 2.103-2013 «ЕСКД. Стадии разработки».

Существующая практика проектирования конкретно вычислительных устройств для различных систем

управления позволяет считать целесообразным выделение следующих этапов :

• предварительное проектирование (направленный поиск информации на основе просмотра нескольких

вариантов построения вычислительного устройства);

• системотехнический синтез и разработка эффективных алгоритмов функционирования вычислительного

устройства (уточняются требования к изделию по точности, а также способы ввода и вывода информации);

• структурное проектирование (выбираются формы представления преобразуемой информации,

определяются характеристики и набор блоков для получения требуемых характеристик вычислительного

устройства, определяется возможность проектирования блоков и устройств управления по отдельности);

• функционально-логическое проектирование (разрабатываются блоки и устройства управления).

59

60.

Этапы проектирования СВУ для встраиваемых систем• комплексное согласование (уточняются характеристики блоков, корректируется структурная схема изделия);

• оценка надежности всего изделия в целом;

• техническое проектирование (заканчивается выпуском конструкторской документации и разработкой

опытного образца вычислительного устройства);

• настройка и отладка в системе (производится настройка и отладка разработанного вычислительного

устройства в составе системы управления, уточняются его стыковочные параметры с другими блоками

комплекса, производится тестовая эксплуатация);

• доработка конструкторской документации на вычислительное устройство с учетом появившихся замечаний

в результате стыковки в составе комплекса (изменяется конструкторская документация, при необходимости

повторно выполняются расчеты надежности и т.д.).

Процесс проектирования специализированных вычислительных устройств является итерационным, т.е.

осуществляется методом последовательных приближений, что находит свое отражение в тесной взаимосвязи

всех этапов проектирования.

60

61.

Синтез алгоритмов функционирования вычислительных устройствЗадачи,

решаемые СВУ

Вспомогательные

задачи

Основные

(функциональные)

Сбора и первичной

обработки информации

Оптимизированной

обработки информации

Вторичной

обработки информации

Представления

информации

Расширения

операционных

ресурсов СВУ

Организации

вычислительного

процесса

Контроля

корректности

функционирования

61

62.

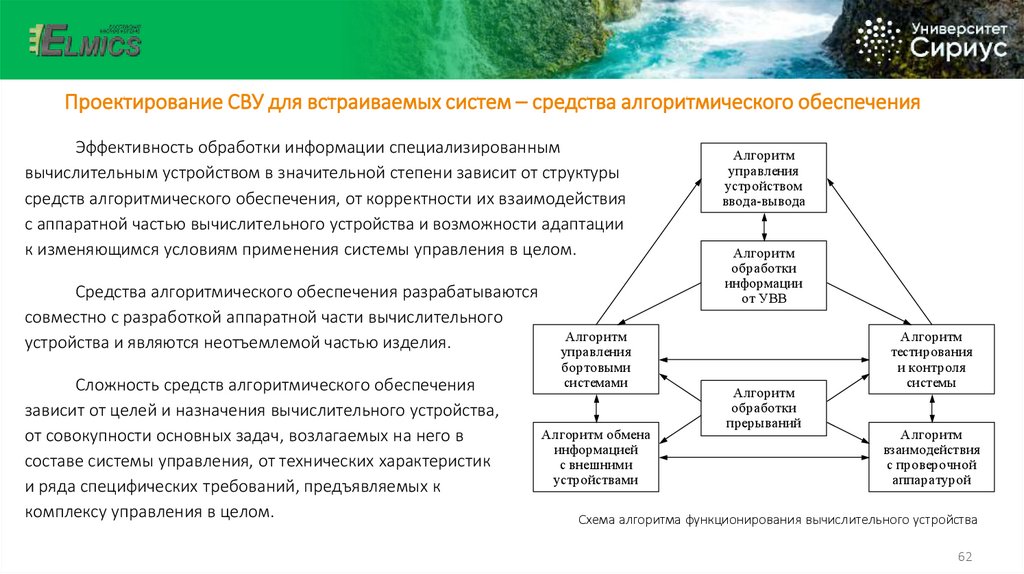

Проектирование СВУ для встраиваемых систем – средства алгоритмического обеспеченияЭффективность обработки информации специализированным

вычислительным устройством в значительной степени зависит от структуры

средств алгоритмического обеспечения, от корректности их взаимодействия

с аппаратной частью вычислительного устройства и возможности адаптации

к изменяющимся условиям применения системы управления в целом.

Средства алгоритмического обеспечения разрабатываются

совместно с разработкой аппаратной части вычислительного

устройства и являются неотъемлемой частью изделия.

Сложность средств алгоритмического обеспечения

зависит от целей и назначения вычислительного устройства,

от совокупности основных задач, возлагаемых на него в

составе системы управления, от технических характеристик

и ряда специфических требований, предъявляемых к

комплексу управления в целом.

Алгоритм

управления

бортовыми

системами

Алгоритм обмена

информацией

с внешними

устройствами

Алгоритм

управления

устройством

ввода-вывода

Алгоритм

обработки

информации

от УВВ

Алгоритм

обработки

прерываний

Алгоритм

тестирования

и контроля

системы

Алгоритм

взаимодействия

с проверочной

аппаратурой

Схема алгоритма функционирования вычислительного устройства

62

63.

Требования к алгоритмам функционирования СВУК алгоритмам функционирования современных специализированных вычислительных устройств для

встраиваемых систем управления предъявляются следующие требования :

• выполнение вычислений должно осуществляться в реальном масштабе времени при наличии задач, имеющих

случайный характер включения в общий вычислительный процесс;

• в алгоритме функционирования вычислительного устройства должны быть предусмотрены средства защиты

вычислительного процесса от случайных сбоев, отказов аппаратуры и ошибок во входной информации;

• алгоритм функционирования вычислительного устройства должен обеспечивать возможность работы в

тестовом режиме с целью обнаружения неисправностей в системе управления.

Таким образом, общий алгоритм функционирования специализированных вычислительных устройств

встраиваемых систем управления представляет собой сложный комплекс функционально различимых частных

алгоритмов с определенным порядком их выполнения.

63

64.

Классификация языков программированияЯзыки программирования

Процедурные

Низкого уровня

(машинно-зависимые)

в машинных кодах

Ассемблер

MASM

Непроцедурные

Высокого уровня

(машинно-независимые)

Универсальные

Fortran

Basic

Pascal

ANSI C

Проблемноориентированные

PHP

Perl

JavaScript

VBScript

Объектноориентированные

C ++

C#

V. Basic

Visual C

Delphi

Java

Swift

GoLang

Декларативные

Языки сценариев

(скрипты)

Perl

Python

LUA

QML

Функциональные

LISP

Miranda

Haskel

Логические

Пролог

64

65.

Языки программирования для СВУ встраиваемых системДля написания небольших системных программ, драйверов устройств, программирования специализированных процессоров

часто используются языки низкого уровня, в частности – ассемблер.

Преимущества программирования на ассемблере :

Преимущества языков высокого уровня :

• компактность (размер программного кода в памяти

программ);

• хорошая переносимость программных кодов;

• быстродействие (время выполнения программы);

• возможность прямого доступа к аппаратным ресурсам.

Основной недостаток ассемблера – несовместимость кодов, т.е.

плохая переносимость программ с одной аппаратной платформы

(микропроцессорной архитектуры) на другую.

• читабельность исходных кодов (программа может быть

понята и модифицируема не тем, кто ее разрабатывал);

• большая степень абстракции, многократное использование

отлаженного кода;

• большое количество разнообразных библиотек;

• сокращенное время разработки программного обеспечения.

Согласно исследованию IEEE Spectrum, проведенному в 2016 г., языки Си и Си++ заняли первые два места, как наиболее

применяющиеся во всем мире для программирования вычислительных устройств встраиваемых систем управления.

Однако, оптимальная стратегия – совместное использование языка Си и Ассемблера.

65

66.

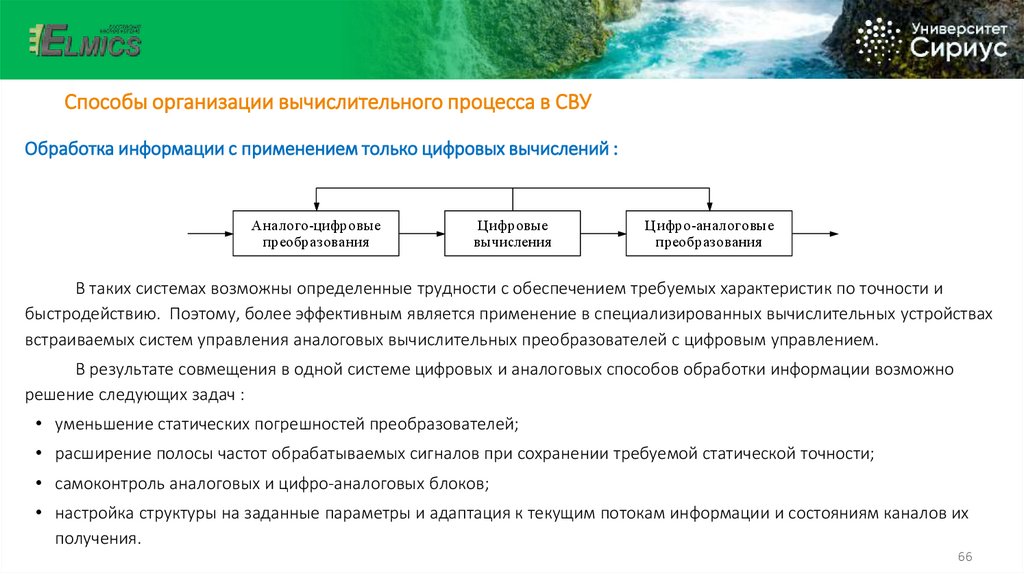

Способы организации вычислительного процесса в СВУОбработка информации с применением только цифровых вычислений :

Аналого-цифровые

преобразования

Цифровые

вычисления

Цифро-аналоговые

преобразования

В таких системах возможны определенные трудности с обеспечением требуемых характеристик по точности и

быстродействию. Поэтому, более эффективным является применение в специализированных вычислительных устройствах

встраиваемых систем управления аналоговых вычислительных преобразователей с цифровым управлением.

В результате совмещения в одной системе цифровых и аналоговых способов обработки информации возможно

решение следующих задач :

• уменьшение статических погрешностей преобразователей;

• расширение полосы частот обрабатываемых сигналов при сохранении требуемой статической точности;

• самоконтроль аналоговых и цифро-аналоговых блоков;

• настройка структуры на заданные параметры и адаптация к текущим потокам информации и состояниям каналов их

получения.

66

67.

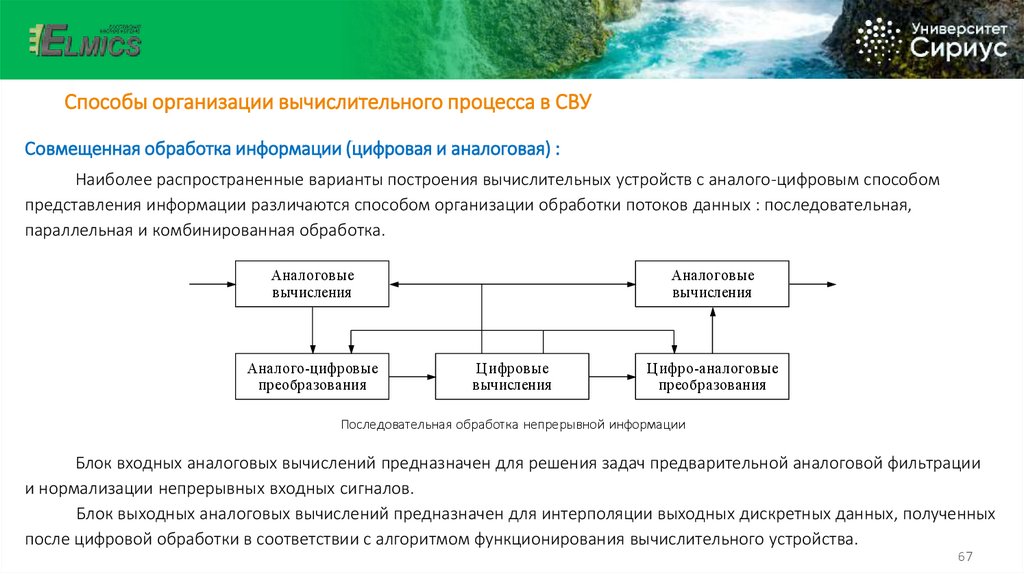

Способы организации вычислительного процесса в СВУСовмещенная обработка информации (цифровая и аналоговая) :

Наиболее распространенные варианты построения вычислительных устройств с аналого-цифровым способом

представления информации различаются способом организации обработки потоков данных : последовательная,

параллельная и комбинированная обработка.

Аналоговые

вычисления

Аналого-цифровые

преобразования

Аналоговые

вычисления

Цифровые

вычисления

Цифро-аналоговые

преобразования

Последовательная обработка непрерывной информации

Блок входных аналоговых вычислений предназначен для решения задач предварительной аналоговой фильтрации

и нормализации непрерывных входных сигналов.

Блок выходных аналоговых вычислений предназначен для интерполяции выходных дискретных данных, полученных

после цифровой обработки в соответствии с алгоритмом функционирования вычислительного устройства.

67

68.

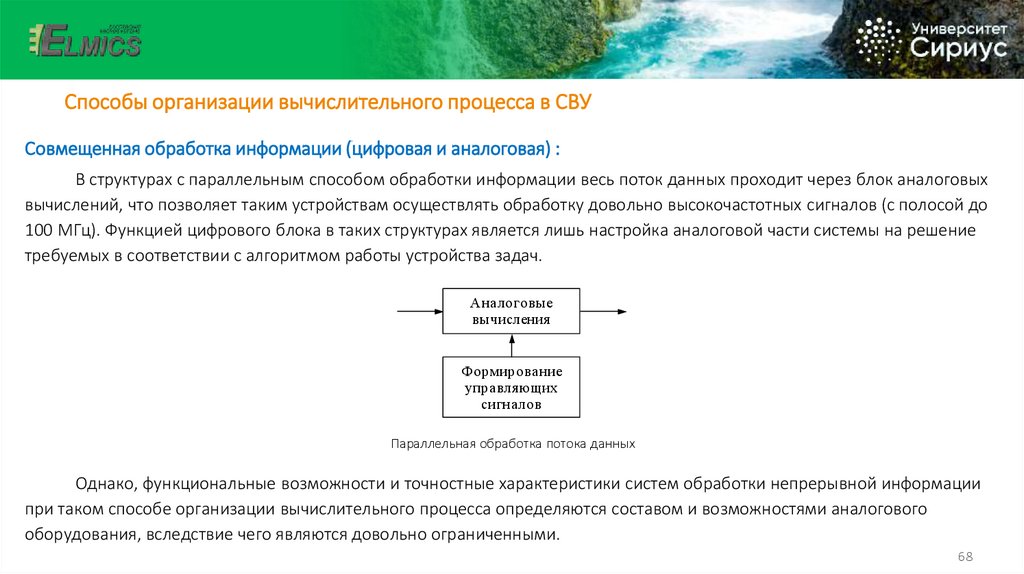

Способы организации вычислительного процесса в СВУСовмещенная обработка информации (цифровая и аналоговая) :

В структурах с параллельным способом обработки информации весь поток данных проходит через блок аналоговых

вычислений, что позволяет таким устройствам осуществлять обработку довольно высокочастотных сигналов (с полосой до

100 МГц). Функцией цифрового блока в таких структурах является лишь настройка аналоговой части системы на решение

требуемых в соответствии с алгоритмом работы устройства задач.

Аналоговые

вычисления

Формирование

управляющих

сигналов

Параллельная обработка потока данных

Однако, функциональные возможности и точностные характеристики систем обработки непрерывной информации

при таком способе организации вычислительного процесса определяются составом и возможностями аналогового

оборудования, вследствие чего являются довольно ограниченными.

68

69.

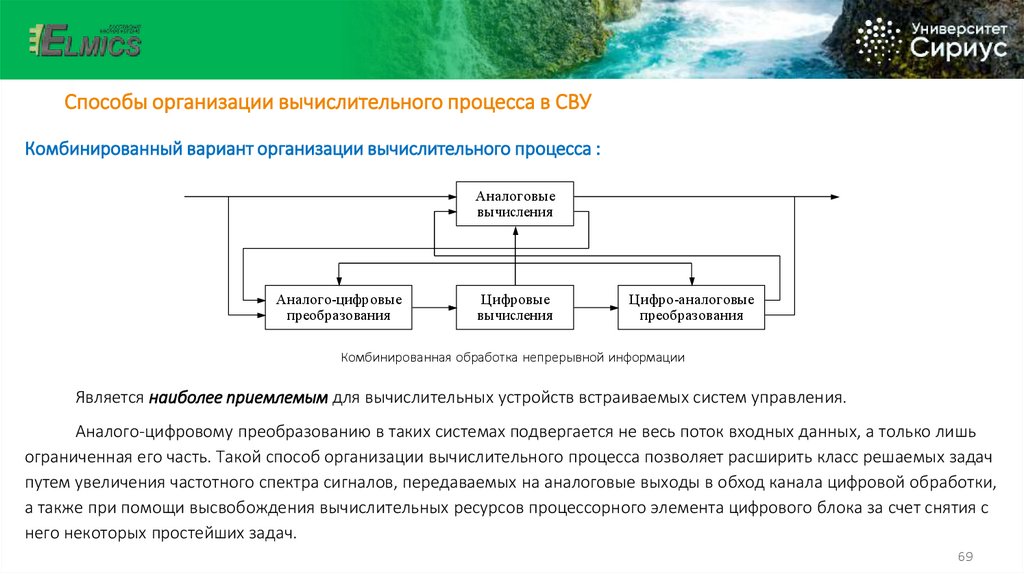

Способы организации вычислительного процесса в СВУКомбинированный вариант организации вычислительного процесса :

Аналоговые

вычисления

Аналого-цифровые

преобразования

Цифровые

вычисления

Цифро-аналоговые

преобразования

Комбинированная обработка непрерывной информации

Является наиболее приемлемым для вычислительных устройств встраиваемых систем управления.

Аналого-цифровому преобразованию в таких системах подвергается не весь поток входных данных, а только лишь

ограниченная его часть. Такой способ организации вычислительного процесса позволяет расширить класс решаемых задач

путем увеличения частотного спектра сигналов, передаваемых на аналоговые выходы в обход канала цифровой обработки,

а также при помощи высвобождения вычислительных ресурсов процессорного элемента цифрового блока за счет снятия с

него некоторых простейших задач.

69

70.

Синтез подсистемы ввода-вывода вычислительных устройствСпециализированное вычислительное устройство, входящее в контур встраиваемой системы управления, должно

обрабатывать информационные потоки, поступающие от разнообразных датчиков комплекса.

Эффективность системы управления зависит от точности выработки выходных сигналов, что, в свою очередь,

зависит от качества согласования датчиков комплекса с вычислительным устройством.

Обычно в СВУ для встраиваемых систем управления подсистема ввода-вывода выполняет следующие функции :

• прием и передача в решающий блок информации о релейных сигналах;

• прием и передача параллельных двоичных кодов;

• прием и передача информации в виде последовательных двоичных кодов;

• прием и передача аналоговых сигналов постоянного тока;

• прием и передача аналоговых сигналов переменного тока;

• формирование сигналов запроса на прерывание вычислений в решающем блоке;

• формирование под управлением решающего блока выходных сигналов для исполнительных механизмов комплекса;

• прием и формирование контрольно-проверочных сигналов для внешних устройств.

70

71.

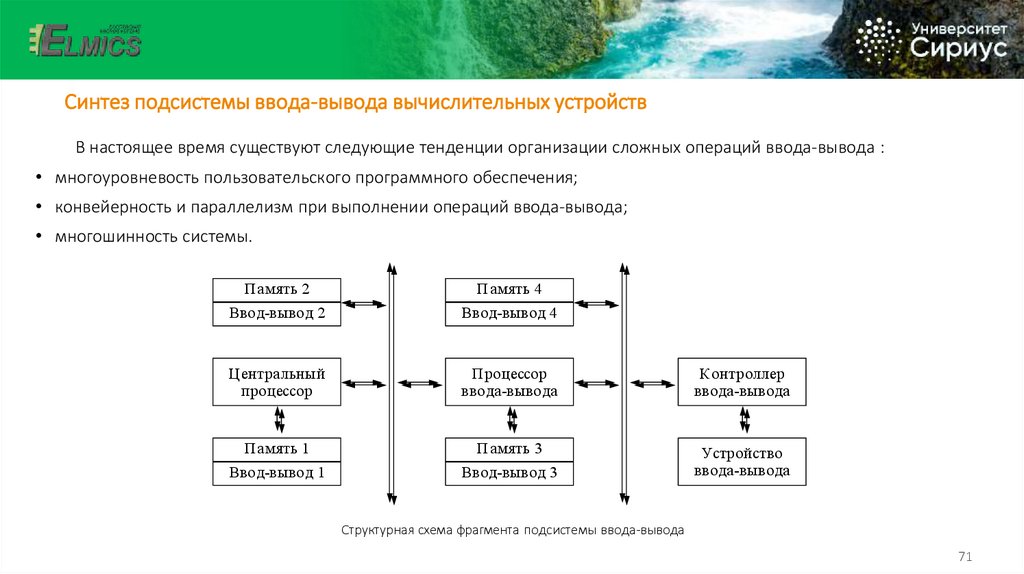

Синтез подсистемы ввода-вывода вычислительных устройствВ настоящее время существуют следующие тенденции организации сложных операций ввода-вывода :

• многоуровневость пользовательского программного обеспечения;

• конвейерность и параллелизм при выполнении операций ввода-вывода;

• многошинность системы.

Память 2

Память 4

Ввод-вывод 2

Ввод-вывод 4

Центральный

процессор

Процессор

ввода-вывода

Контроллер

ввода-вывода

Память 1

Память 3

Ввод-вывод 1

Ввод-вывод 3

Устройство

ввода-вывода

Структурная схема фрагмента подсистемы ввода-вывода

71

72.

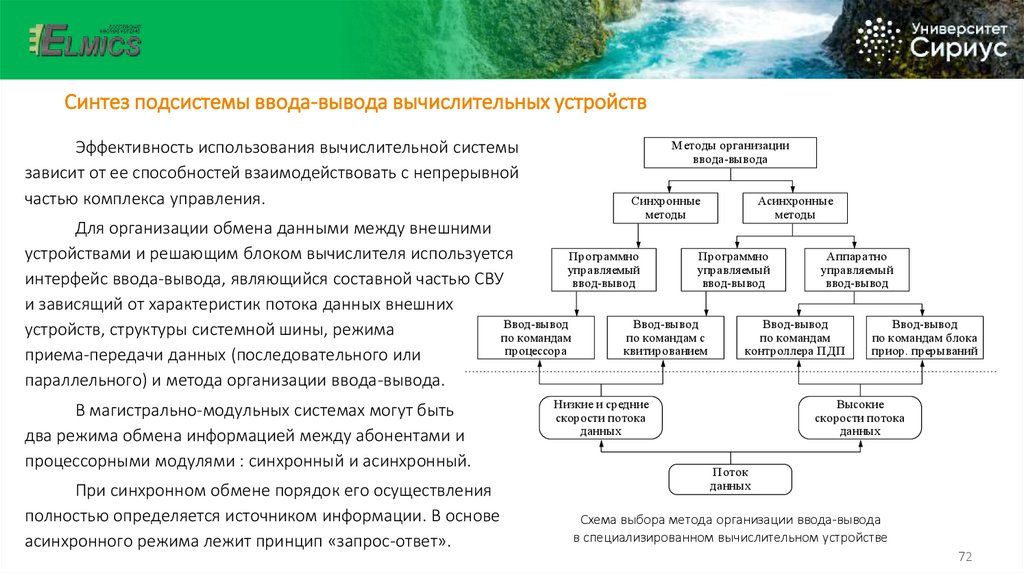

Синтез подсистемы ввода-вывода вычислительных устройствЭффективность использования вычислительной системы

зависит от ее способностей взаимодействовать с непрерывной

частью комплекса управления.

Методы организации

ввода-вывода

Синхронные

методы

Асинхронные

методы

Для организации обмена данными между внешними

устройствами и решающим блоком вычислителя используется

Программно

Программно

Аппаратно

управляемый

управляемый

управляемый

интерфейс ввода-вывода, являющийся составной частью СВУ

ввод-вывод

ввод-вывод

ввод-вывод

и зависящий от характеристик потока данных внешних

Ввод-вывод

Ввод-вывод

Ввод-вывод

Ввод-вывод

устройств, структуры системной шины, режима

по командам

по командам с

по командам

по командам блока

процессора

квитированием

контроллера ПДП

приор. прерываний

приема-передачи данных (последовательного или

параллельного) и метода организации ввода-вывода.

В магистрально-модульных системах могут быть

два режима обмена информацией между абонентами и

процессорными модулями : синхронный и асинхронный.

При синхронном обмене порядок его осуществления

полностью определяется источником информации. В основе

асинхронного режима лежит принцип «запрос-ответ».

Низкие и средние

скорости потока

данных

Высокие

скорости потока

данных

Поток

данных

Схема выбора метода организации ввода-вывода

в специализированном вычислительном устройстве

72

73.

Подсистема ввода-вывода – программный обмен информациейПрограммный обмен информацией является основным в любой микропроцессорной системе.

Он предусмотрен всегда, без него невозможны другие режимы обмена.

Все операции (циклы) обмена информацией инициируются

только процессорным элементов и выполняются строго в порядке,

предписанном исполняемой программой. Процессор считывает

из памяти коды команд ввода-вывода, исполняет их, читая данные

из памяти или из устройства ввода-вывода, обрабатывает их,

записывает данные в память или передает в устройство ввода-вывода.

Путь процессора по программе может быть линейным, может

содержать безусловные и условные переходы, может быть, также,

циклическим, но он всегда непрерывен и полностью находится под

контролем процессора.

Ни на какие внешние события, не связанные с выполнением

программы, процессор в данном режиме не реагирует.

73

74.

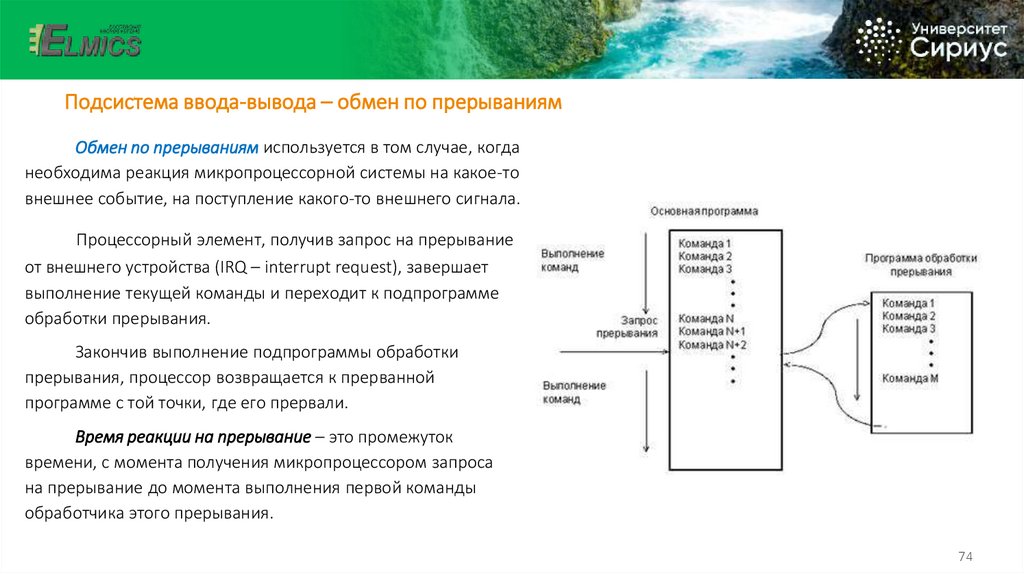

Подсистема ввода-вывода – обмен по прерываниямОбмен по прерываниям используется в том случае, когда

необходима реакция микропроцессорной системы на какое-то

внешнее событие, на поступление какого-то внешнего сигнала.

Процессорный элемент, получив запрос на прерывание

от внешнего устройства (IRQ – interrupt request), завершает

выполнение текущей команды и переходит к подпрограмме

обработки прерывания.

Закончив выполнение подпрограммы обработки

прерывания, процессор возвращается к прерванной

программе с той точки, где его прервали.

Время реакции на прерывание – это промежуток

времени, с момента получения микропроцессором запроса

на прерывание до момента выполнения первой команды

обработчика этого прерывания.

74

75.

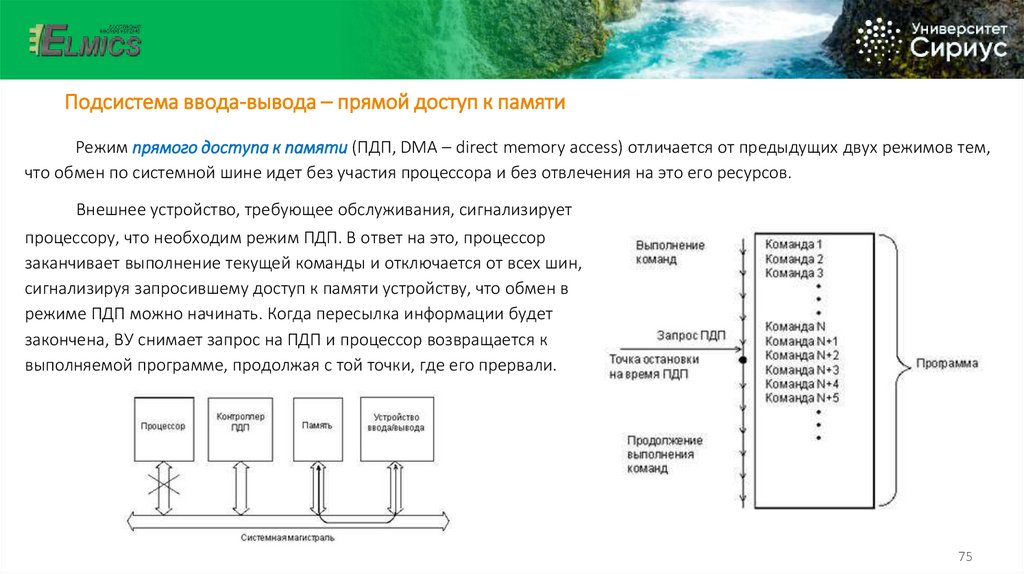

Подсистема ввода-вывода – прямой доступ к памятиРежим прямого доступа к памяти (ПДП, DMA – direct memory access) отличается от предыдущих двух режимов тем,

что обмен по системной шине идет без участия процессора и без отвлечения на это его ресурсов.

Внешнее устройство, требующее обслуживания, сигнализирует

процессору, что необходим режим ПДП. В ответ на это, процессор

заканчивает выполнение текущей команды и отключается от всех шин,

сигнализируя запросившему доступ к памяти устройству, что обмен в

режиме ПДП можно начинать. Когда пересылка информации будет

закончена, ВУ снимает запрос на ПДП и процессор возвращается к

выполняемой программе, продолжая с той точки, где его прервали.

75

76.

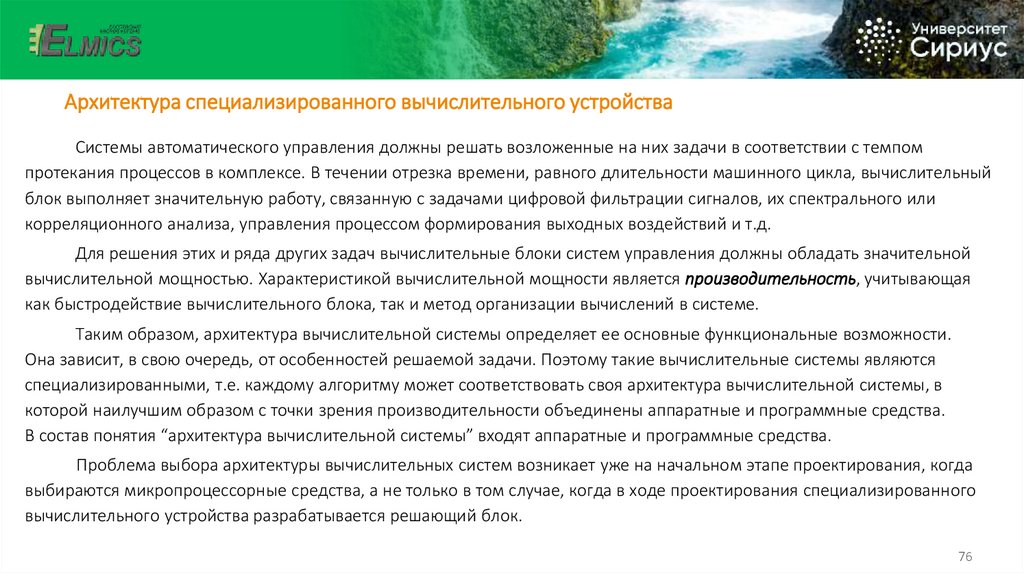

Архитектура специализированного вычислительного устройстваСистемы автоматического управления должны решать возложенные на них задачи в соответствии с темпом

протекания процессов в комплексе. В течении отрезка времени, равного длительности машинного цикла, вычислительный

блок выполняет значительную работу, связанную с задачами цифровой фильтрации сигналов, их спектрального или

корреляционного анализа, управления процессом формирования выходных воздействий и т.д.

Для решения этих и ряда других задач вычислительные блоки систем управления должны обладать значительной

вычислительной мощностью. Характеристикой вычислительной мощности является производительность, учитывающая

как быстродействие вычислительного блока, так и метод организации вычислений в системе.

Таким образом, архитектура вычислительной системы определяет ее основные функциональные возможности.

Она зависит, в свою очередь, от особенностей решаемой задачи. Поэтому такие вычислительные системы являются

специализированными, т.е. каждому алгоритму может соответствовать своя архитектура вычислительной системы, в

которой наилучшим образом с точки зрения производительности объединены аппаратные и программные средства.

В состав понятия “архитектура вычислительной системы” входят аппаратные и программные средства.

Проблема выбора архитектуры вычислительных систем возникает уже на начальном этапе проектирования, когда

выбираются микропроцессорные средства, а не только в том случае, когда в ходе проектирования специализированного

вычислительного устройства разрабатывается решающий блок.

76

77.

Архитектура специализированного вычислительного устройстваАрхитектура

вычислительных средств

Аппаратные

средства

Программное

обеспечение

Прикладные

Системные

Структуры с

“жесткой” логикой

Технические средства

организации

внутрисистемного

взаимодействия

Универсальные

алгоритмы и

программы

Технические средства

организации

межсистемного

взаимодействия

Прикладные

алгоритмы и

программы

Программируемые

структуры

Комбинированные

структуры

Прикладное

Системное

Программы

организации

внутрисистемного

обмена

Программы

управления

вводом-выводом

Архитектура вычислительных систем

77

78.

Архитектура специализированного вычислительного устройстваПри выборе архитектуры вычислительного устройства решается ряд задач, в совокупности обеспечивающих

выполнение системой управления возложенных на нее функций.

Первая задача связана с многовариантностью структур управляющих вычислительных устройств. Основной

возникающий при этом вопрос - как распределить вычислительную мощность системы по ее элементам и блокам.

На этом этапе определяется способ организации обмена информацией между составляющими вычислительное

устройство блоками, будет ли он синхронным или асинхронным, будет ли использоваться режим прямого доступа к

памяти и т.д. Внутренняя структура прежде всего связана с методами организации системной шины и устройств памяти.

Вторая задача связана с многообразием систем команд, которые в значительной мере определяют вычислительную

мощность системы и степень универсальности ее применения.

78

79.

Архитектура встраиваемого программного обеспеченияВ настоящее время распространены несколько вариантов архитектуры встраиваемого программного обеспечения :

• простой цикл управления (simple control loop, continuous loop)

Программное обеспечение «крутится» в бесконечном цикле, внутри которого осуществляется мониторинг внешних

устройств и сигналов. Общий цикл вызывает подпрограммы, каждая из которых управляет частью аппаратного или

программного обеспечения. Он называется простой цикл управления или программно-управляемый ввод-вывод.

«Вечный» цикл (Continuous Loop)

Инициализация

системы

Получение

входных данных

Вычисление

выходных значений

Формирование

выходных сигналов

79

80.

Архитектура встраиваемого программного обеспеченияВ настоящее время распространены несколько вариантов архитектуры встраиваемого программного обеспечения :

• система, управляемая прерываниями (interrupt-controlled system)

Задачи, выполняемые системой, запускаются различными событиями (прерываниями).

Такая архитектура используется, если обработчики событий должны запускаться не слишком часто,

а сами такие обработчики событий являются простыми и короткими по времени выполнения.

Такие системы также выполняют простые задачи и в основном цикле, но эти задачи не являются

слишком чувствительными к возникновению непредвиденных задержек.

Иногда, обработчик прерывания добавляет более длинные задачи в очередь на выполнение с тем,

чтобы по завершению обработки прерывания эти задачи были бы выполнены в основном цикле.

Этот метод приближает подобные системы к системам типа «многозадачное ядро с дискретными процессами».

80

81.

Архитектура встраиваемого программного обеспеченияВ настоящее время распространены несколько вариантов архитектуры встраиваемого программного обеспечения :

• система, управляемая прерываниями (interrupt-controlled system)

«Вечный» цикл (Continuous Loop)

Инициализация

системы

Получение

входных данных

Вычисление

выходных значений

Формирование

выходных сигналов

Interrupt #2

Interrupt #1

Подпрограмма обработки прерывания

Interrupt Service Routine (ISR)

81

82.

Синтез структуры подсистемы решающих блоков – шинная организацияДля достижения максимальной универсальности и упрощения протоколов обмена информацией в современных

вычислительных системах применяется шинная структура связей между отдельными устройствами.

Классическая структура («от каждого к каждому»)

Шинная структура связей

Достоинства шинной структуры связей :

• легко осуществляется пересылка всех информационных потоков в нужном направлении (например, их можно

пропустить через один микропроцессор);

• все устройства, подключенные к шине, должны принимать и передавать информацию по одним и тем же

правилам (протоколам обмена информацией по шине), соответственно, все узлы, отвечающие за обмен с

шиной в этих устройствах, должны быть единообразны, унифицированы.

82

83.

Синтез структуры подсистемы решающих блоков – шинная организацияДля достижения максимальной универсальности и упрощения протоколов обмена информацией в современных

вычислительных системах применяется шинная структура связей между отдельными устройствами.

Классическая структура («от каждого к каждому»)

Шинная структура связей

Недостатки шинной структуры связей :

• вся информация передается по линиям связи последовательно во времени, по очереди, что снижает быстродействие

системы по сравнению с классической структурой связей, когда вся информация между устройствами передается по

отдельным линиям связи («от каждого к каждому»);

• все устройства подключаются к каждой линии параллельно, поэтому любая неисправность любого устройства может

вывести из строя всю систему, если она портит линии связи.

83

84.

Синтез структуры подсистемы решающих блоков – базовые архитектурыТиповая обобщенная структура микропроцессорной вычислительной системы :

84

85.

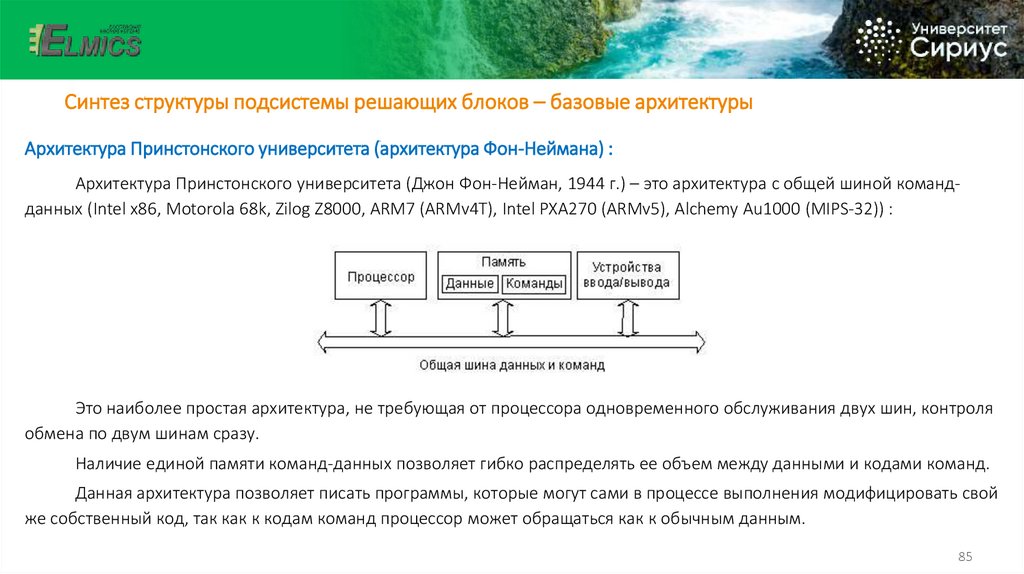

Синтез структуры подсистемы решающих блоков – базовые архитектурыАрхитектура Принстонского университета (архитектура Фон-Неймана) :

Архитектура Принстонского университета (Джон Фон-Нейман, 1944 г.) – это архитектура с общей шиной командданных (Intel x86, Motorola 68k, Zilog Z8000, ARM7 (ARMv4T), Intel PXA270 (ARMv5), Alchemy Au1000 (MIPS-32)) :

Это наиболее простая архитектура, не требующая от процессора одновременного обслуживания двух шин, контроля

обмена по двум шинам сразу.

Наличие единой памяти команд-данных позволяет гибко распределять ее объем между данными и кодами команд.

Данная архитектура позволяет писать программы, которые могут сами в процессе выполнения модифицировать свой

же собственный код, так как к кодам команд процессор может обращаться как к обычным данным.

85

86.

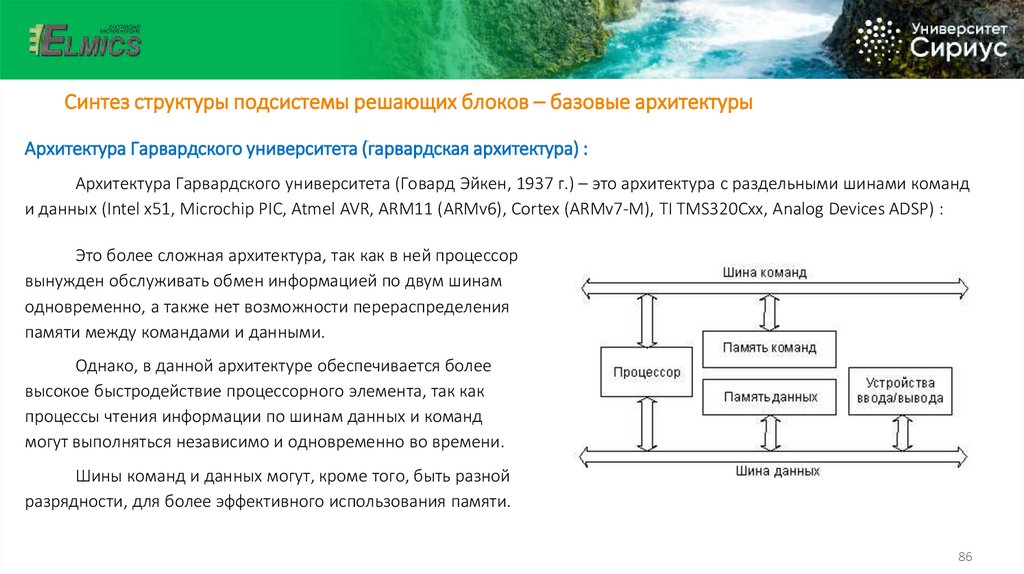

Синтез структуры подсистемы решающих блоков – базовые архитектурыАрхитектура Гарвардского университета (гарвардская архитектура) :

Архитектура Гарвардского университета (Говард Эйкен, 1937 г.) – это архитектура с раздельными шинами команд

и данных (Intel x51, Microchip PIC, Atmel AVR, ARM11 (ARMv6), Cortex (ARMv7-M), TI TMS320Cxx, Analog Devices ADSP) :

Это более сложная архитектура, так как в ней процессор

вынужден обслуживать обмен информацией по двум шинам

одновременно, а также нет возможности перераспределения

памяти между командами и данными.

Однако, в данной архитектуре обеспечивается более

высокое быстродействие процессорного элемента, так как

процессы чтения информации по шинам данных и команд

могут выполняться независимо и одновременно во времени.

Шины команд и данных могут, кроме того, быть разной

разрядности, для более эффективного использования памяти.

86

87.

Современные процессорные элементы - классификацияКлассификация современных процессорных элементов

По числу БИС

Однокристальные

По виду обрабатываемых сигналов

Многокристальные

По количеству выполняемых программ

Однопрограммные

16

Многопрограммные

32

Аналоговые

Универсальные

По характеру временной организации

По разрядности операндов (данных)

8

Цифровые

По назначению

Синхронные

Асинхронные

По количеству магистралей

Одномагистральные

По формату представления чисел

64

Фиксированная точка

Плавающая точка

Специализированные

Многомагистральные

По размеру набора инструкций

CISC

RISC

MISC

VLIW

87

88.

Современные процессорные элементы - микропроцессорыМикропроцессор (MPU, microprocessor unit) – электронное устройство, отвечающее за выполнение арифметических,

логических операций и операций управления, выполненное в виде одной микросхемы или комплекта из нескольких

специализированных микросхем.

Примеры микропроцессоров :

Intel 4004 – 1971,

Texas Instruments TMS1000 – 1972,

Motorola MC6800 - 1973,

Intel 8080 - 1974,

Zilog Z80 - 1976.

Структурная схема микропроцессора Intel 8080

88

89.

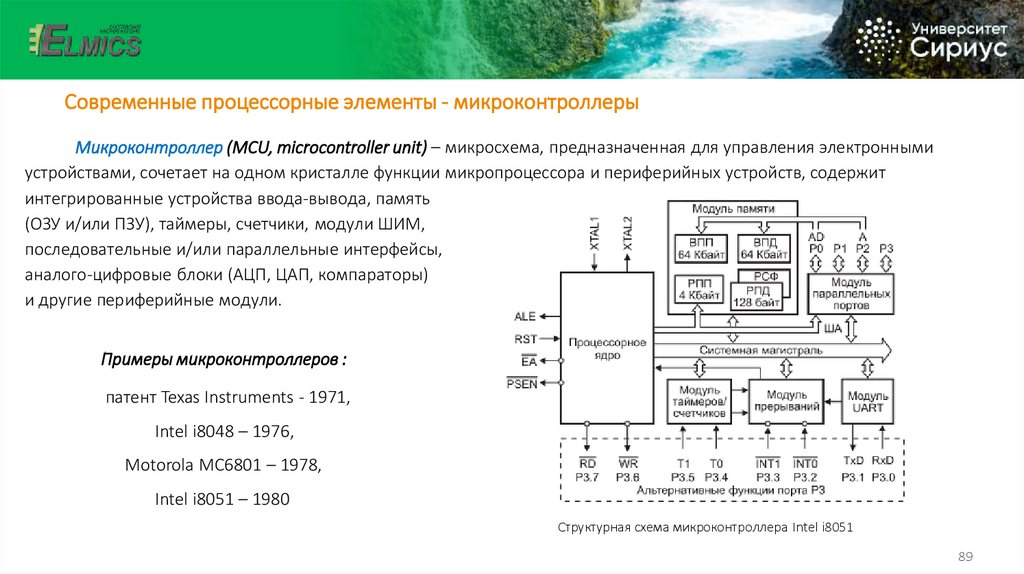

Современные процессорные элементы - микроконтроллерыМикроконтроллер (MCU, microcontroller unit) – микросхема, предназначенная для управления электронными

устройствами, сочетает на одном кристалле функции микропроцессора и периферийных устройств, содержит

интегрированные устройства ввода-вывода, память

(ОЗУ и/или ПЗУ), таймеры, счетчики, модули ШИМ,

последовательные и/или параллельные интерфейсы,

аналого-цифровые блоки (АЦП, ЦАП, компараторы)

и другие периферийные модули.

Примеры микроконтроллеров :

патент Texas Instruments - 1971,

Intel i8048 – 1976,

Motorola MC6801 – 1978,

Intel i8051 – 1980

Структурная схема микроконтроллера Intel i8051

89

90.

Микроконтроллеры – наиболее распространенные семейства32 разряда

8 разрядов

16 разрядов

Intel

x51

Intel

x96

ARM

ARM-7, -9, -11

ST Microelectronics

STM32 family

Motorola

68HC05

Motorola

68HC11

Microchip xAptiv

PIC32 (MIPS32)

Texas Instruments

Stellaris family

Microchip

AVR

Texas Instruments

MSP430

Microchip

AVR32

NXP

LPC family

Microchip

PICmicro

Microchip

PIC24

Espressif Tensilica

ESP32

NXP (Freescale)

Kinetis family

ST Microelectronics

STM8

Renesas

RL78

ARM Cortex-Mx

-M0, -M3, -M4, -M7

Silicon Labs

EFM32 family

90

91.

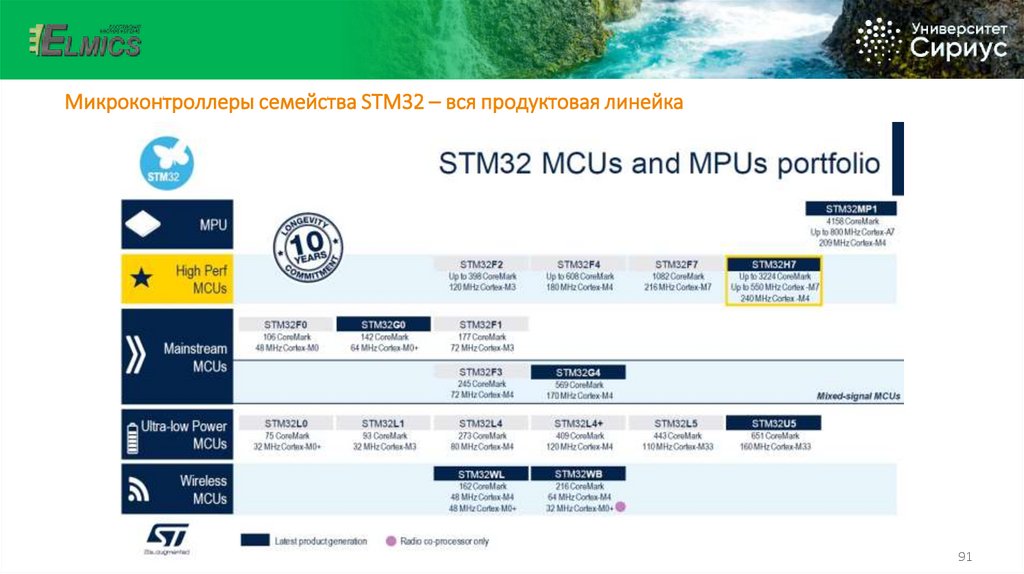

Микроконтроллеры семейства STM32 – вся продуктовая линейка91

92.

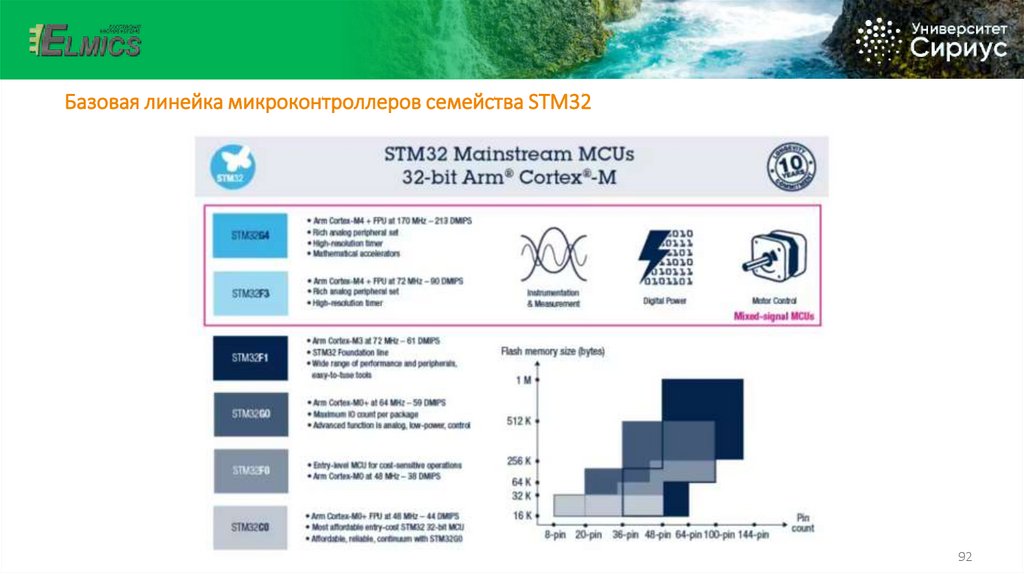

Базовая линейка микроконтроллеров семейства STM3292

93.

Малопотребляющие микроконтроллеры семейства STM3293

94.

Микроконтроллеры семейства STM32 с беспроводными интерфейсами94

95.

Высокопроизводительные микроконтроллеры семейства STM3295

96.

Высокопроизводительные микроконтроллеры семейства STM3296

97.

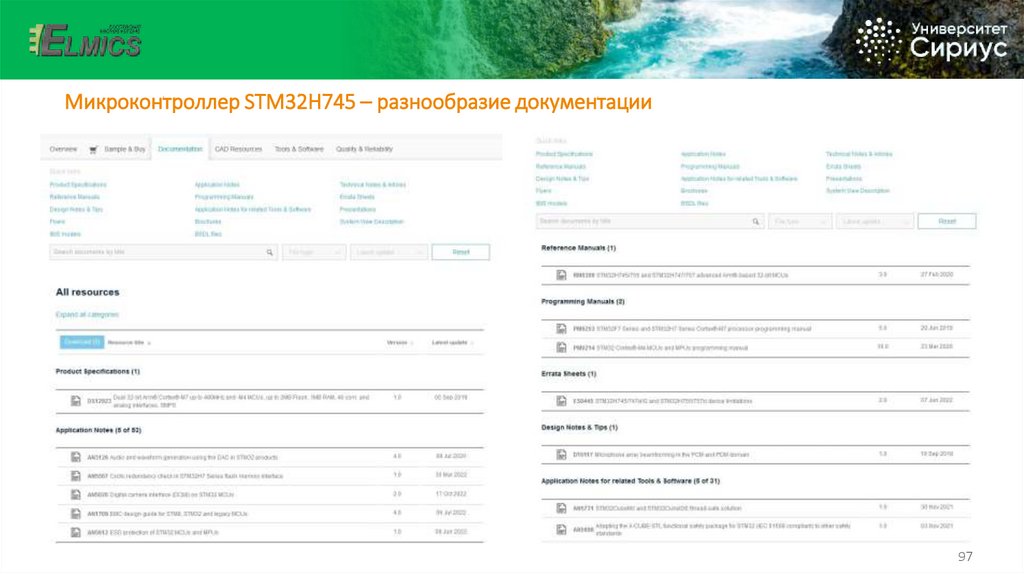

Микроконтроллер STM32H745 – разнообразие документации97

98.

Микроконтроллер STM32H745 – обзор семействаМаркетинговые материалы компании ST Microelectronics :

1. STM32H7 – MCUs for rich and complex applications (marketing presentation).

Файл : «_1 - microcontrollers_stm32h7_series_product_overview.pdf»

2. STM32H7 series – Powered by ARM Cortex-M7 & -M4 releasing your creativity.

Файл : «_2 - brstm32h7.pdf»

3. STM32 development boards portfolio.

Файл : «_3 - stm32_eval-tools_portfolio.pdf»

98

99.

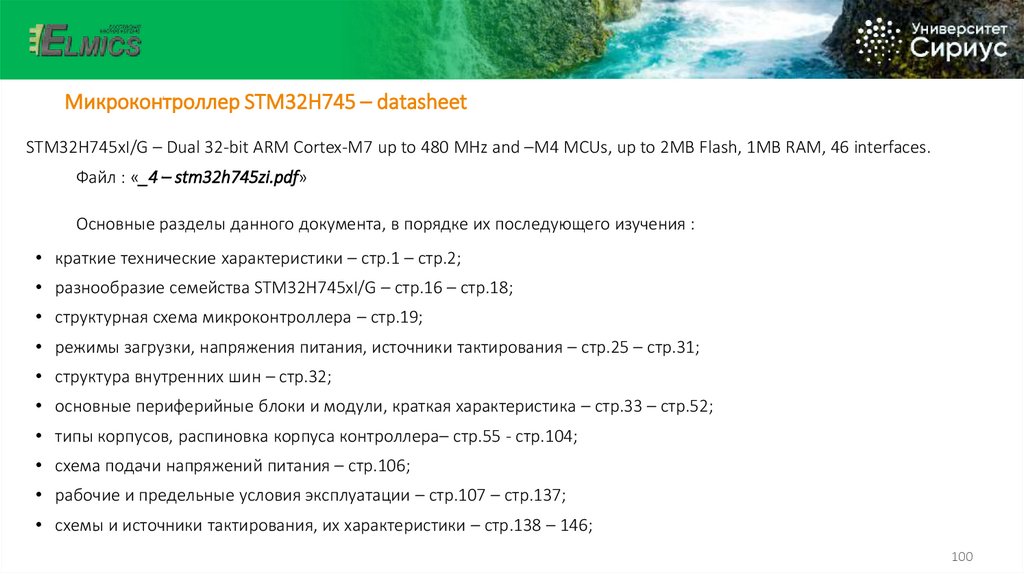

Микроконтроллер STM32H745 – datasheetТехническая спецификация (datasheet) – это документ, который объединяет в себе технические характеристики

продукта, материала, компонента или подсистемы и предназначен для использования инженером-разработчиком.

Создается компанией-производителем компонента и содержит следующую информацию :

• название производителя, код и название продукта;

• список доступных типов корпусов (с чертежами);

• особые свойства компонента;

• краткое описание функций компонента (functional overview);

• схема подключения (pin descriptions, «распиновка»);

• минимальные и максимальные эксплуатационные параметры (electrical characteristics);

• рекомендуемые условия эксплуатации (operating conditions);

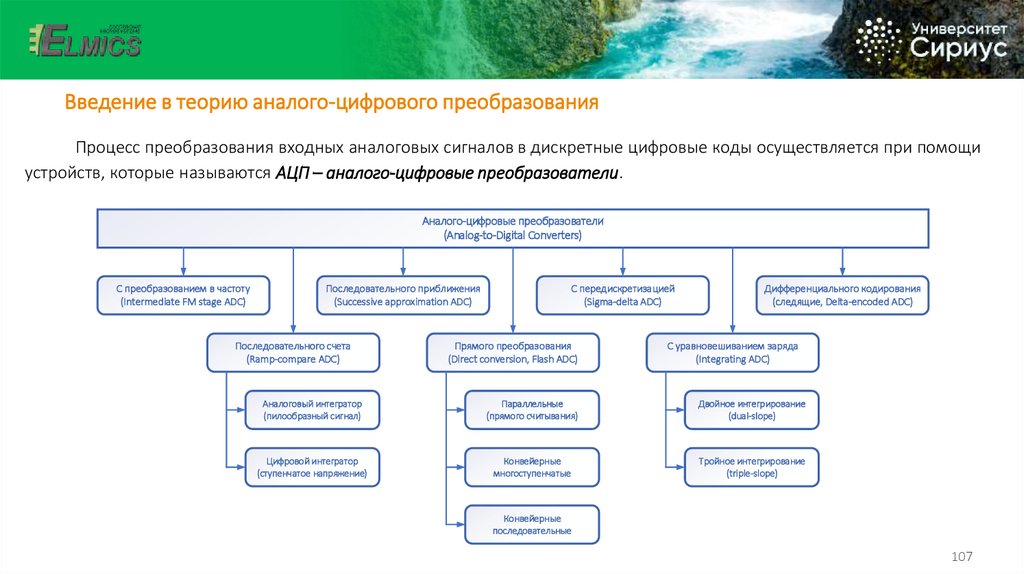

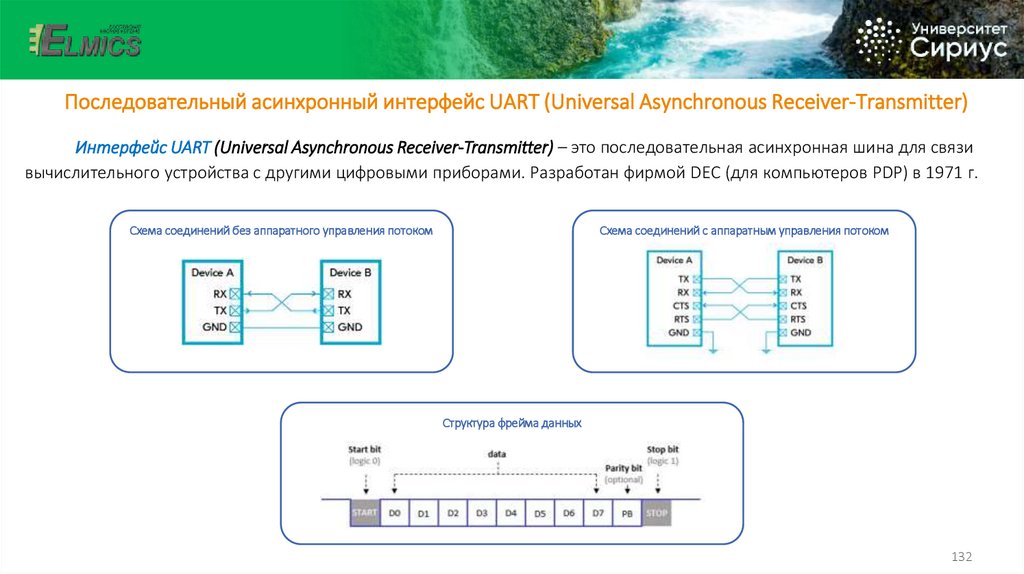

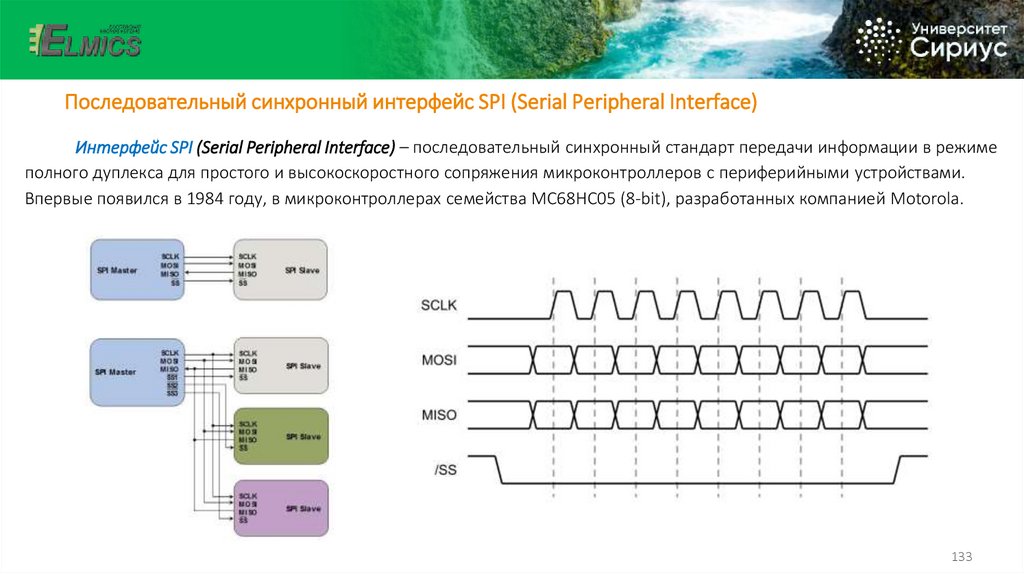

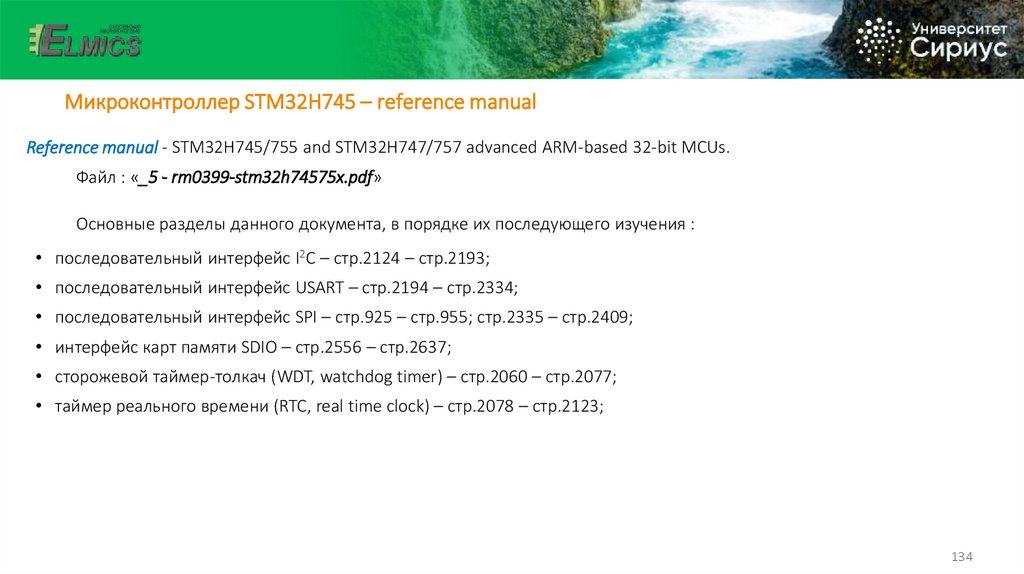

• рекомендации по применению (application examples).