Similar presentations:

Режимы работы процессоров разных поколений и способы адресации памяти

1.

Режимы работы процессоровразных поколений и способы

адресации памяти

1

2.

Принцип адресации ОЗУ для РС-совместимых ЭВМОЗУ

Сегмент 1

Сегмент 2

Сегмент 3

Начало сегмента

(базовый адрес) - БА

Память,

выделенная

для одной

задачи

Сегмент 4

Смещение ячейки

внутри сегмента - См

Адресуемая ячейка памяти

Физический

= БА + См

адрес памяти

2

3.

Режимы работы процессоровРазрядность

Режим

Размер

сегмента

Максимальный

объём памяти для

одной задачи

Виртуальная

память

Защита

памяти

Операционная

система

Приложения

Реальный

16

16

64 Кбайт

1 Мбайт

-

-

Защищённый

32

32

≤ 4Г байт

Вся память

(зависит от типа

процессора)

+

+

Виртуальный

реальный

32

16

≤ 64 Кбайт

+

+

1 Мбайт

для каждой задачи

3

4.

Режимы работы процессоровРазрядность

Режим

Реальный

Подрежим

-

Операционная

система

Приложения

16

16

Размер

сегмента

Максимальный

объём памяти для

одной задачи

Виртуальная

память

Защита

памяти

64 Кбайт

1 Мбайт

-

-

Вся память

(зависит от типа

процессора)

+

+

+

+

Защищённый

32

32

≤ 4Г байт

Виртуальный

реальный

32

16

≤ 64 Кбайт

64-разрядный

(long mode)

64

64

244 байт

244 байт

+

+

Совместимости

(legacy mode)

64

16/32

≤ 4Г байт

244 байт

+

+

IA-32

IA-32e,

AMD64,

x86-64,

EM64T

1 Мбайт

для каждой задачи

4

5.

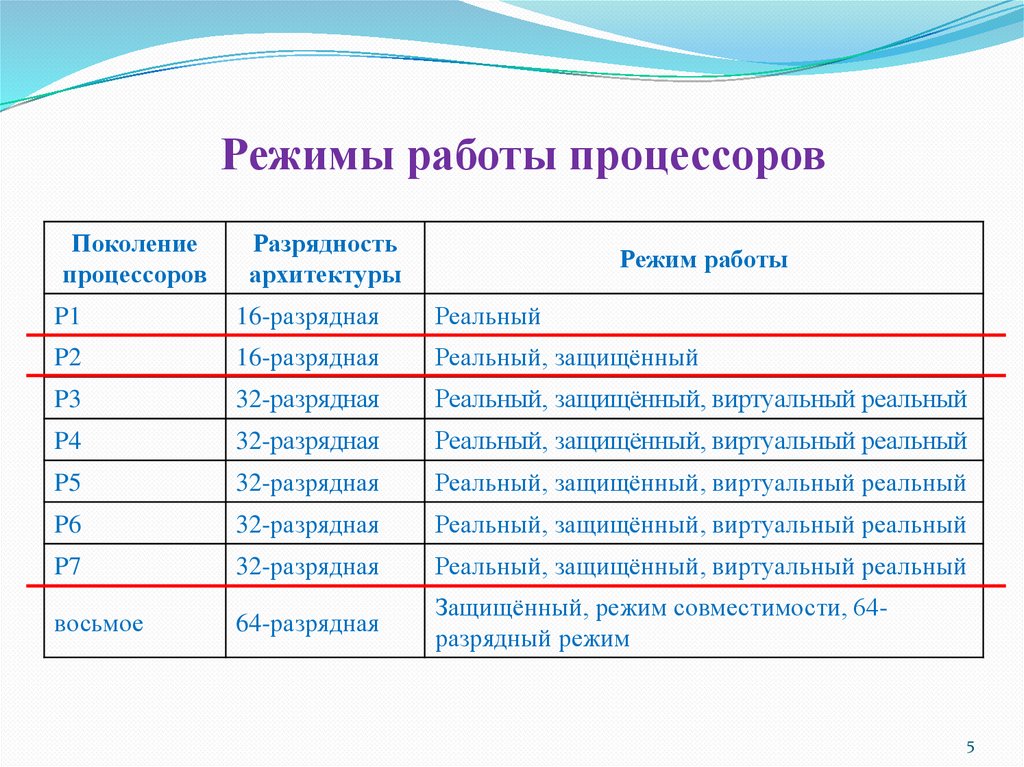

Режимы работы процессоровПоколение

процессоров

Разрядность

архитектуры

P1

16-разрядная

Реальный

P2

16-разрядная

Реальный, защищённый

P3

32-разрядная

Реальный, защищённый, виртуальный реальный

P4

32-разрядная

Реальный, защищённый, виртуальный реальный

P5

32-разрядная

Реальный, защищённый, виртуальный реальный

P6

32-разрядная

Реальный, защищённый, виртуальный реальный

P7

32-разрядная

Реальный, защищённый, виртуальный реальный

восьмое

64-разрядная

Защищённый, режим совместимости, 64разрядный режим

Режим работы

5

6.

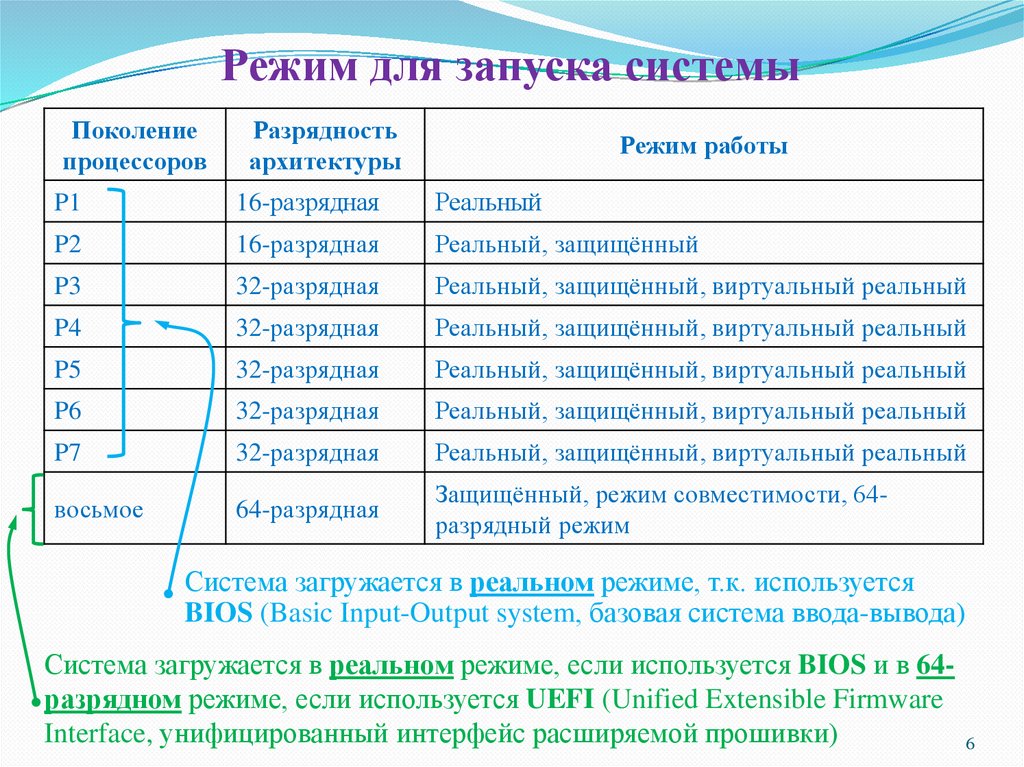

Режим для запуска системыПоколение

процессоров

Разрядность

архитектуры

P1

16-разрядная

Реальный

P2

16-разрядная

Реальный, защищённый

P3

32-разрядная

Реальный, защищённый, виртуальный реальный

P4

32-разрядная

Реальный, защищённый, виртуальный реальный

P5

32-разрядная

Реальный, защищённый, виртуальный реальный

P6

32-разрядная

Реальный, защищённый, виртуальный реальный

P7

32-разрядная

Реальный, защищённый, виртуальный реальный

восьмое

64-разрядная

Защищённый, режим совместимости, 64разрядный режим

Режим работы

Система загружается в реальном режиме, т.к. используется

BIOS (Basic Input-Output system, базовая система ввода-вывода)

Система загружается в реальном режиме, если используется BIOS и в 64разрядном режиме, если используется UEFI (Unified Extensible Firmware

Interface, унифицированный интерфейс расширяемой прошивки)

6

7.

Режимы работы процессоровРазрядность

Режим

Реальный

Подрежим

-

Операционная

система

Приложения

16

16

Размер

сегмента

Максимальный

объём памяти для

одной задачи

Виртуальная

память

Защита

памяти

64 Кбайт

1 Мбайт

-

-

Вся память

(зависит от типа

процессора)

+

+

+

+

Защищённый

32

32

≤ 4Г байт

Виртуальный

реальный

32

16

≤ 64 Кбайт

64-разрядный

64

64

244 байт

244 байт

+

+

Совместимости

64

16/32

≤ 4Г байт

244 байт

+

+

IA-32

IA-32e,

AMD64,

x86-64,

EM64T

1 Мбайт

для каждой задачи

7

8.

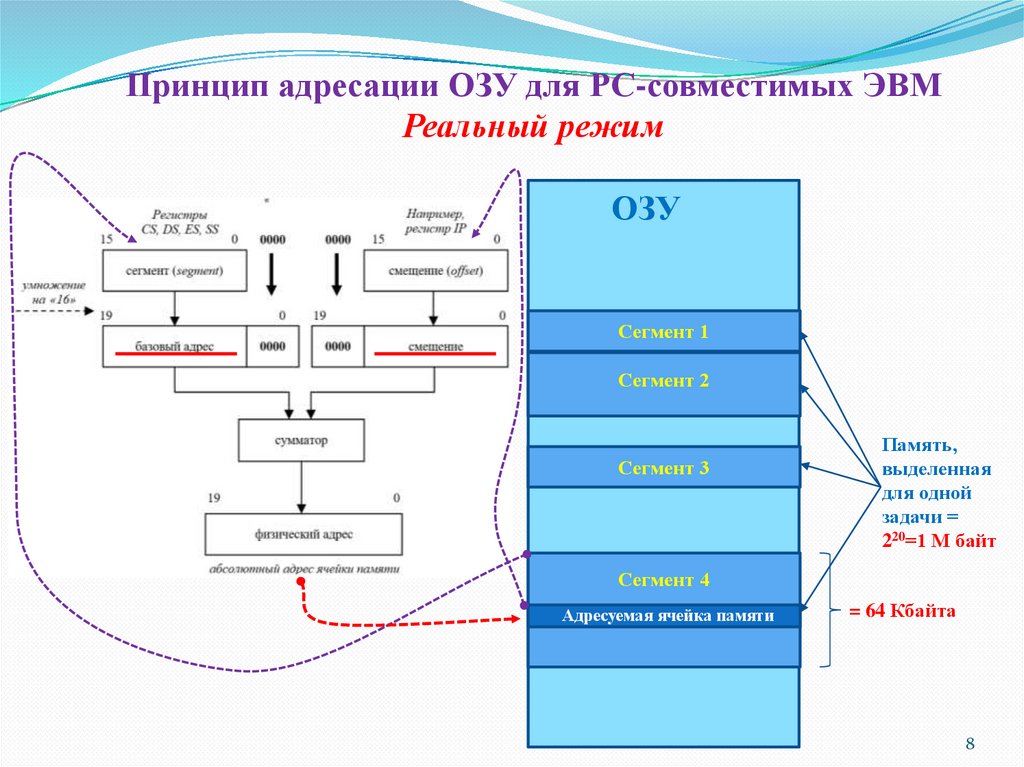

Принцип адресации ОЗУ для РС-совместимых ЭВМРеальный режим

ОЗУ

Сегмент 1

Сегмент 2

Сегмент 3

Память,

выделенная

для одной

задачи =

220=1 М байт

Сегмент 4

Адресуемая ячейка памяти

= 64 Кбайта

8

9.

Режимы работы процессоровРазрядность

Режим

Реальный

Подрежим

-

Защищённый

Операционная

система

Приложения

16

16

Размер

сегмента

Максимальный

объём памяти для

одной задачи

Виртуальная

память

Защита

памяти

64 Кбайт

1 Мбайт

-

-

+

+

+

+

Вся память

32

32

≤ 4Г байт (зависит от типа

процессора)

IA-32

IA-32e,

AMD64,

x86-64,

EM64T

Виртуальный

реальный

32

16

≤ 64 Кбайт

64-разрядный

64

64

244 байт

244 байт

+

+

Совместимости

64

16/32

≤ 4Г байт

244 байт

+

+

1 Мбайт

для каждой задачи

9

10.

Принцип адресации ОЗУ для РС-совместимых ЭВМЗащищённый режим для процессора i80286

ОЗУ

Сегмент 1

Сегмент 2

Локальная дескрипторная

таблица содержит описание

сегментов, занятых «рядовыми»

программами и данными.

Локальная таблица может быть

определена для каждой

конкретной задачи (процесса).

Глобальная дескрипторная таблица

содержит описание сегментов,

занятых операционной системой и

Сегмент 3

структурами данных, совместно

используемыми ядрами процессора. У

каждого ядра процессора своя

глобальная дескрипторная таблица.

Память,

выделенная

для одной

задачи =

224=16 М байт

Сегмент 4

10

11.

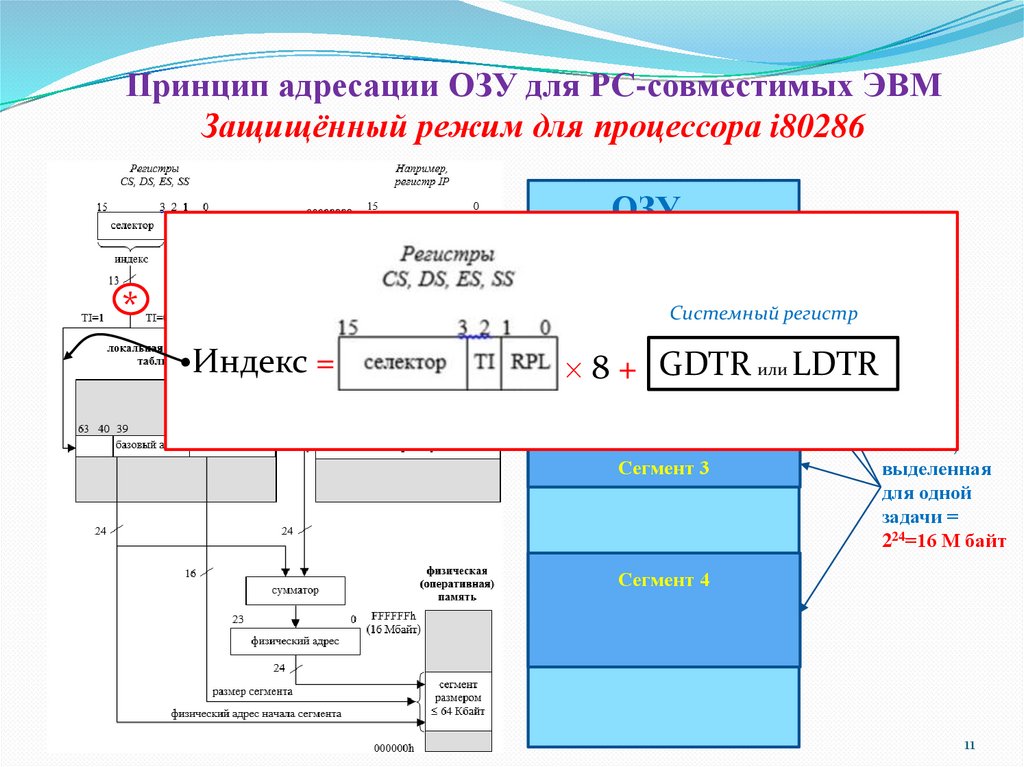

Принцип адресации ОЗУ для РС-совместимых ЭВМЗащищённый режим для процессора i80286

ОЗУ

*

Системный регистр

Сегмент 1

Индекс =

GDTR или LDTR

8+

Сегмент 2

Сегмент 3

Память,

выделенная

для одной

задачи =

224=16 М байт

Сегмент 4

11

12.

Принцип адресации ОЗУ для РС-совместимых ЭВМЗащищённый режим для процессора i80286

ОЗУ

Сегмент 1

Сегмент 2

Сегмент 3

Память,

выделенная

для одной

задачи =

224=16 М байт

Сегмент 4

Адресуемая ячейка памяти

≤ 64Кбайта

12

13.

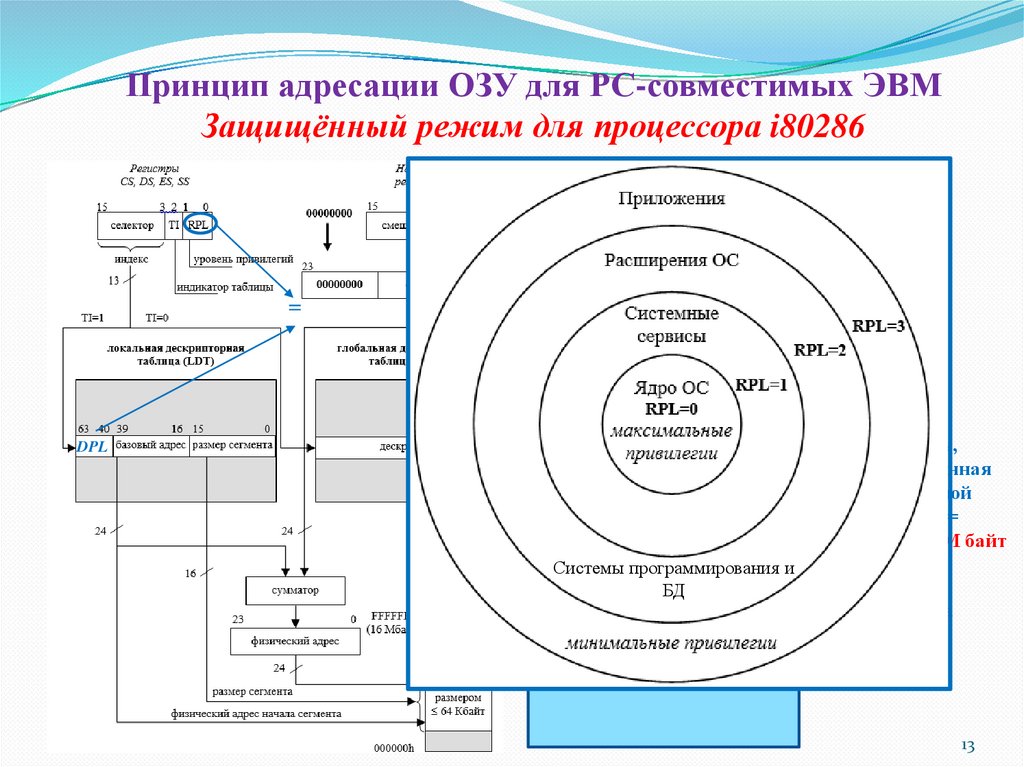

Принцип адресации ОЗУ для РС-совместимых ЭВМЗащищённый режим для процессора i80286

ОЗУ

=

Сегмент 1

Сегмент 2

DPL

Сегмент 3

Системы программирования и

Сегмент 4

БД

Адресуемая ячейка памяти

Память,

выделенная

для одной

задачи =

224=16 М байт

≤ 64Кбайта

13

14.

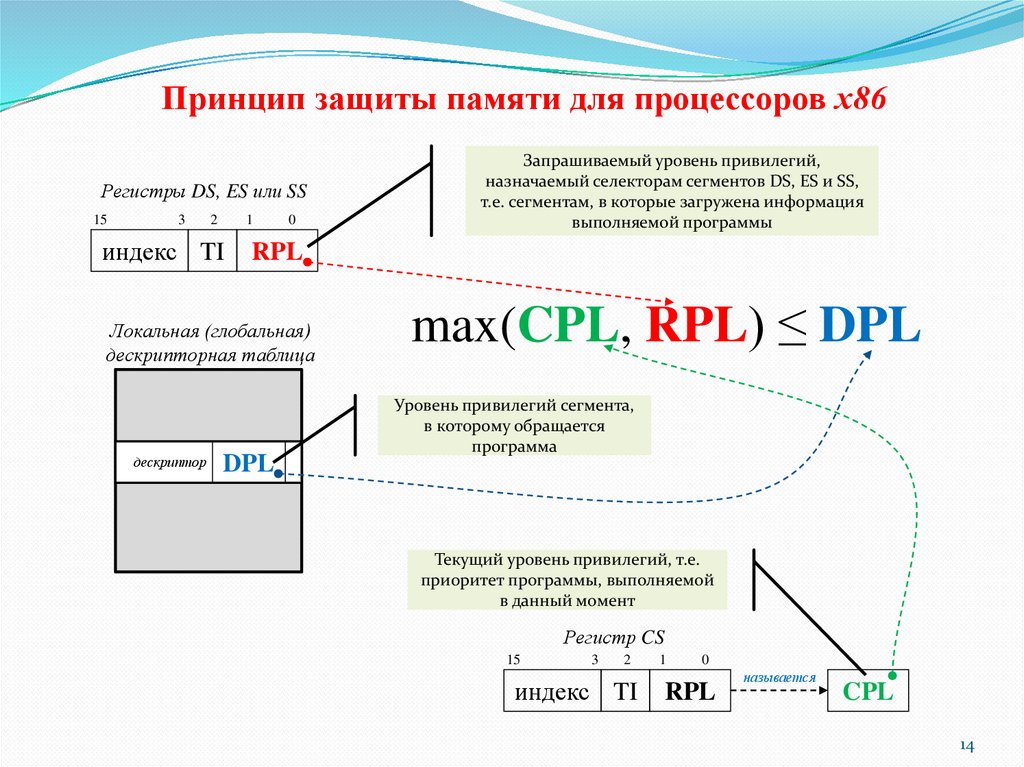

Принцип защиты памяти для процессоров х86Регистры DS, ES или SS

15

3

2

1

индекс TI

0

RPL

Локальная (глобальная)

дескрипторная таблица

дескриптор

Запрашиваемый уровень привилегий,

назначаемый селекторам сегментов DS, ES и SS,

т.е. сегментам, в которые загружена информация

выполняемой программы

DPL

max(CPL, RPL) ≤ DPL

Уровень привилегий сегмента,

в которому обращается

программа

Текущий уровень привилегий, т.е.

приоритет программы, выполняемой

в данный момент

Регистр CS

15

3

2

индекс TI

1

0

RPL

называется

CPL

14

15.

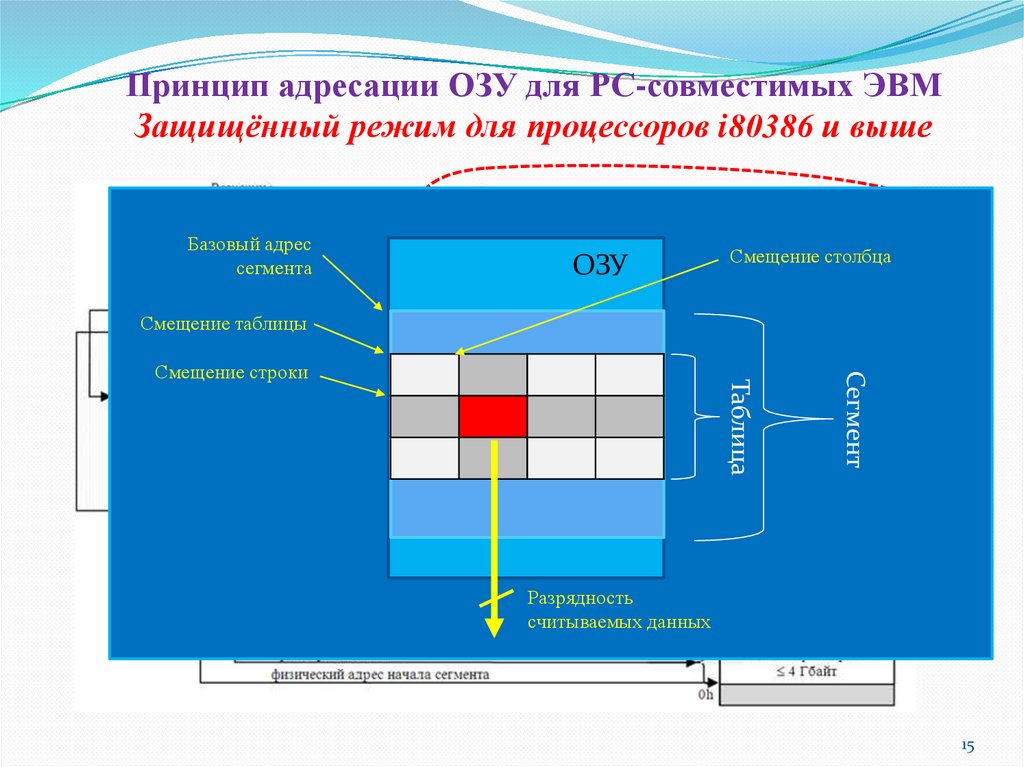

Принцип адресации ОЗУ для РС-совместимых ЭВМЗащищённый режим для процессоров i80386 и выше

Базовый адрес

сегмента

ОЗУ

Смещение столбца

Смещение таблицы

Сегмент

Таблица

Смещение строки

Разрядность

считываемых данных

15

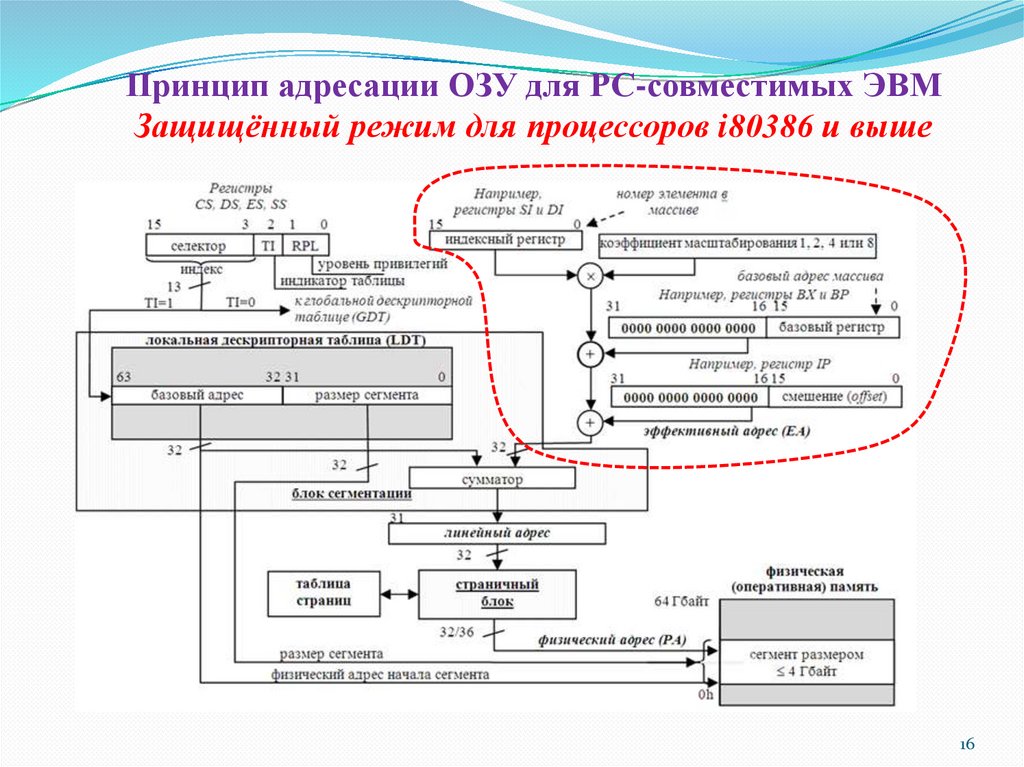

16.

Принцип адресации ОЗУ для РС-совместимых ЭВМЗащищённый режим для процессоров i80386 и выше

16

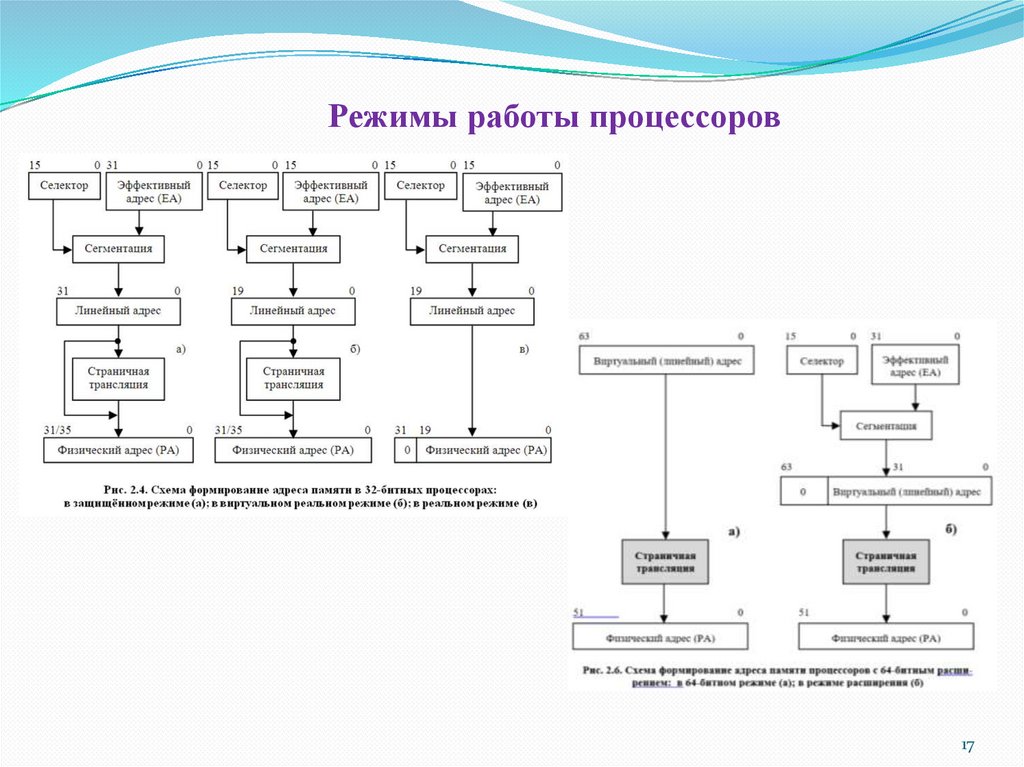

17.

Режимы работы процессоров17

18.

Страничное преобразование адреса18

electronics

electronics