Similar presentations:

Система удаленного реконфигурирования, отладки и тестирования карт электроники для детектора TPC/MPD проекта NICA

1.

ВСЕРОССИЙСКАЯ ШКОЛА-КОНФЕРЕНЦИЯГОСУДАРСТВЕННОГО УНИВЕРСИТЕТА «ДУБНА»:

«ФУНДАМЕНТАЛЬНАЯ ФИЗИКА И ПРИКЛАДНЫЕ

ТЕХНОЛОГИИ»

Система удаленного

реконфигурирования, отладки и

тестирования карт электроники для

детектора TPC/MPD проекта NICA

ПОТАПОВ ДЕНИС СЕРГЕЕВИЧ

Дубна, 2022

ГУ«ДУБНА», ОИЯИ

2.

Актуальность2

Актуальность работы заключается в том, что она

выполняется в рамках работ с детекторной электроники

детектора TPC/MPD коллайдера NICA.

3.

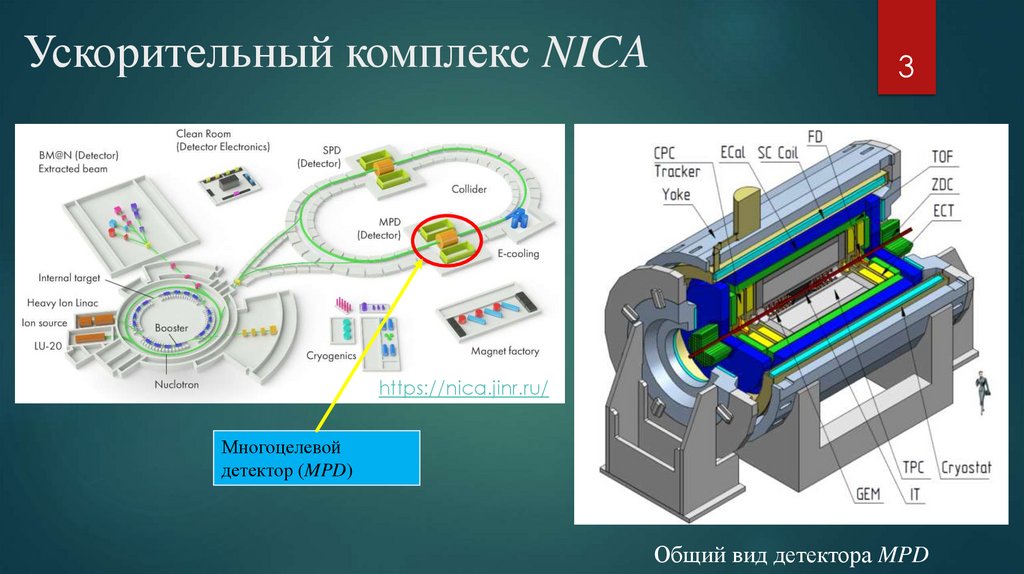

Ускорительный комплекс NICA3

https://nica.jinr.ru/

Многоцелевой

детектор (MPD)

Общий вид детектора MPD

4.

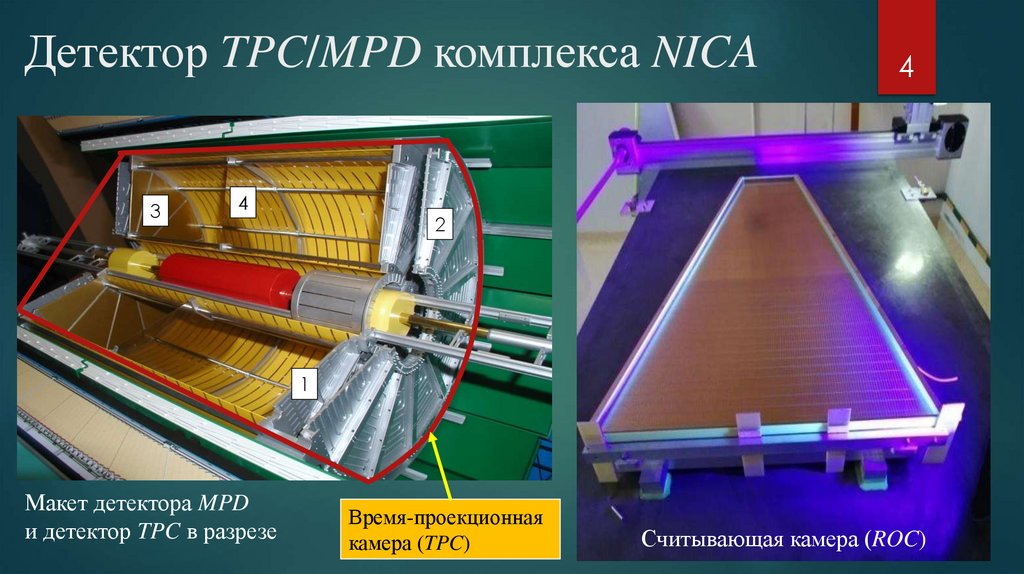

Детектор TPC/MPD комплекса NICA4

1. Место установки карт

3

электроники;

4

2

2. Экран системы

термостабилизации;

3. Многопроволочная

пропорциональная камера (МПК);

4. Высоковольтный электрод;

1

Макет детектора MPD

и детектор TPC в разрезе

Время-проекционная

камера (TPC)

Считывающая камера (ROC)

5.

Карта детекторной электроники (FEC)Подключение программатора к FEC

1 ROC –

62 FECs

24 ROCs –

1488 FECs

Программатор

ROC с детекторной электроникой

SAMPA FEC

Сборка FEC

FEC controller

5

6.

Цель и задачи6

Цель работы - разработать устройство обеспечивающее

удаленный доступ к ПЛИС каждой карты детекторной

электроники, расположенной на считывающей камере.

Задачи работы:

Разработать концепцию устройства;

Разработать устройство;

Протестировать базовые функции устройства;

Проверить целостность данных при записи и чтении в

память ПЛИС.

7.

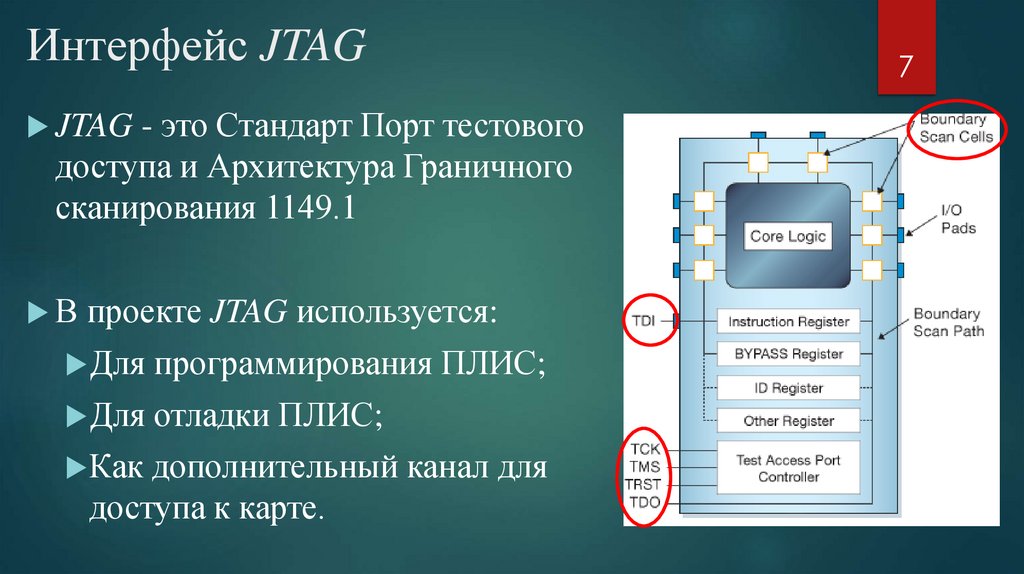

Интерфейс JTAGJTAG - это Стандарт Порт тестового

доступа и Архитектура Граничного

сканирования 1149.1

В проекте JTAG используется:

Для программирования ПЛИС;

Для отладки ПЛИС;

Как дополнительный канал для

доступа к карте.

7

8.

Блок-схема работы устройстваJTAG_Switch

Кнопка сброса

1-й разъем

JTAG

Выходной

разъем JTAG JTAG

7-й разъем

3

Конфигурационный

переключатель

3-й переключатель

JTAG_Switch

FEC 1

Карта детекторной

электроники

…

JTAG

7

…

Одноплатный

компьютер и/или

Raspberry PI

Конфигурационный

переключатель

7

Выходной

разъем JTAG JTAG

…

1-й переключатель

SCANSTA112

…

Программатор

Входной

USB Blaster

JTAG разъем JTAG JTAG

8

7

Карта детекторной

электроники

FEC 7

9.

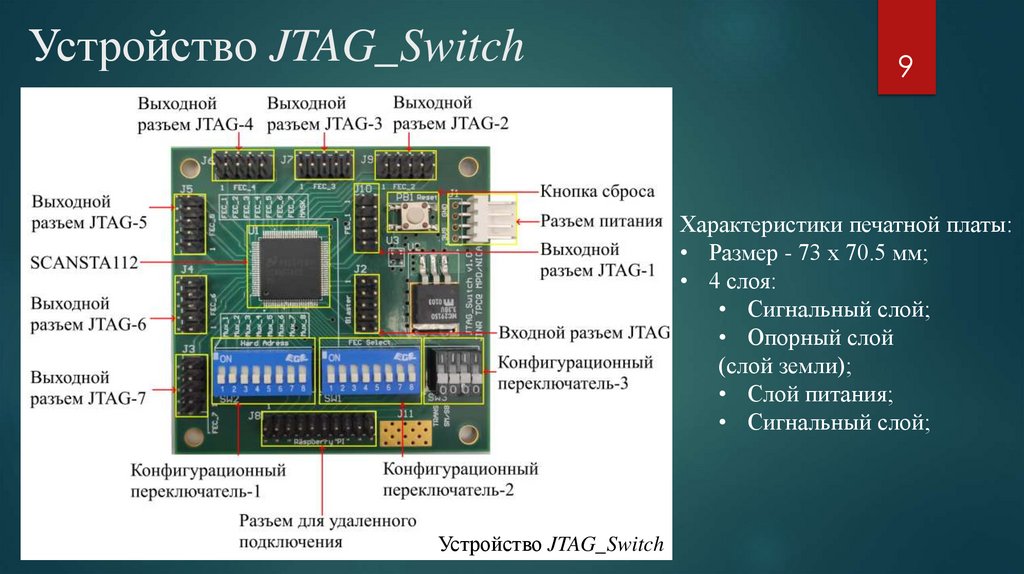

Устройство JTAG_Switch9

Характеристики печатной платы:

• Размер - 73 х 70.5 мм;

• 4 слоя:

• Сигнальный слой;

• Опорный слой

(слой земли);

• Слой питания;

• Сигнальный слой;

Устройство JTAG_Switch

10.

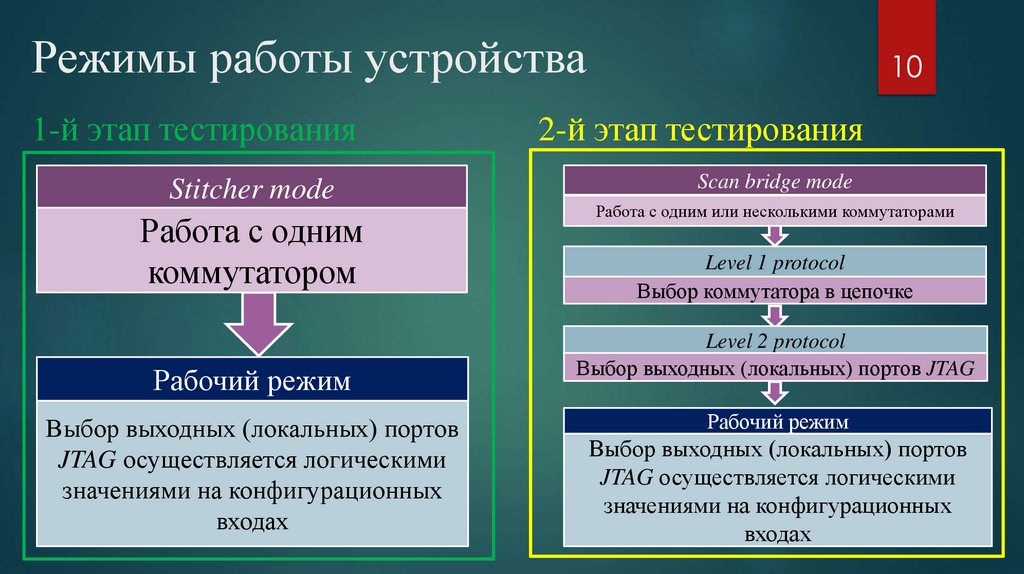

Режимы работы устройства1-й этап тестирования

Stitcher mode

Работа с одним

коммутатором

Рабочий режим

Выбор выходных (локальных) портов

JTAG осуществляется логическими

значениями на конфигурационных

входах

10

2-й этап тестирования

Scan bridge mode

Работа с одним или несколькими коммутаторами

Level 1 protocol

Выбор коммутатора в цепочке

Level 2 protocol

Выбор выходных (локальных) портов JTAG

Рабочий режим

Выбор выходных (локальных) портов

JTAG осуществляется логическими

значениями на конфигурационных

входах

11.

Блок-схема работы тестового стенда11

Карта детекторной электроники

ПЛИС Cyclone V

JTAG master

FEC 1

JTAG

RAM память

JTAG_Switch

SCANSTA112

7

…

…

7

Карта детекторной электроники

Коммутатор JTAG

JTAG

Программатор

USB Blaster

USB 2.0

ПЛИС Cyclone V

JTAG master

FEC 7

RAM память

JTAG

Инструменты

САПР Quartus II

Компьютер

12.

Тестирование устройства JTAG_SwitchПроверка базовых функций

Стенд для тестирования

устройства JTAG_Switch

12

Окно инструмента Programmer

13.

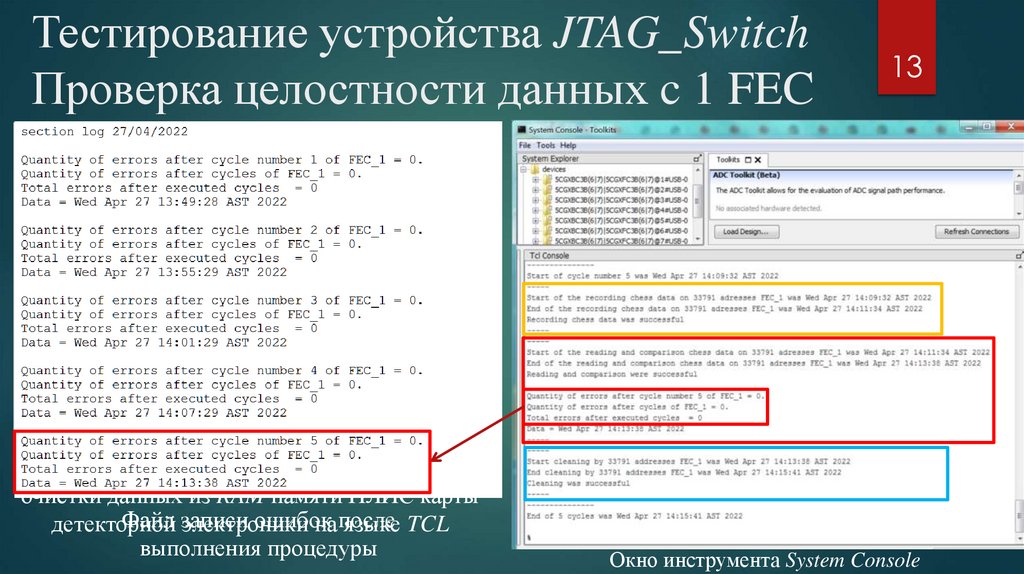

Тестирование устройства JTAG_SwitchПроверка целостности данных c 1 FEC

Процедура записи, чтения, сравнения и

очистки данных из RAM памяти ПЛИС карты

Файл записи

ошибок

детекторной

электроники

напосле

языке TCL

выполнения процедуры

13

Окно инструмента System Console

14.

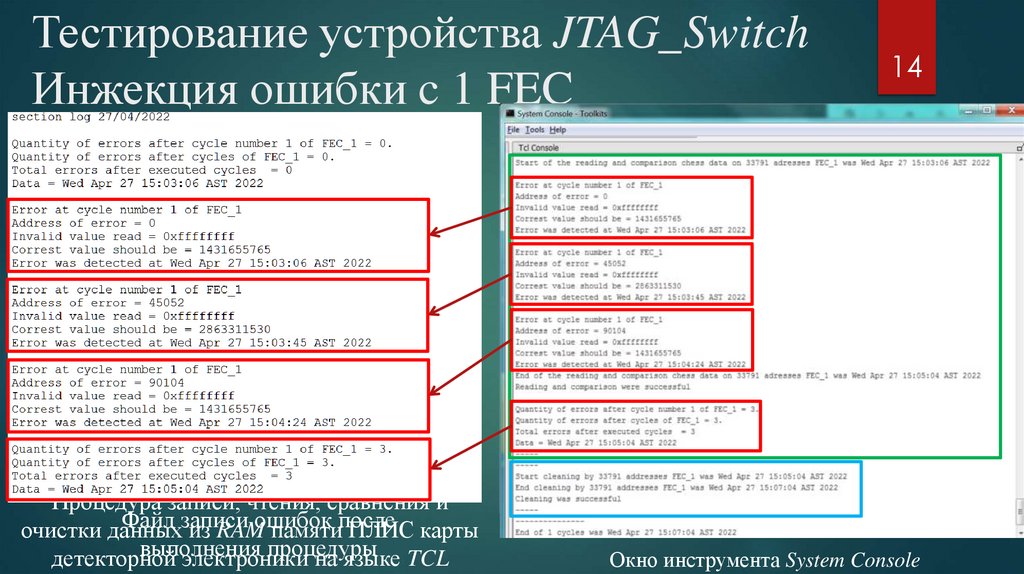

Тестирование устройства JTAG_SwitchИнжекция ошибки c 1 FEC

Процедура записи, чтения, сравнения и

Файл записи

очистки данных

из RAMошибок

памятипосле

ПЛИС карты

выполнения

процедуры

детекторной

электроники

на языке TCL

14

Окно инструмента System Console

15.

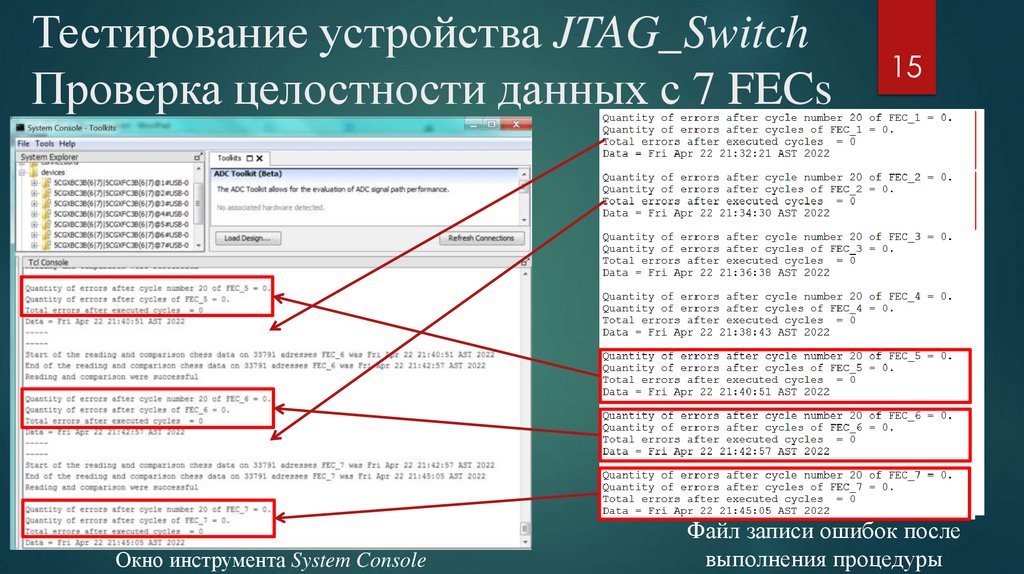

Тестирование устройства JTAG_SwitchПроверка целостности данных с 7 FECs

Окно инструмента System Console

15

Файл записи ошибок после

выполнения процедуры

16.

Заключение16

В ходе выполнения работы было разработано и протестировано

устройство, способное запрограммировать и отладить семь карт

детекторной электроники;

Исследованы базовые функции устройства;

Выполнена проверка целостности данных при записи и чтении

в память ПЛИС FEC.

Планы

Улучшить автоматизацию системы (2й этап тестирования)

Разработать устройство для управления считывающей камерой.

17.

ВСЕРОССИЙСКАЯ ШКОЛА-КОНФЕРЕНЦИЯГОСУДАРСТВЕННОГО УНИВЕРСИТЕТА «ДУБНА»:

«ФУНДАМЕНТАЛЬНАЯ ФИЗИКА И ПРИКЛАДНЫЕ

ТЕХНОЛОГИИ»

Система удаленного

реконфигурирования, отладки и

тестирования карт электроники для

детектора TPC/MPD проекта NICA

ПОТАПОВ ДЕНИС СЕРГЕЕВИЧ

Дубна, 2022

ГУ«ДУБНА», ОИЯИ

electronics

electronics