Similar presentations:

Цифровые устройства и микропроцессоры. Лекция №5. Интегральные триггеры

1.

ВОЕННАЯ АКАДЕМИЯ ВОЗДУШНО-КОСМИЧЕСКОЙ ОБОРОНЫИМЕНИ МАРШАЛА СОВЕТСКОГО СОЮЗА Г.К. ЖУКОВА

Кафедра № 13

основ построения радиоэлектронных средств и систем

Учебная дисциплина Д-1321

«ЦИФРОВЫЕ УСТРОЙСТВА И

МИКРОПРОЦЕССОРЫ»

Тверь 2018

2.

СТРУКТУРА УЧЕБНОЙ ДИСЦИПЛИНЫ ДС-1321Номера и наименование

разделов и тем

Всего

часов

Из них по видам занятий

Лекции Лаб.раб. Пр.зан.

Зачет

5 семестр

Введение

2

2

Тема 1. Основы схемотехники и элементная база

комбинационных цифровых электронных

устройств

14

6

4

4

Тема 2. Основы схемотехники и элементная база

последовательностных цифровых электронных

устройств

24

10

8

6

Тема 3. Аналого-цифровые и цифро-аналоговые 10

преобразователи

4

4

2

Тема 4. Запоминающие устройства ЭВМ и МПС

8

4

2

2

Тема 5. Микропроцессоры и микропроцессорные

системы

26

16

Заключение

2

2

Зачет с оценкой в конце 5-го семестра

4

Всего по дисциплине

90

10

4

44

18

24

4

3.

Содержание темы 2«Основы схемотехники и элементная база последовательностных

цифровых электронных устройств»

Номера и вид

занятий

Лекция № 4

Наименование тем занятий

Математическое описание последовательностных

цифровых устройств

Пр.занятие №3 Синтез последовательностных цифровых устройств

Лекция №5

Интегральные триггеры

Пр.занятие №4 Анализ и расчет триггеров

Лаб. работа №2

Экспериментальное исследование интегральных

триггеров

Лекция № 6

Счетчики

Лекция № 7

Регистры.

Пр.занятие №5 Анализ и расчет типовых последовательностных

цифровых узлов ЭВМ

исследование типовых

Лаб. работа №3 Экспериментальное

последовательностных цифровых электронных узлов

радиотехнических систем и ЭВМ

4.

ЛЕКЦИЯ №5Интегральные триггеры

5.

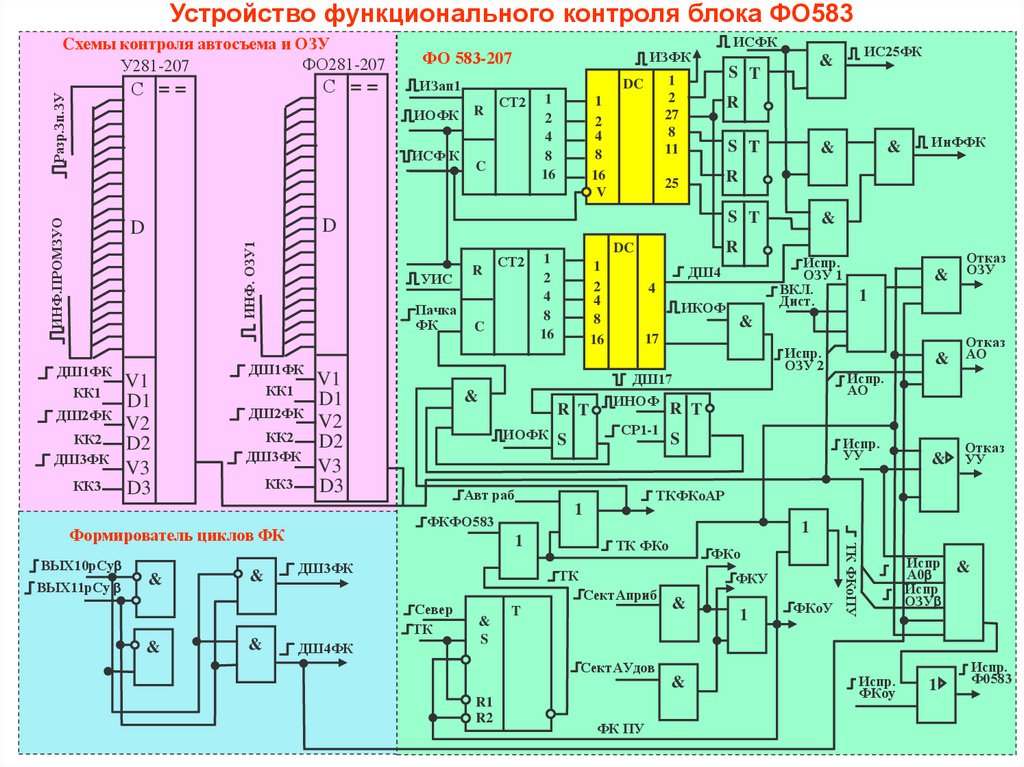

Устройство функционального контроля блока ФО583Cхемы контроля автосъема и ОЗУ

ФО281-207

У281-207

С ==

Разр.Зп.ЗУ

С ==

ФО 583-207

ИЗап1

ИОФК

ИНФ.ПРОМЗУО

ИСФ К

ИНФ. ОЗУ1

ДШ2ФК

КК2

ДШ3ФК

КК3

S T

V1

D1

V2

D2

V3

D3

Пачка

ФК

ДШ1ФК

КК1

ДШ2ФК

КК2

ДШ3ФК

КК3

V1

D1

V2

D2

V3

D3

&

&

&

C

1

2

4

8

16

ИОФК

4

ИКОФ

СР1-1

S

Испр.

ОЗУ 2

Отказ

& АО

Испр.

АО

R T

S

ТК ФКо

Испр.

УУ

ФКо

ТК

ФКУ

СектАприб

T

&

СектАУдов

&

R1

R2

1

&

Отказ

УУ

1

1

&

S

Отказ

ОЗУ

ТКФКоАР

1

ДШ3ФК

&

&

17

ИНОФ

&

Испр.

ОЗУ 1

ВКЛ.

Дист.

ДШ4

Авт раб

ФКФО583

ДШ4ФК

R

ДШ17

R T

ИнФФК

R

25

DC

1

2

4

8

16

&

Север

ТК

&

R

СТ2

&

&

ФК ПУ

1

ФКоУ

ТК ФКоПУ

ВЫХ11рСу

R

S T

УИС

Формирователь циклов ФК

ВЫХ10рСу

C

1

2

4

8

16

V

D

D

ДШ1ФК

КК1

СТ2

1

2

4

8

16

ИС25ФК

&

S T

1

2

27

8

11

DC

R

ИСФК

ИЗФК

Испр.

ФКоу

Испр

А0

Испр

ОЗУ

1

&

Испр.

Ф0583

6.

ФОРМИРУЕМАЯ КОМПЕТЕНЦИЯСпособность учитывать в профессиональной деятельности

современные

тенденции

развития

электроники,

измерительной и вычислительной техники (ОПК-6).

ПЛАНИРУЕМЫЕ РЕЗУЛЬТАТЫ ОБУЧЕНИЯ

ЗНАТЬ:

основы схемотехники и элементную базу цифровых

электронных устройств, архитектуру, условия и способы

использования микропроцессоров и микропроцессорных

систем в электронных устройствах.

УЧЕБНАЯ ЦЕЛЬ ЛЕКЦИИ

Систематизировать основы научных знаний по схемотехнике

и элементной базе интегральных триггеров.

7.

УЧЕБНЫЕ ВОПРОСЫ ЛЕКЦИИ1. Общие сведения о триггерах.

2. Одноступенчатые интегральные триггеры.

3. Двухступенчатые интегральные триггеры.

8.

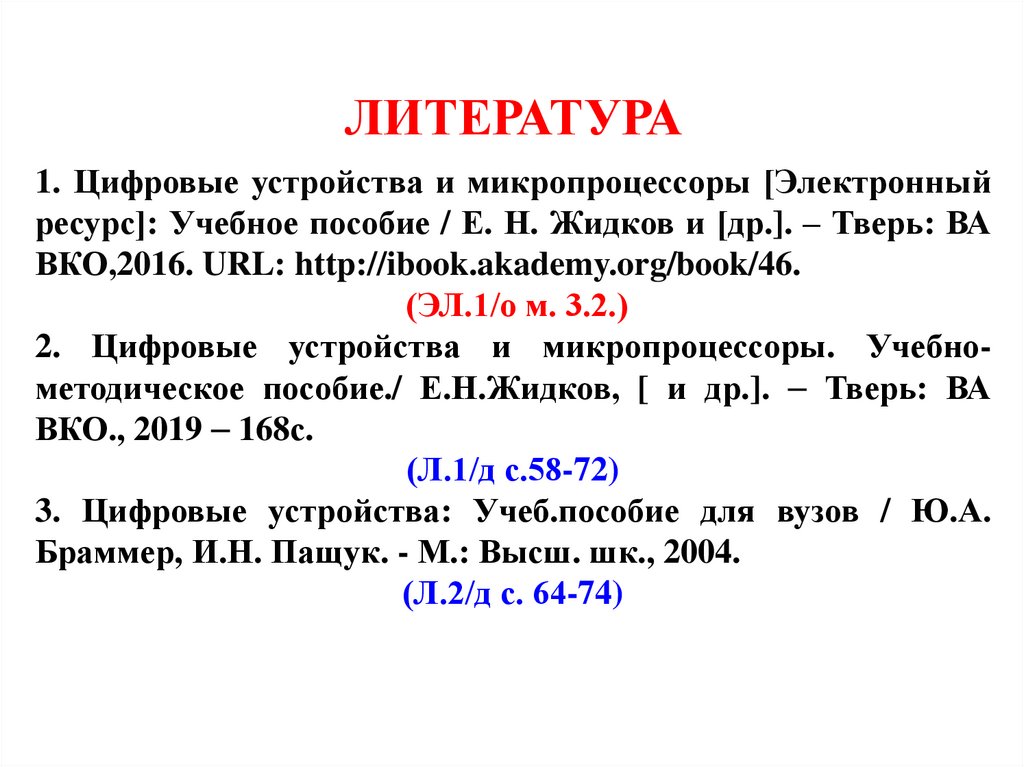

ЛИТЕРАТУРА1. Цифровые устройства и микропроцессоры [Электронный

ресурс]: Учебное пособие / Е. Н. Жидков и [др.]. – Тверь: ВА

ВКО,2016. URL: http://ibook.akademy.org/book/46.

(ЭЛ.1/о м. 3.2.)

2. Цифровые устройства и микропроцессоры. Учебнометодическое пособие./ Е.Н.Жидков, [ и др.]. Тверь: ВА

ВКО., 2019 168с.

(Л.1/д с.58-72)

3. Цифровые устройства: Учеб.пособие для вузов / Ю.А.

Браммер, И.Н. Пащук. - М.: Высш. шк., 2004.

(Л.2/д с. 64-74)

9.

1. Общие сведения о триггерах10.

Понятие триггераСтруктурная схема простейшего триггера и его

принцип действия

Разновидности входов триггеров и их условные

графические обозначения

Классификация и параметры триггеров

11.

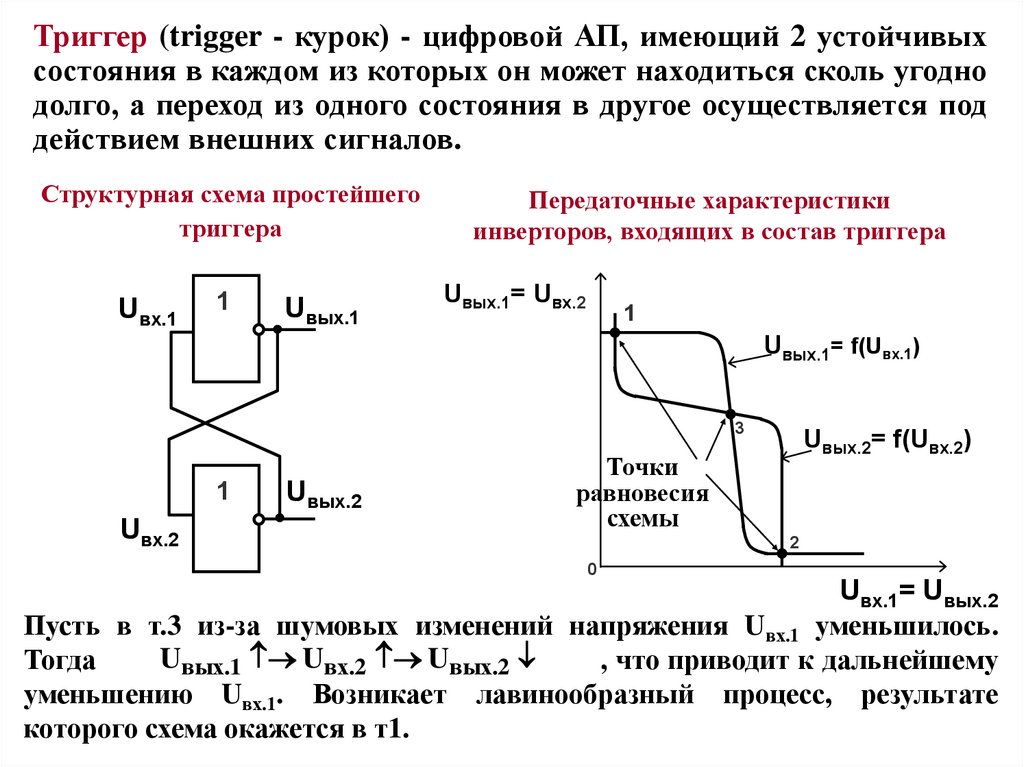

Триггер (trigger - курок) - цифровой АП, имеющий 2 устойчивыхсостояния в каждом из которых он может находиться сколь угодно

долго, а переход из одного состояния в другое осуществляется под

действием внешних сигналов.

Структурная схема простейшего

триггера

Uвх.1

1

Uвых.1

Передаточные характеристики

инверторов, входящих в состав триггера

Uвых.1= Uвх.2

1

Uвых.1= f(Uвх.1)

3

1

Uвх.2

Uвых.2

Uвых.2= f(Uвх.2)

Точки

равновесия

схемы

2

0

Uвх.1= Uвых.2

Пусть

в1,2т.3

из-за устойчивого

шумовых

изменений

напряжения

Uвх.1при

уменьшилось.

Точки

точки

равновесия.

Действительно,

если

Uвых.1=U1

ВТочка

метастабильном

состоянии

триггер может

оказаться

включении

3 -соответствует

неустойчивому

(метастабильному)

состоянию

Uавых

U

Uвых

Тогда

, что

приводит

к дальнейшему

1, .а1

0 .2

вх.2Uкратковременно,

,питания,

то Uвх.2существующему

=U

значит

в свою

очередь

удерживает

также

при

воздействии

сигналов,

имеющих

предельносхемы,

после

чего

схема случайным

вых.2=U , которое

уменьшению

Возникает

лавинообразный

процесс, результате

1 ЕслиUU

0 то U

1

вх.1. =U

U

=U

допустимые

значения

уровню. состояний.

образом

оказывается

ввых.2

одном

изиустойчивых

вых.1=U . вновь

вых.1 по, длительности

которого схема окажется в т1.

12.

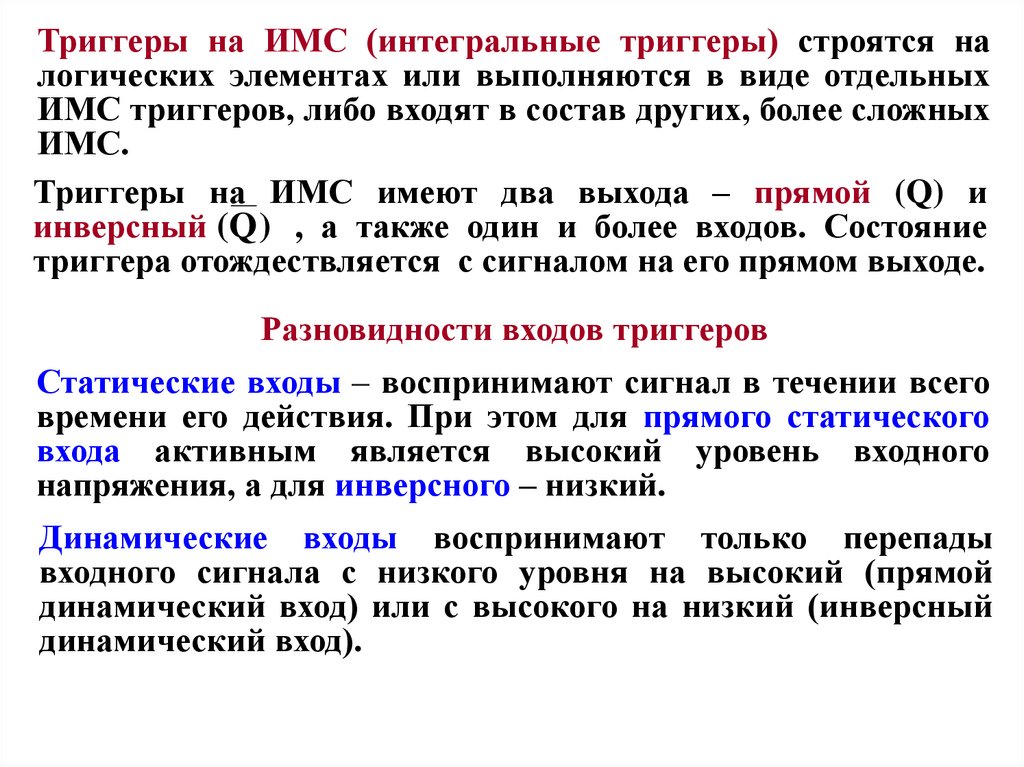

Триггеры на ИМС (интегральные триггеры) строятся налогических элементах или выполняются в виде отдельных

ИМС триггеров, либо входят в состав других, более сложных

ИМС.

Триггеры на ИМС имеют два выхода – прямой (Q) и

инверсный (Q ) , а также один и более входов. Состояние

триггера отождествляется с сигналом на его прямом выходе.

Разновидности входов триггеров

Статические входы – воспринимают сигнал в течении всего

времени его действия. При этом для прямого статического

входа активным является высокий уровень входного

напряжения, а для инверсного – низкий.

Динамические входы воспринимают только перепады

входного сигнала с низкого уровня на высокий (прямой

динамический вход) или с высокого на низкий (инверсный

динамический вход).

13.

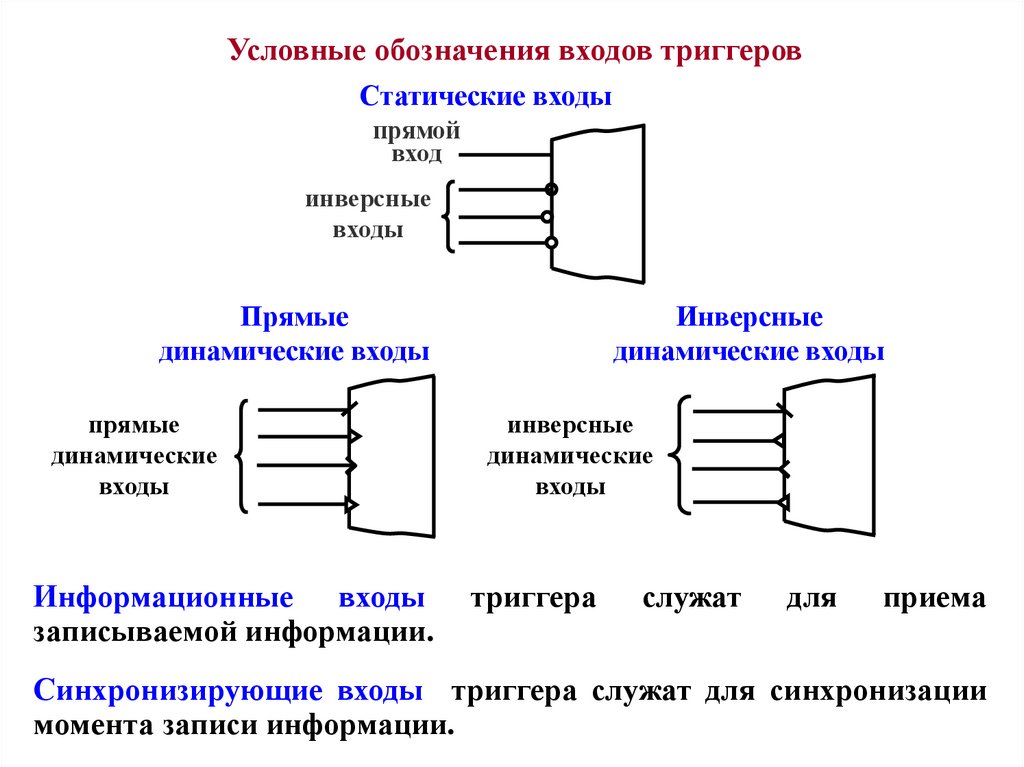

Условные обозначения входов триггеровСтатические входы

прямой

вход

инверсные

входы

Прямые

динамические входы

прямые

динамические

входы

Информационные входы

записываемой информации.

Инверсные

динамические входы

инверсные

динамические

входы

триггера

служат

для

приема

Синхронизирующие входы триггера служат для синхронизации

момента записи информации.

14.

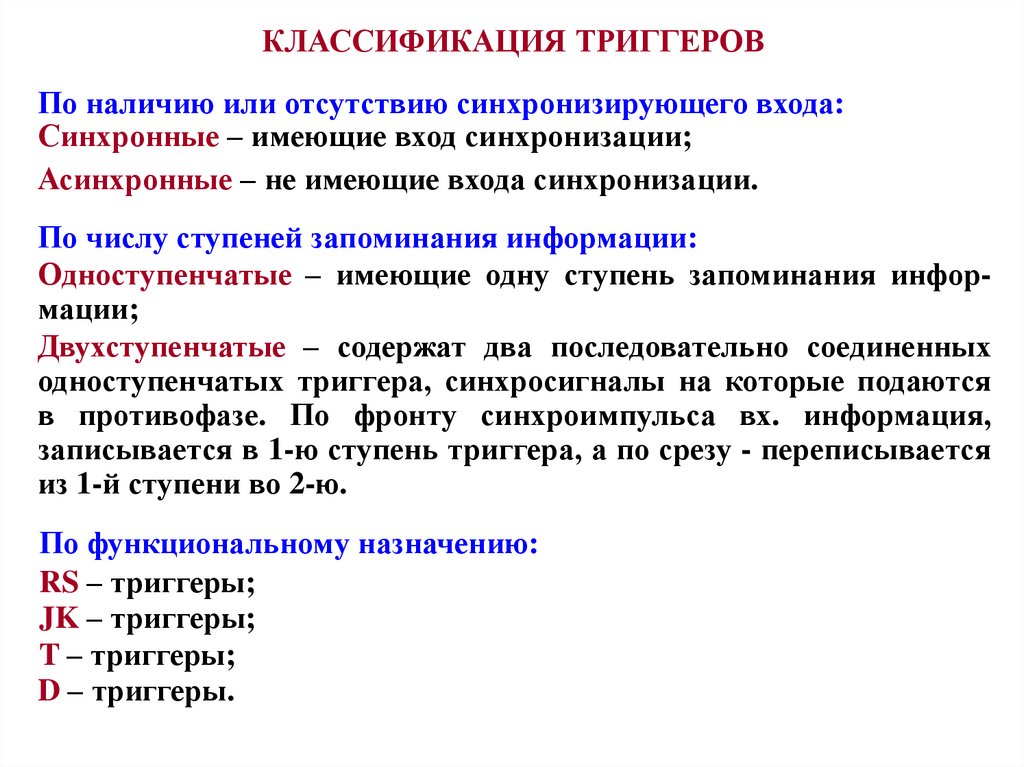

КЛАССИФИКАЦИЯ ТРИГГЕРОВПо наличию или отсутствию синхронизирующего входа:

Синхронные – имеющие вход синхронизации;

Асинхронные – не имеющие входа синхронизации.

По числу ступеней запоминания информации:

Одноступенчатые – имеющие одну ступень запоминания информации;

Двухступенчатые – содержат два последовательно соединенных

одноступенчатых триггера, синхросигналы на которые подаются

в противофазе. По фронту синхроимпульса вх. информация,

записывается в 1-ю ступень триггера, а по срезу - переписывается

из 1-й ступени во 2-ю.

По функциональному назначению:

RS – триггеры;

JK – триггеры;

T – триггеры;

D – триггеры.

15.

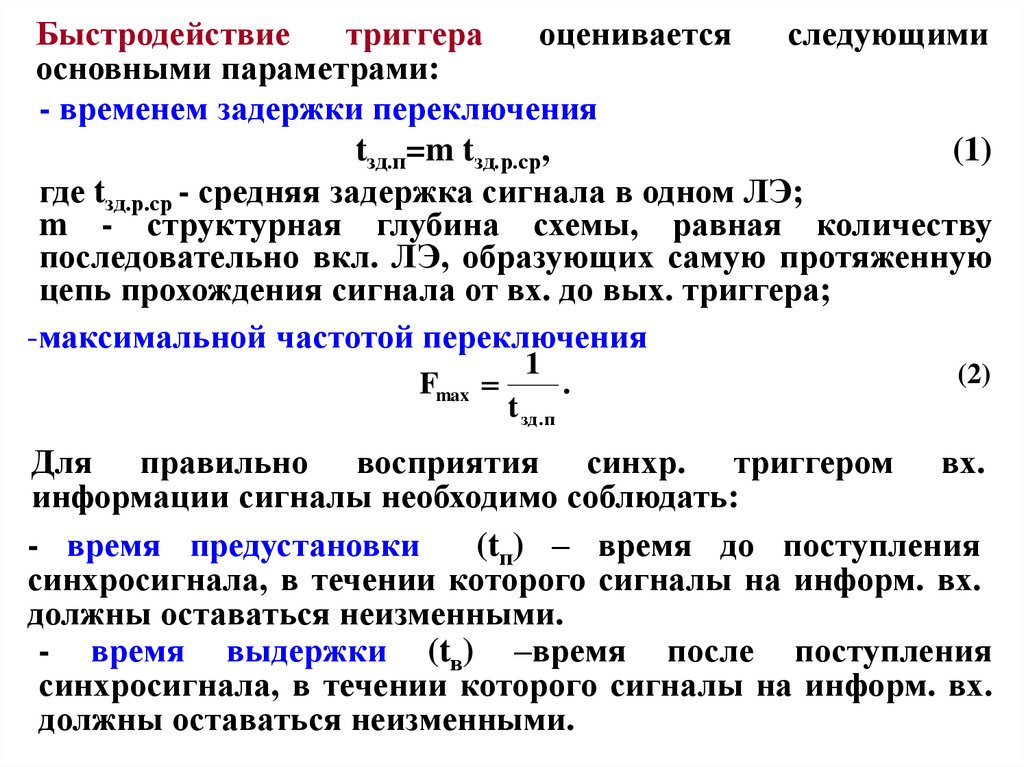

Быстродействиетриггера

оценивается

следующими

основными параметрами:

- временем задержки переключения

tзд.п=m tзд.р.ср,

(1)

где tзд.р.ср - средняя задержка сигнала в одном ЛЭ;

m - структурная глубина схемы, равная количеству

последовательно вкл. ЛЭ, образующих самую протяженную

цепь прохождения сигнала от вх. до вых. триггера;

-максимальной частотой переключения

Fmax

1

t зд .п

.

(2)

Для правильно восприятия синхр. триггером вх.

информации сигналы необходимо соблюдать:

- время предустановки

(tп) – время до поступления

синхросигнала, в течении которого сигналы на информ. вх.

должны оставаться неизменными.

- время выдержки (tв) –время после поступления

синхросигнала, в течении которого сигналы на информ. вх.

должны оставаться неизменными.

16.

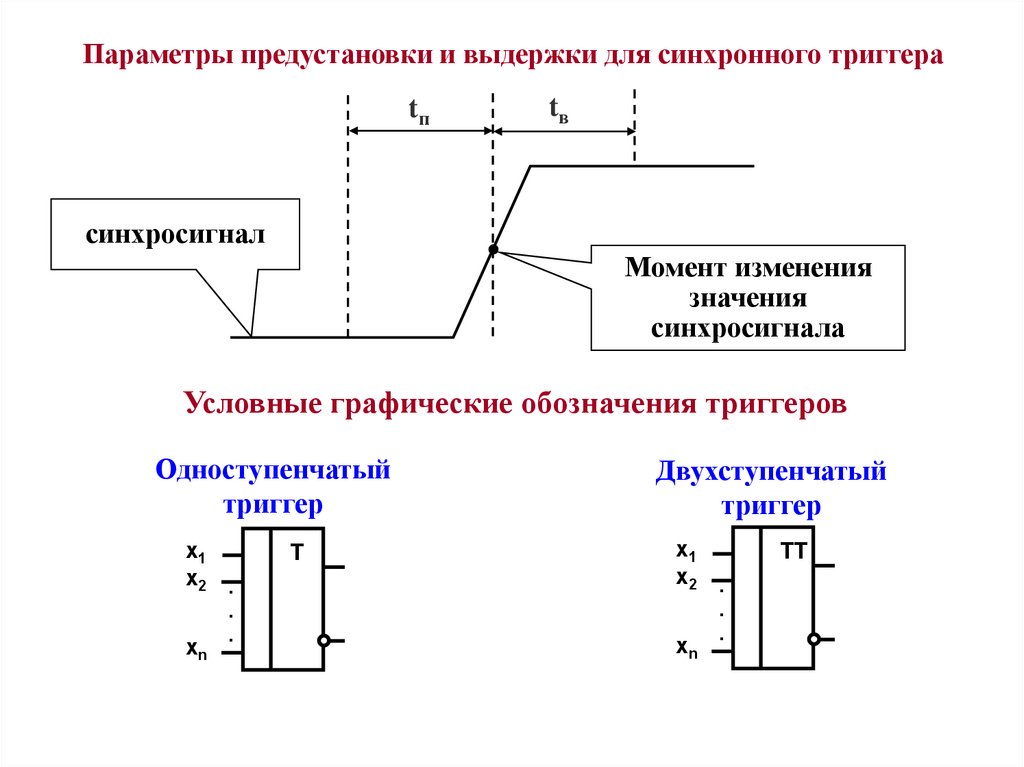

Параметры предустановки и выдержки для синхронного триггераtп

tв

синхросигнал

Момент изменения

значения

синхросигнала

Условные графические обозначения триггеров

Одноступенчатый

триггер

x1

x2 .

xn

.

.

Т

Двухступенчатый

триггер

x1

x2 .

xn

.

.

ТТ

17.

2. Одноступенчатые интегральныетриггеры

18.

Одноступенчатый RS-триггерОдноступенчатый D - триггер

Одноступенчатый T - триггер

Одноступенчатый JK - триггер

Комбинированные триггеры

19.

2.1. Асинхронные RS триггерыАсинхронные RS-триггеры - являются простейшими триггерами,

которые применяются самостоятельно и на основе которых

строятся более сложные схемы триггеров. Асинхронные RS триггеры имеют два информационных входа: S (set - установка) и

R (reset - сброс).

Асинхронный RS-триггер с

прямыми входами

Схема

УГО

S S Т

Q

R

Q

R

Асинхронный RS-триггер с

инверсными входами

R

1

S

1

УГО

Q

S S Т

Q

Q

R

Q

R

Таблица переходов

S

R

Схема

&

Q

&

Q

Таблица переходов

n 1

n 1

Sn

Rn

Qn 1

0

0

н/о

н/о

1

0

1

1

0

1

0

1

0

0

1

н/о

н/о

1

1

Qn

Q

Sn

Rn

Qn 1

0

0

Qn

Q

0

1

0

1

0

1

1

Q

n

Q

n

20.

2.2. Синхронный RS-триггерУГО

S

C

R

S

Т

Схема

Q

C

R

Q

S

Таблица переходов

DD1

q1 DD3

&

& Q

С

R

&

DD2

q2

&

Q

DD4

При С=1 схема функционирует как асинхр. RS- триггер

с прямыми входами. Если С=0, то триггер не изменяет

своего состояния при любой комбинации сигналов на

входах S и R, т.к. в этом случае q1=q2=q=1, что является

нейтральным набором для асинхр. RS –триггера с

инверсн. Входами на элементах DD3 и DD4. Сигналы

на информ. входах S и R подготавливают триггер к

срабатыванию,

тогда

как

непосредственно

срабатывание происходит в момент поступления

синхроимпульсов на вход С.

n 1

Сn

Sn

Rn

Qn 1

Q

0

0

0

Qn

Q

0

0

1

Qn

Q

0

1

0

Qn

Q

0

1

1

Qn

Q

1

0

0

Qn

Q

1

0

1

0

1

1

1

0

1

0

1

1

1

н/о

н/о

n

n

n

n

n

21.

2.3. Cинхронный D-триггерСинхронный D-триггер при наличии синхронизирующего сигнала

на входе С устанавливается в состояние, соответствующее

значению сигнала на информационном входе D. Обозначение входа

D- происходит от слова delay (задержка).

Cинхронный D-триггер со статическим входом синхронизации

УГО

Схема

Таблица переходов

D

n 1

n

n

n+1

C

D

Q

Q

D

&

Q

D Т

& Q

0

0

Qn

Qn

0

1

Qn

Qn

C

Q

Q

С

C

&

&

1

0

0

1

1

1

1

0

У синхронных триггеров со статическим входом синхронизации если во время действия

импульса синхронизации изменяется значение сигналов на на информационных входах,

это изменение передается на выход.

Cинхронный D-триггер с динамическим входом синхронизации

D

C

D

С

Т

Q

Q

Если во время действия импульса синхронизации

изменяется значение сигнала на входе D, это

изменение не передается на выход.

22.

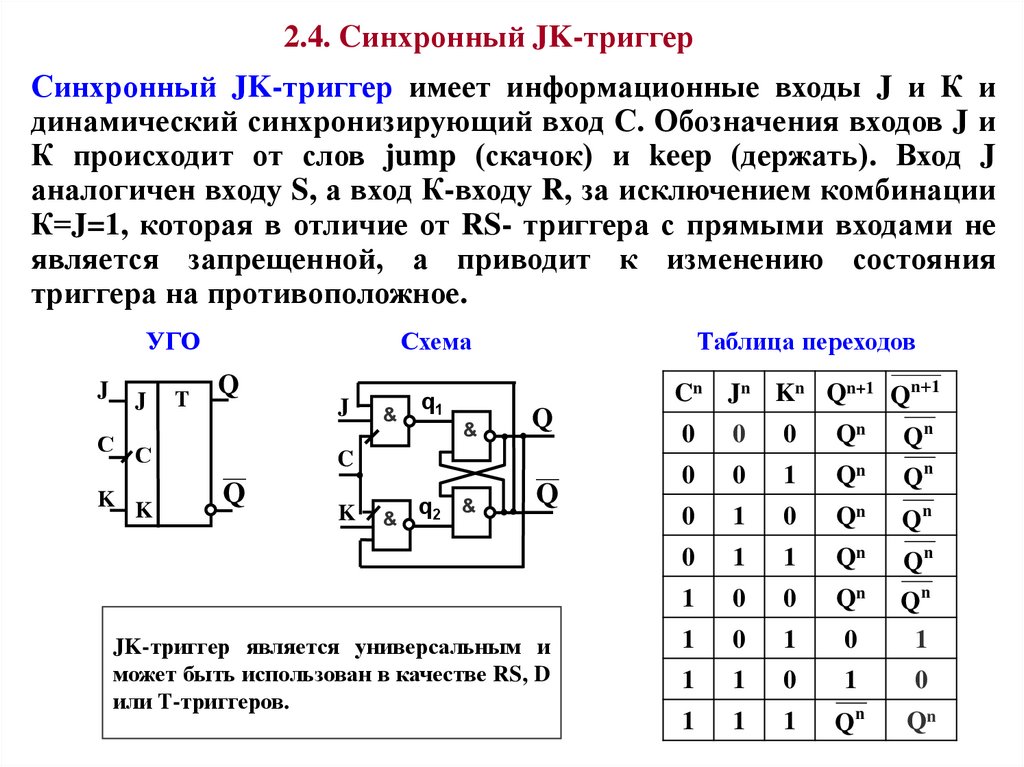

2.4. Cинхронный JK-триггерСинхронный JK-триггер имеет информационные входы J и К и

динамический синхронизирующий вход С. Обозначения входов J и

К происходит от слов jump (скачок) и keep (держать). Вход J

аналогичен входу S, а вход К-входу R, за исключением комбинации

К=J=1, которая в отличие от RS- триггера с прямыми входами не

является запрещенной, а приводит к изменению состояния

триггера на противоположное.

УГО

J

J

Т

Q

С С

K K

J

&

Схема

Таблица переходов

q1

Cn Jn Kn Qn+1 Qn 1

&

Q

C

Q

K

&

q2 &

Q

JK-триггер является универсальным и

может быть использован в качестве RS, D

или Т-триггеров.

0

0

0

Qn

Qn

0

0

1

Qn

Qn

0

1

0

Qn

Qn

0

1

1

Qn

Qn

1

0

0

Qn

1

0

1

0

Qn

1

1

1

0

1

0

1

1

1

Qn

Qn

23.

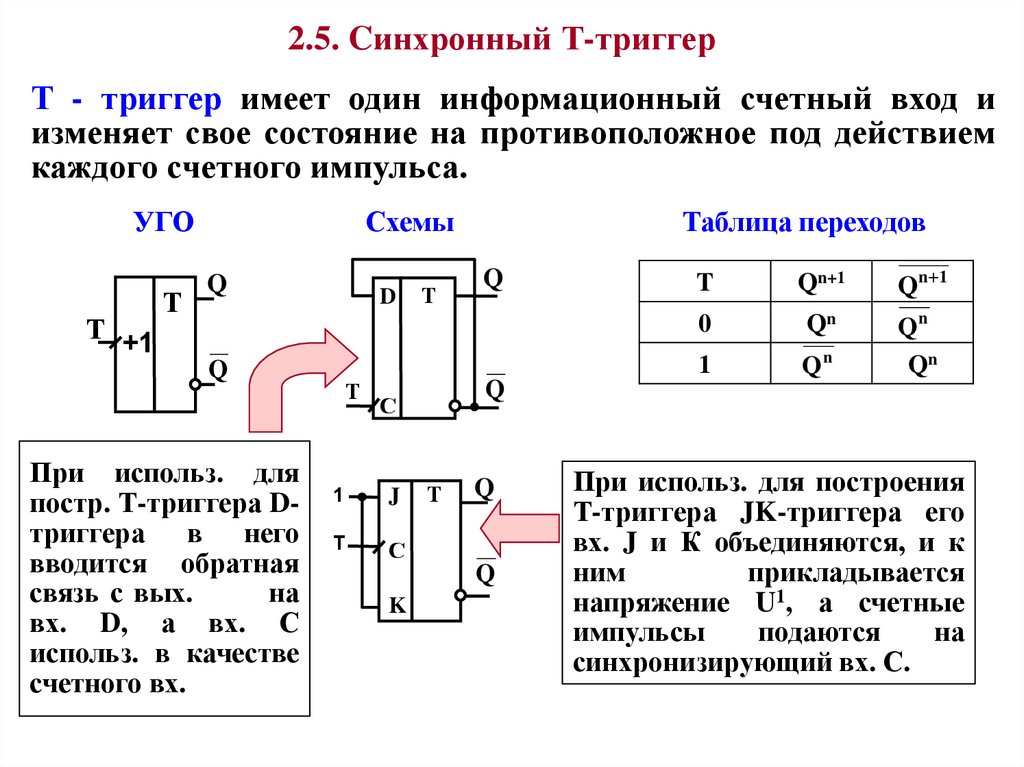

2.5. Cинхронный Т-триггерТ - триггер имеет один информационный счетный вход и

изменяет свое состояние на противоположное под действием

каждого счетного импульса.

УГО

Т +1

Т

Схемы

Q

D

Q

При использ. для

постр. Т-триггера Dтриггера в него

вводится обратная

связь с вых.

на

вх. D, а вх. С

использ. в качестве

счетного вх.

Т

Т

J

Т

С

Q

Т

Q

Q

K

T

Qn+1

Qn 1

0

Qn

1

Qn

Qn

Qn

Q

С

1

Таблица переходов

При использ. для построения

Т-триггера JK-триггера его

вх. J и К объединяются, и к

ним

прикладывается

напряжение U1, а счетные

импульсы

подаются

на

синхронизирующий вх. С.

24.

Примеры применения одноступенчатых триггеровПрименение D-триггера

для построения однофазного

регистра памяти

D0

D1

D

C

D

C

C

Т

Т

Применение RS-триггера

для построения парафазного

регистра памяти

D0

Q0

Q1

В составе регистров

триггеры

используются для

запоминания разрядов

(бит) двоичного слова.

Каждый триггер

запоминает 1 бит.

S

Т

Q0

C

D0

D1

R

S

Т

Q0

Q1

C

D1

C

R

Q1

25.

Применение синхронного RS- триггера в качествеэлемента памяти статических ОЗУ

Синхронный RS- триггер

VT2

+Uп

VT4

Эл-ный

ключ

Эл-ный

ключ

VT6

VT5

Сигнал

VT1

выбора эл-та

памяти

Инверсный канал R (Q)

VT3

Прямой канал S (Q)

Вх. (вых.) бит данных

RS-триггер обеспечивает хранение 1 бита данных. Запись и считывание

бита данных осуществл. парафазным двоичным кодом, т.е. по прямому и

инверсному каналам.

26.

Применение одноступенчатых Т-триггеровПрименение Т-триггера

для деления частоты входных импульсов на 2

Т

Q

Твх

t

Твых=2Твх

t

С помощью Т-триггера можно

уменьшить частоту следования

входных импульсов в 2 раза,

что используется при

построении делителей частоты.

Fвых=Fвх/2

Применение Т-триггера

для счета количества входных импульсов

№ входного импульса

Состояние

триггера

1

1

2

0

3

1

4

0

С помощью Т-триггера можно

суммировать количество

импульсов поступивших на его

вход и запоминать младший

разряд суммы, что используется

при построении счетчиков

27.

3. Двухступенчатые интегральныетриггеры

28.

Двухступенчатый RS-триггерДвухступенчатый D - триггер

Двухступенчатый T - триггер

Двухступенчатый JK - триггер

29.

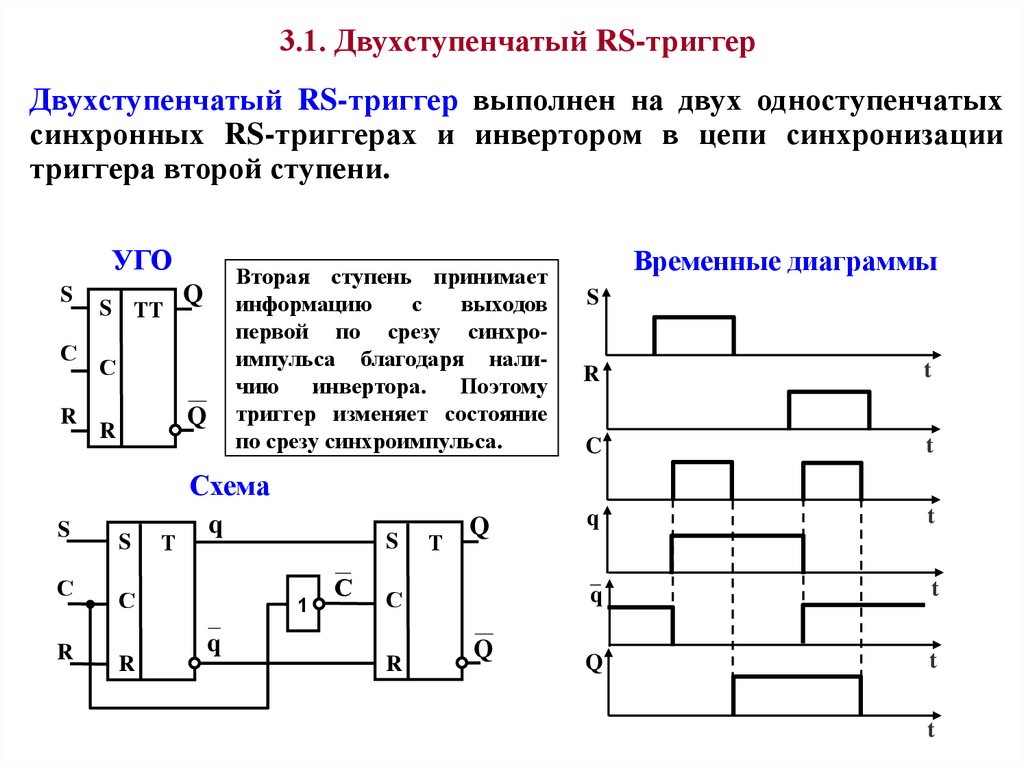

3.1. Двухступенчатый RS-триггерДвухступенчатый RS-триггер выполнен на двух одноступенчатых

синхронных RS-триггерах и инвертором в цепи синхронизации

триггера второй ступени.

УГО

S

С

R

S ТТ

Вторая ступень принимает

информацию

с

выходов

первой по срезу синхроимпульса благодаря наличию инвертора. Поэтому

триггер изменяет состояние

по срезу синхроимпульса.

Q

С

Q

R

Временные диаграммы

S

R

t

C

t

q

t

q

t

Q

t

Схема

S

С

R

S

Т

q

С

R

S

1

q

С

Т

Q

С

R

Q

t

30.

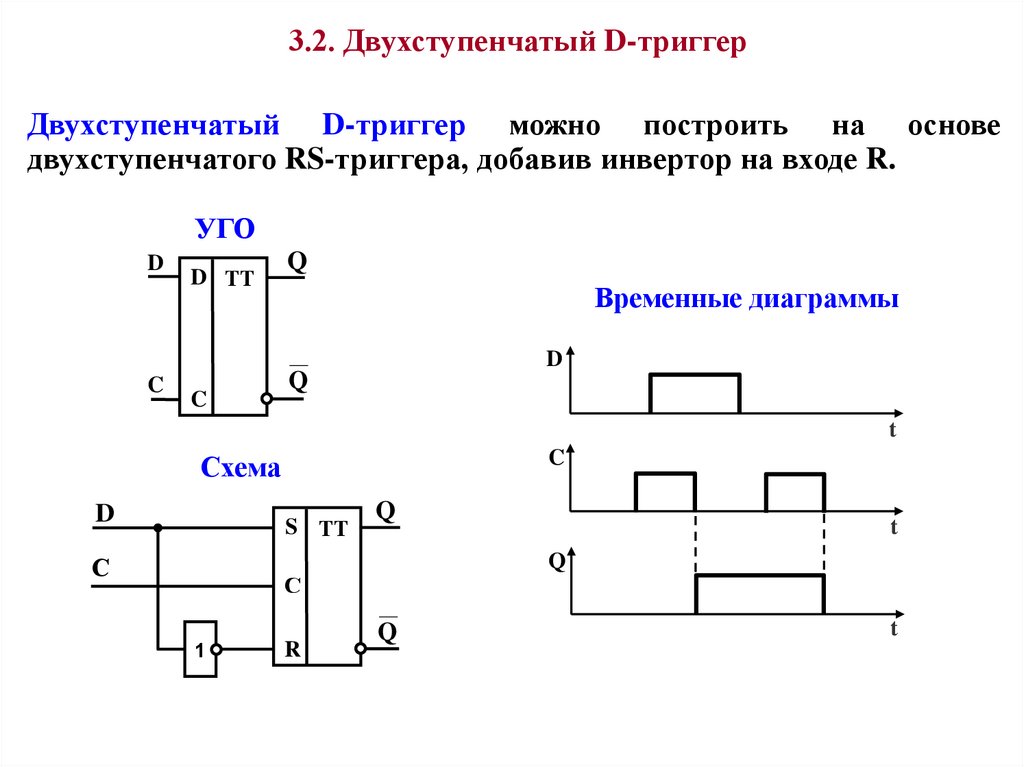

3.2. Двухступенчатый D-триггерДвухступенчатый D-триггер можно построить на основе

двухступенчатого RS-триггера, добавив инвертор на входе R.

УГО

D

D ТТ

Q

Временные диаграммы

D

C

C

Q

t

C

Схема

D

S ТТ

С

Q

Q

С

1

R

t

Q

t

31.

3.3. Двухступенчатый JK-триггерДвухступенчатый JK-триггер можно получить из двухступенчатого

RS- триггера, охватив его перекрестными обратными связями с

выходов Q и Q соответственно на входы R и S через элементы И.

УГО

J

С

K

J ТТ

Временные диаграммы

Q

J

С

t

Q

K

K

Схема

J

&

С

S ТТ

t

Q

t

С

K

&

R

C

Q

Q

t

32.

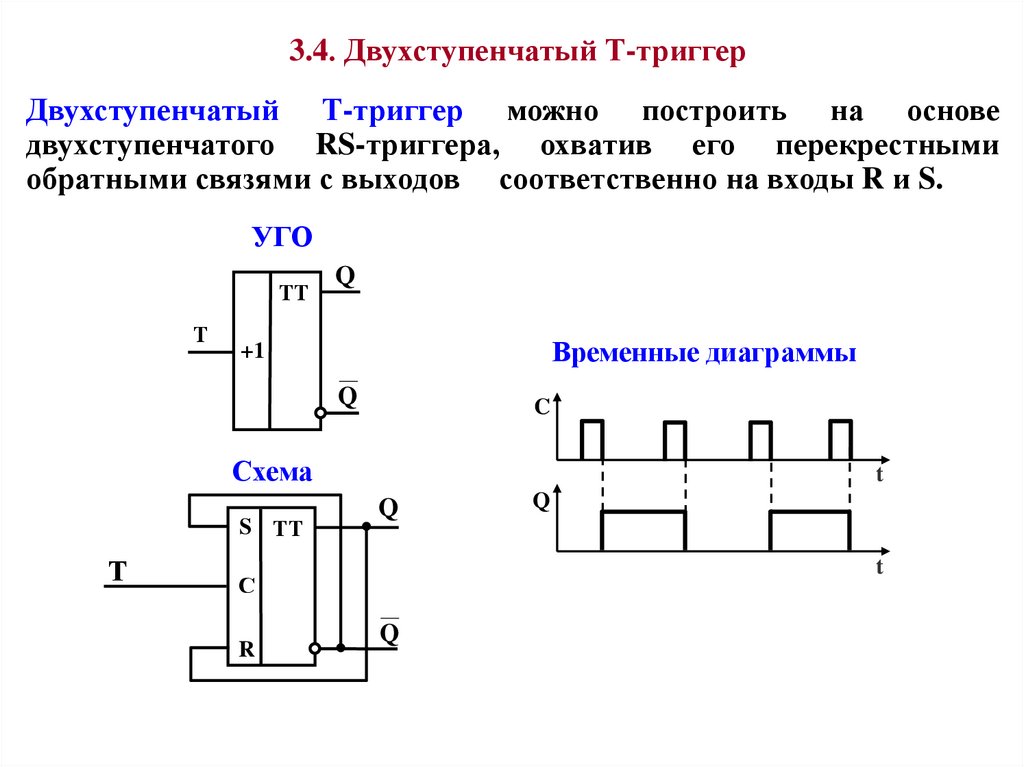

3.4. Двухступенчатый Т-триггерДвухступенчатый Т-триггер можно построить на основе

двухступенчатого RS-триггера, охватив его перекрестными

обратными связями с выходов соответственно на входы R и S.

УГО

ТТ

Т

Q

Временные диаграммы

+1

Q

C

Схема

S ТТ

Т

t

Q

t

С

R

Q

Q

33.

Применение двухступенчатых D-триггеров дляпостроения сдвигающего регистра

D

C

D

C

D

Q0

C

D TT

RG

Q2

C

D ТT

Q1

Q2

C

D TT

C

Q2

34.

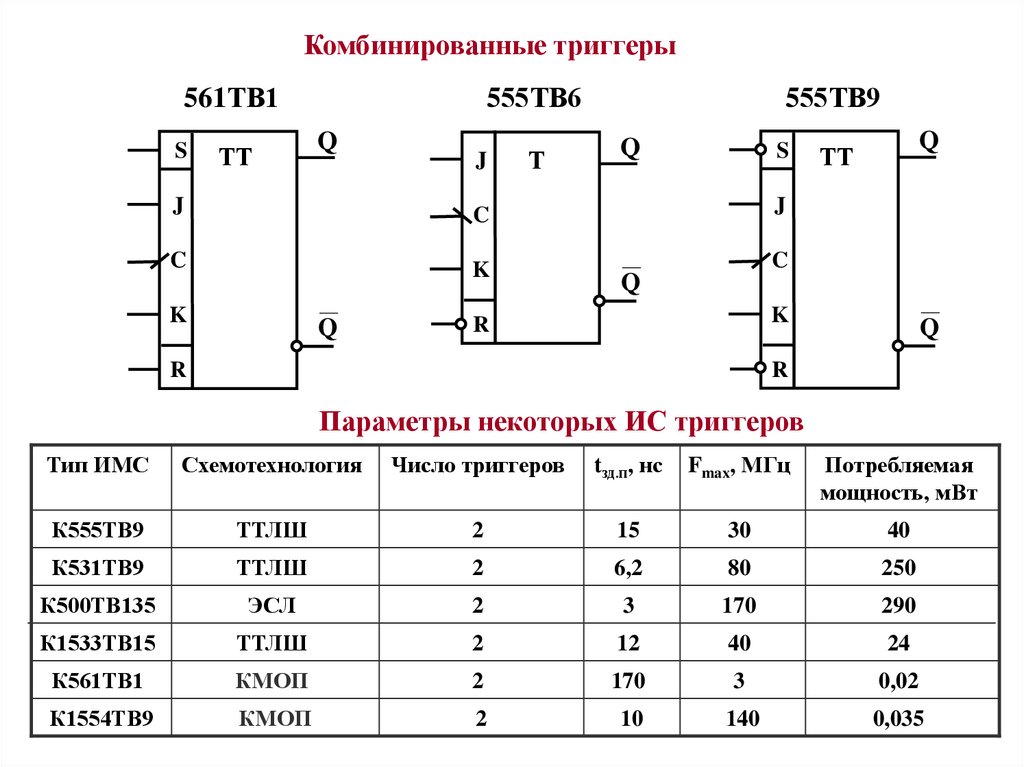

Комбинированные триггеры555ТВ6

561ТВ1

S

ТТ

Q

J

Т

555ТВ9

Q

S

J

C

J

C

K

C

K

Q

Q

ТТ

Q

K

R

Q

R

R

Параметры некоторых ИС триггеров

Тип ИМС

Схемотехнология

Число триггеров

tзд.п, нс

Fmax, МГц

Потребляемая

мощность, мВт

К555ТВ9

ТТЛШ

2

15

30

40

К531ТВ9

ТТЛШ

2

6,2

80

250

К500ТВ135

ЭСЛ

2

3

170

290

К1533ТВ15

ТТЛШ

2

12

40

24

К561ТВ1

КМОП

2

170

3

0,02

К1554ТВ9

КМОП

2

10

140

0,035

35.

Нессиметричные триггеры (триггеры Шмитта) имеют один вх. и 1 или 2выхода. Смена состояний осуществляется в зависимости от уровня Uвх.

Если Uвх ниже наименьшего порогового значения (Uпор1), то на вых. 1 из

логических уровней, если Uвх больше наибольшего порогового значения

(Uпор2), то – другой логический уровень.

Uвых

УГО

Передаточная характеристика

U1

U0

U0пор

U1пор

Uвх

t1

t2

t

t1

t2

t

В ЦУ триггеры Шмитта прим. в качестве пороговых устройств и

формирователей прямоугольных импульсов из сигналов произвольной формы.

36.

Отработать лекцию, используя:ЭЛ.1/о м. 3.2;

Л.1/д с.58-72;

Л.2/д с. 64-74

Основное внимание обратить на условные графические

обозначения и таблицы переходов триггеров.

Подготовиться к пр. зан. №4 «Анализ и расчет триггеров».

electronics

electronics