Similar presentations:

Многотактный процессор. Лекция 9

1.

Лекция 9. Многотактный процессор.Вопросы:

1. Тракты команд и данных многотактного процессора.

2. Многотактное устройство управления.

3. Дополнительные команды addi и j.

Литература: Дэвид М. Харрис и Сара Л. Харрис.

Цифровая схемотехника и архитектура компьютера,

второе издание, с. 966 - 1003.

2.

Тракт команд и данных однотактного процессора3.

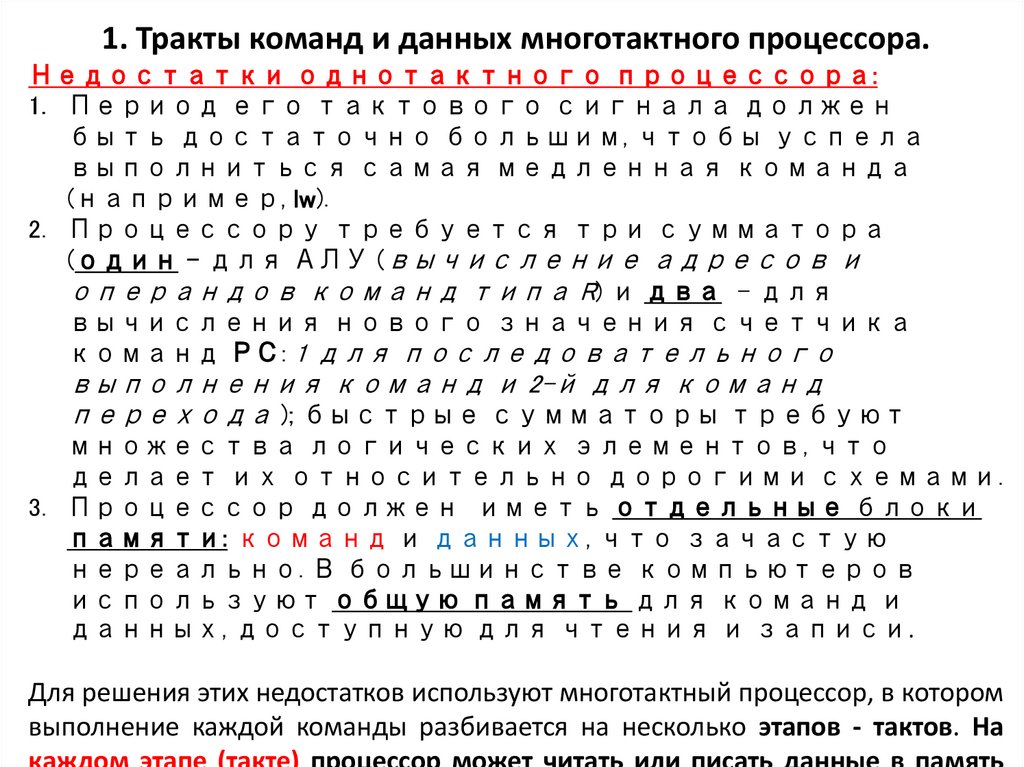

1. Тракты команд и данных многотактного процессора.Недостатки однотактного процессора:

1. Период его тактового сигнала должен

быть достаточно большим, чтобы успела

выполниться самая медленная команда

(например, lw).

2. Процессору требуется три сумматора

(один - для АЛУ (вычисление адресов и

операндов команд типа R) и два - для

вычисления нового значения счетчика

команд РС: 1 для последовательного

выполнения команд и 2-й для команд

перехода ); быстрые сумматоры требуют

множества логических элементов, что

делает их относительно дорогими схемами.

3. Процессор должен иметь отдельные блоки

памяти: команд и данных, что зачастую

нереально. В большинстве компьютеров

используют общую память для команд и

данных, доступную для чтения и записи.

Для решения этих недостатков используют многотактный процессор, в котором

выполнение каждой команды разбивается на несколько этапов - тактов. На

4.

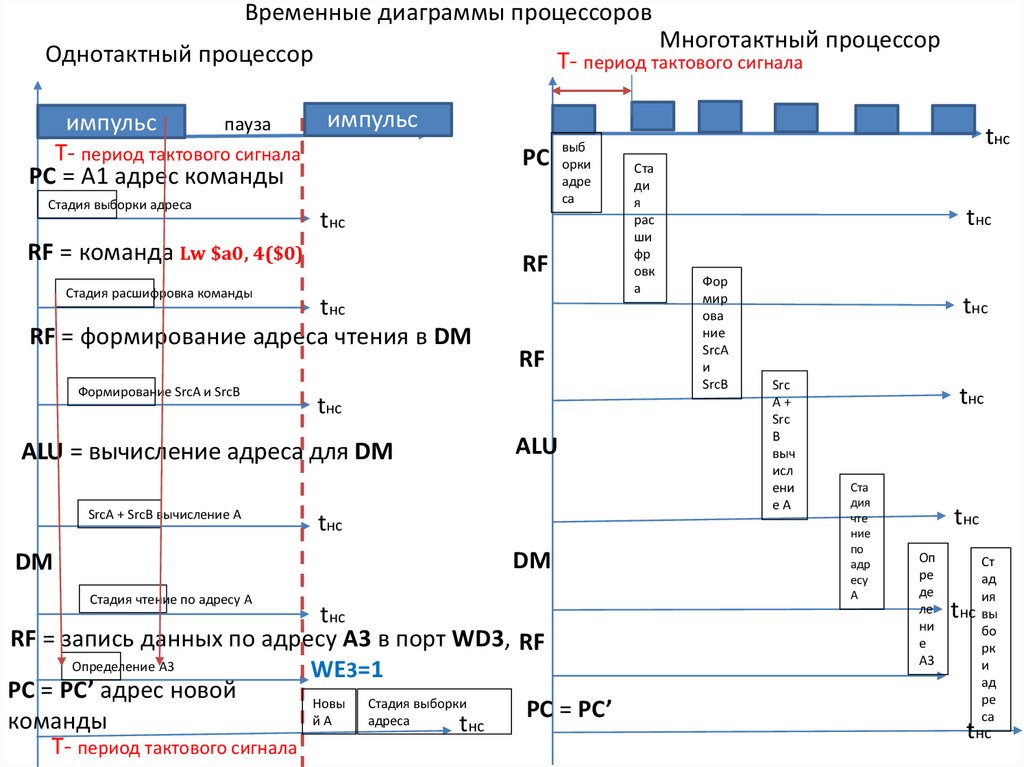

Временные диаграммы процессоровМноготактный процессор

Однотактный процессор

T- период тактового сигнала

Тактовый

импульс импульс

импульс

пауза

T- период тактового сигнала

PC

PC = A1 адрес команды

Стадия выборки адреса

Тактовый импульс

выб

орки

адре

са

tнс

RF = команда Lw $a0, 4($0)

RF

Стадия расшифровка команды

tнс

RF = формирование адреса чтения в DM

Формирование SrcA и SrcB

tнс

ALU = вычисление адреса для DM

SrcA + SrcB вычисление А

RF

ALU

tнс

DM

DM

Стадия чтение по адресу А

tнс

RF = запись данных по адресу А3 в порт WD3, RF

Определение А3

WE3=1

PC = PC’ адрес новой

Новы

Стадия выборки

PC = PC’

йА

адреса

команды

tнс

T- период тактового сигнала

Ста

ди

я

рас

ши

фр

овк

а

tнс

tнс

Фор

мир

ова

ние

SrcA

и

SrcB

tнс

Src

A+

Src

B

выч

исл

ени

еА

tнс

Ста

дия

чте

ние

по

адр

есу

А

tнс

Оп

ре

де

ле

ни

е

А3

tнс

Ст

ад

ия

вы

бо

рк

и

ад

ре

са

tнс

5.

1.1 Основные принципы конструирования многотактногопроцессора.

1. Конструкция тракта данных выполнена на основе соединения

блоков памяти и блоков, хранящие архитектурное состояние

процессора

при

помощи

комбинационной

логики,

определяющей какие блоки и когда использовать на основании

их адресного разделения .

2. Использование других блоков для хранения информации о

промежуточном (не архитектурном) состоянии между

этапами.

3. Определение устройства управления, которое должно

формировать разные управляющие сигналы в зависимости от

текущего этапа выполнения команды на основе конечного

автомата.

4. Добавление новых команд, по необходимости.

6.

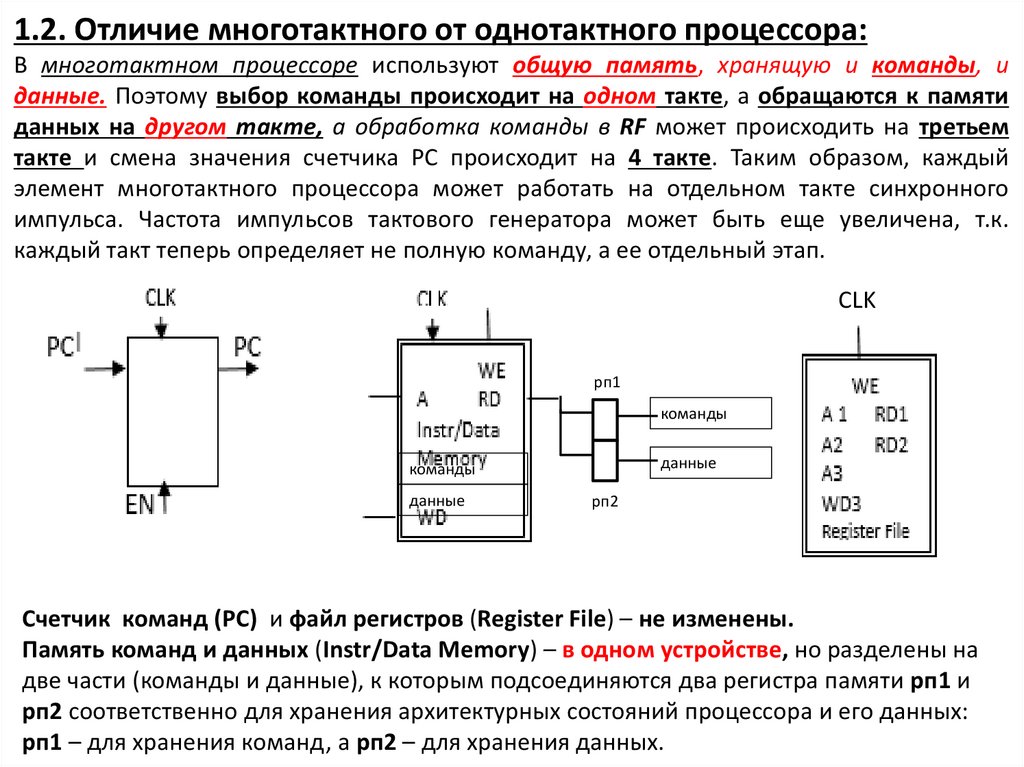

1.2. Отличие многотактного от однотактного процессора:В многотактном процессоре используют общую память, хранящую и команды, и

данные. Поэтому выбор команды происходит на одном такте, а обращаются к памяти

данных на другом такте, а обработка команды в RF может происходить на третьем

такте и смена значения счетчика РС происходит на 4 такте. Таким образом, каждый

элемент многотактного процессора может работать на отдельном такте синхронного

импульса. Частота импульсов тактового генератора может быть еще увеличена, т.к.

каждый такт теперь определяет не полную команду, а ее отдельный этап.

CLK

рп1

команды

данные

команды

данные

рп2

Счетчик команд (РС) и файл регистров (Register File) – не изменены.

Память команд и данных (Instr/Data Memory) – в одном устройстве, но разделены на

две части (команды и данные), к которым подсоединяются два регистра памяти рп1 и

рп2 соответственно для хранения архитектурных состояний процессора и его данных:

рп1 – для хранения команд, а рп2 – для хранения данных.

7.

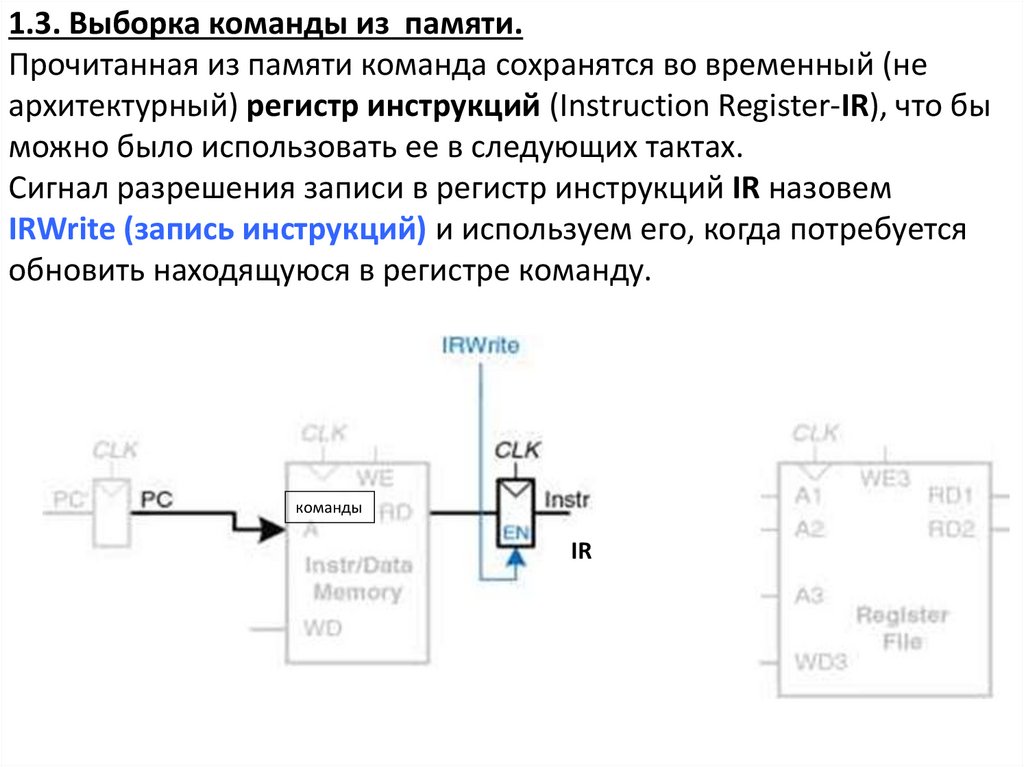

1.3. Выборка команды из памяти.Прочитанная из памяти команда сохранятся во временный (не

архитектурный) регистр инструкций (Instruction Register-IR), что бы

можно было использовать ее в следующих тактах.

Сигнал разрешения записи в регистр инструкций IR назовем

IRWrite (запись инструкций) и используем его, когда потребуется

обновить находящуюся в регистре команду.

команды

IR

8.

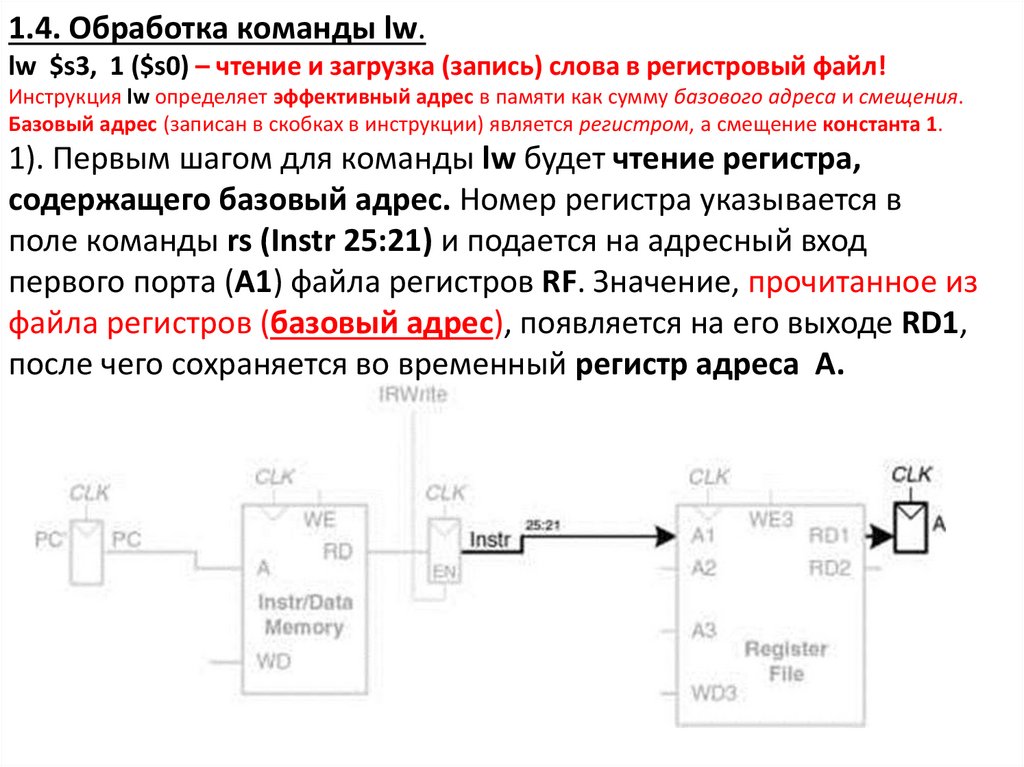

1.4. Обработка команды lw.lw $s3, 1 ($s0) – чтение и загрузка (запись) слова в регистровый файл!

Инструкция lw определяет эффективный адрес в памяти как сумму базового адреса и смещения.

Базовый адрес (записан в скобках в инструкции) является регистром, а смещение константа 1.

1). Первым шагом для команды lw будет чтение регистра,

содержащего базовый адрес. Номер регистра указывается в

поле команды rs (Instr 25:21) и подается на адресный вход

первого порта (А1) файла регистров RF. Значение, прочитанное из

файла регистров (базовый адрес), появляется на его выходе RD1,

после чего сохраняется во временный регистр адреса А.

9.

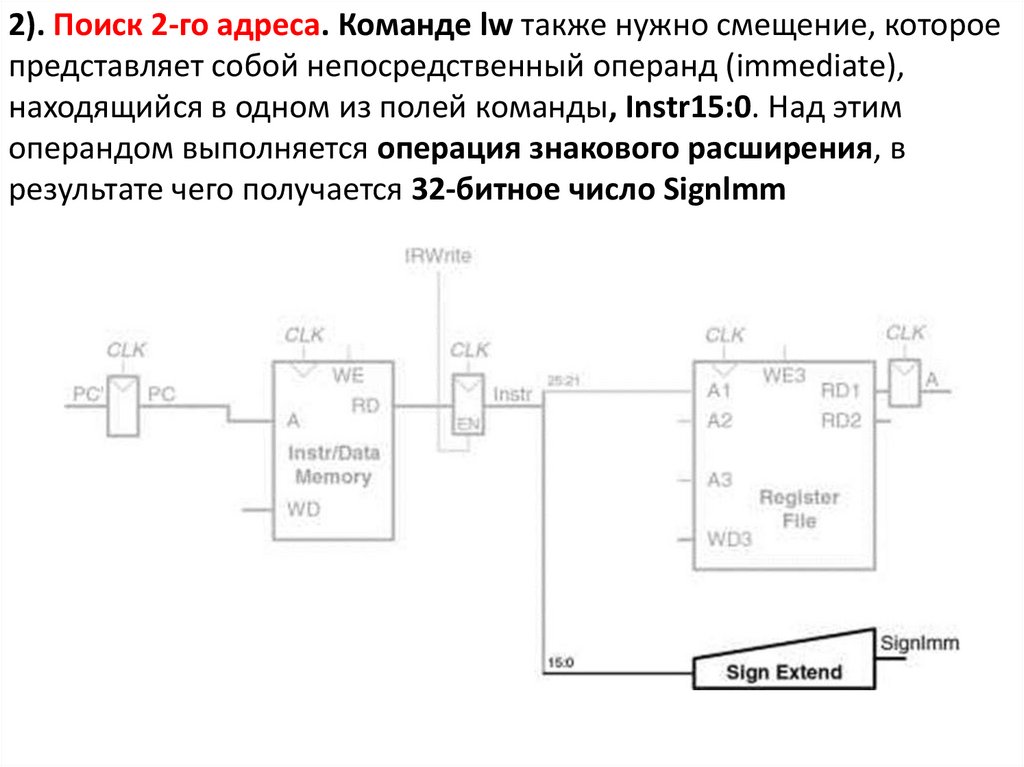

2). Поиск 2-го адреса. Команде lw также нужно смещение, котороепредставляет собой непосредственный операнд (immediate),

находящийся в одном из полей команды, Instr15:0. Над этим

операндом выполняется операция знакового расширения, в

результате чего получается 32-битное число Signlmm

10.

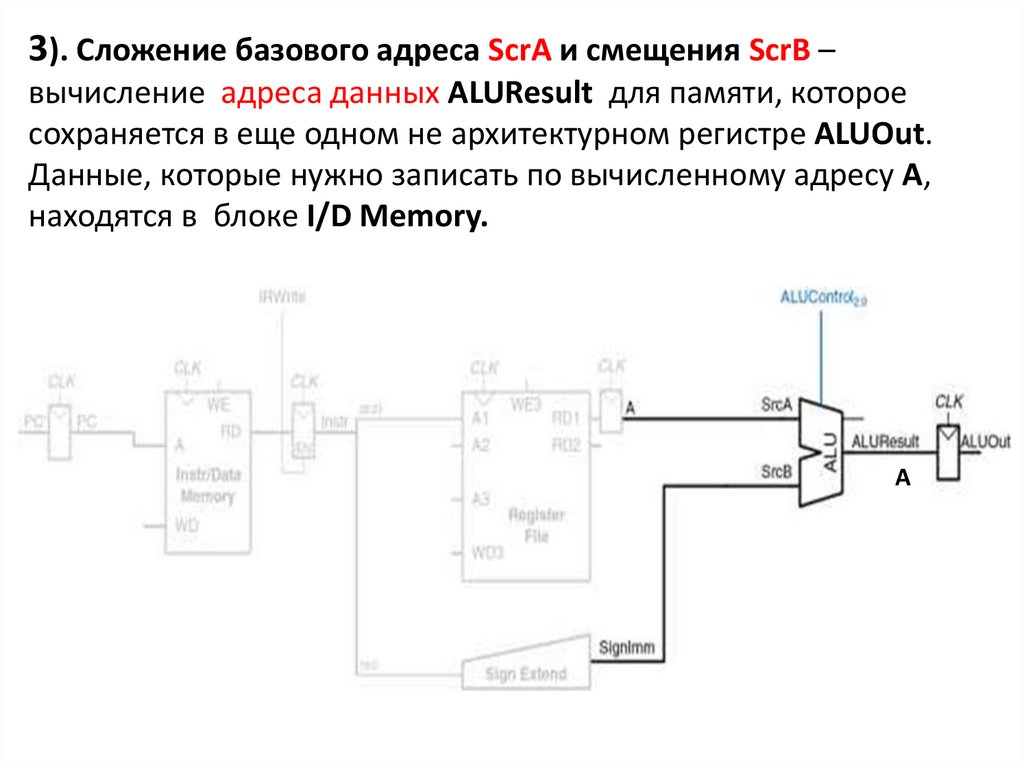

3). Сложение базового адреса ScrA и смещения ScrB –вычисление адреса данных ALUResult для памяти, которое

сохраняется в еще одном не архитектурном регистре ALUOut.

Данные, которые нужно записать по вычисленному адресу А,

находятся в блоке I/D Memory.

А

11.

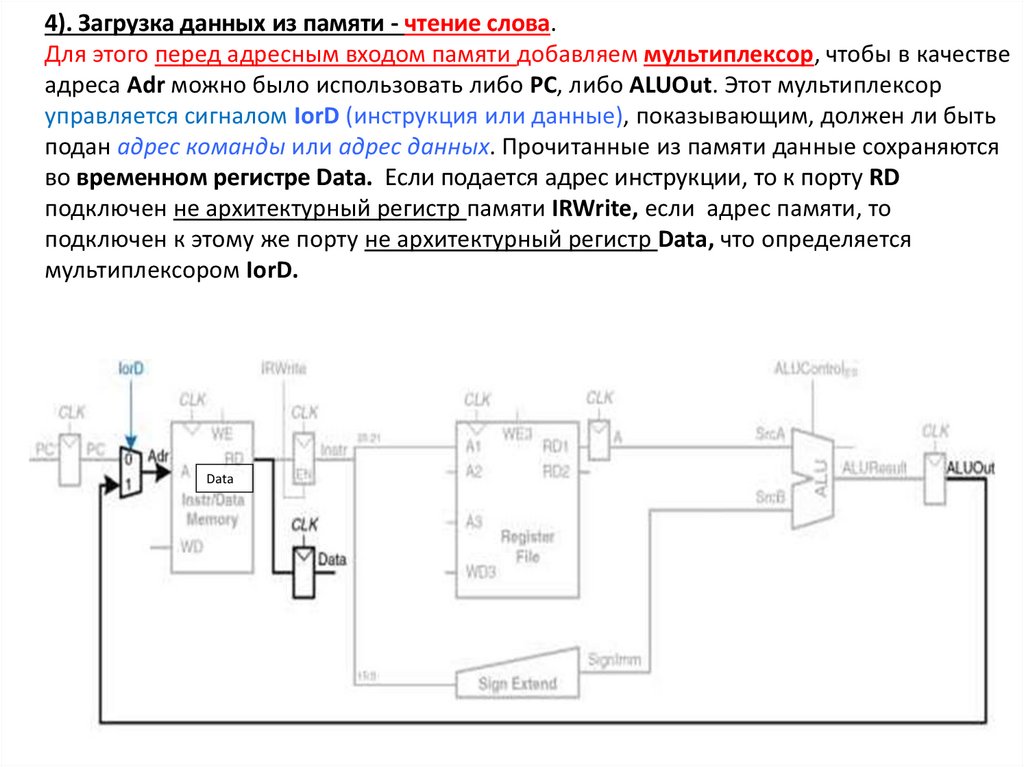

4). Загрузка данных из памяти - чтение слова.Для этого перед адресным входом памяти добавляем мультиплексор, чтобы в качестве

адреса Adr можно было использовать либо PC, либо ALUOut. Этот мультиплексор

управляется сигналом IorD (инструкция или данные), показывающим, должен ли быть

подан адрес команды или адрес данных. Прочитанные из памяти данные сохраняются

во временном регистре Data. Если подается адрес инструкции, то к порту RD

подключен не архитектурный регистр памяти IRWrite, если адрес памяти, то

подключен к этому же порту не архитектурный регистр Data, что определяется

мультиплексором IorD.

Data

12.

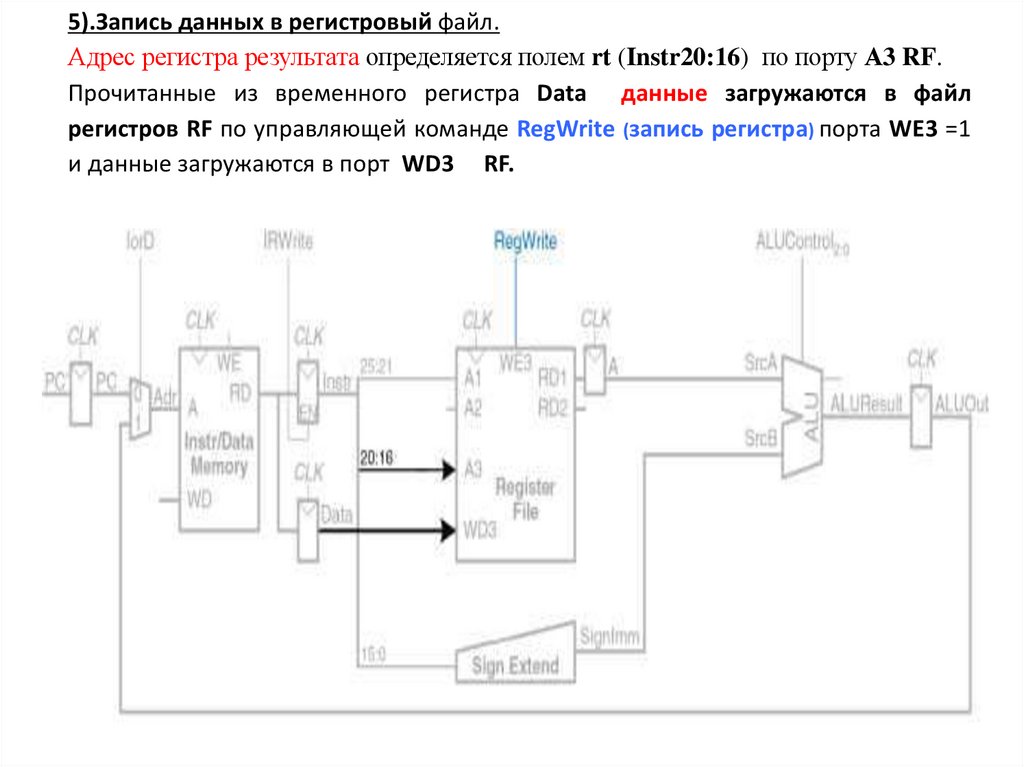

5).Запись данных в регистровый файл.Адрес регистра результата определяется полем rt (Instr20:16) по порту А3 RF.

Прочитанные из временного регистра Data данные загружаются в файл

регистров RF по управляющей команде RegWrite (запись регистра) порта WE3 =1

и данные загружаются в порт WD3 RF.

13.

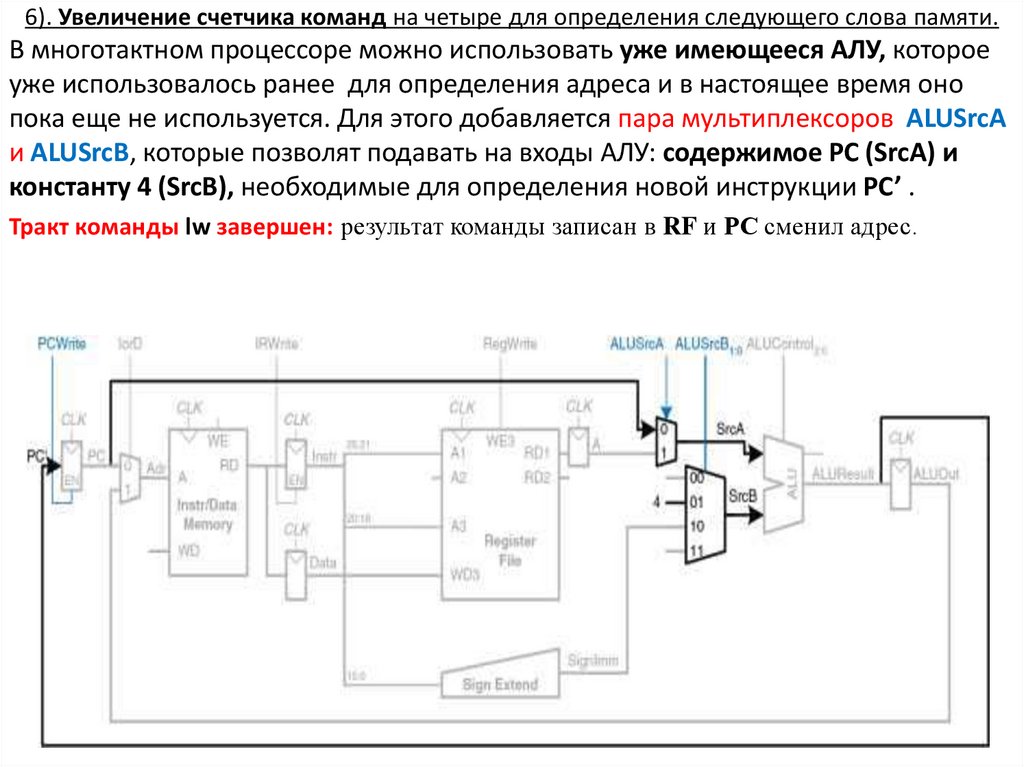

6). Увеличение счетчика команд на четыре для определения следующего слова памяти.В многотактном процессоре можно использовать уже имеющееся АЛУ, которое

уже использовалось ранее для определения адреса и в настоящее время оно

пока еще не используется. Для этого добавляется пара мультиплексоров ALUSrcA

и ALUSrcB, которые позволят подавать на входы АЛУ: содержимое РС (SrcA) и

константу 4 (SrcB), необходимые для определения новой инструкции PC’ .

Тракт команды lw завершен: результат команды записан в RF и РС сменил адрес.

14.

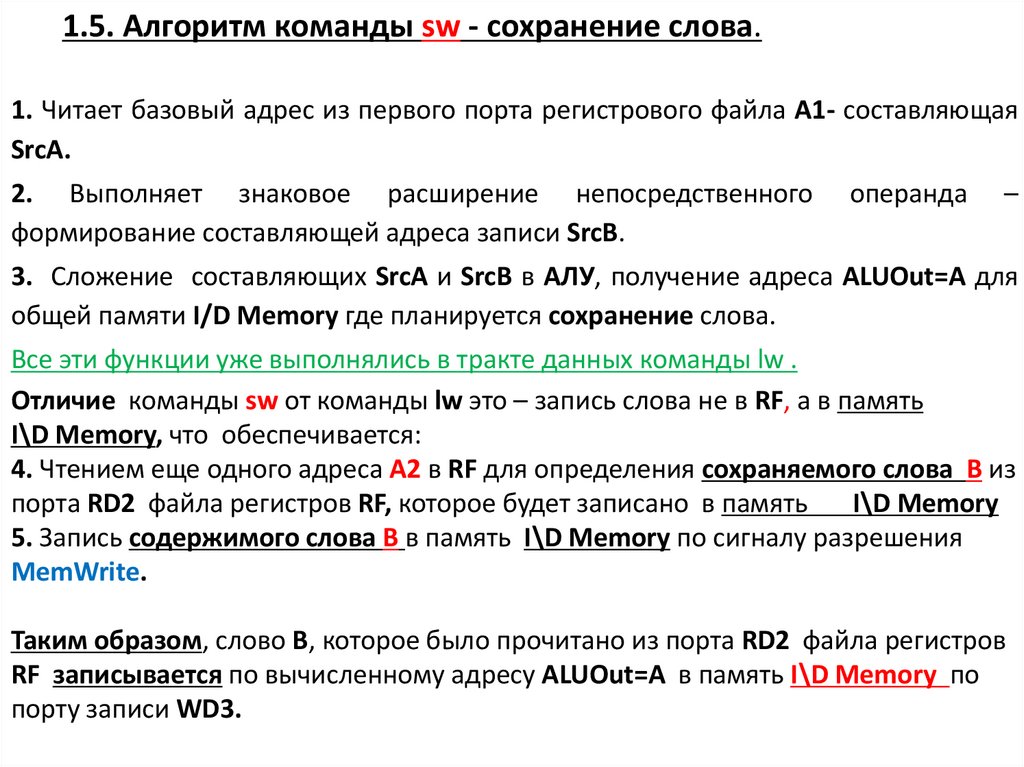

1.5. Алгоритм команды sw - сохранение слова.1. Читает базовый адрес из первого порта регистрового файла А1- составляющая

SrcA.

2. Выполняет знаковое расширение непосредственного

формирование составляющей адреса записи SrcB.

операнда

–

3. Сложение составляющих SrcA и SrcВ в АЛУ, получение адреса ALUOut=А для

общей памяти I/D Memory где планируется сохранение слова.

Все эти функции уже выполнялись в тракте данных команды lw .

Отличие команды sw от команды lw это – запись слова не в RF, а в память

I\D Memory, что обеспечивается:

4. Чтением еще одного адреса А2 в RF для определения сохраняемого слова В из

порта RD2 файла регистров RF, которое будет записано в память

I\D Memory

5. Запись содержимого слова В в память I\D Memory по сигналу разрешения

MemWrite.

Таким образом, слово В, которое было прочитано из порта RD2 файла регистров

RF записывается по вычисленному адресу ALUOut=А в память I\D Memory по

порту записи WD3.

15.

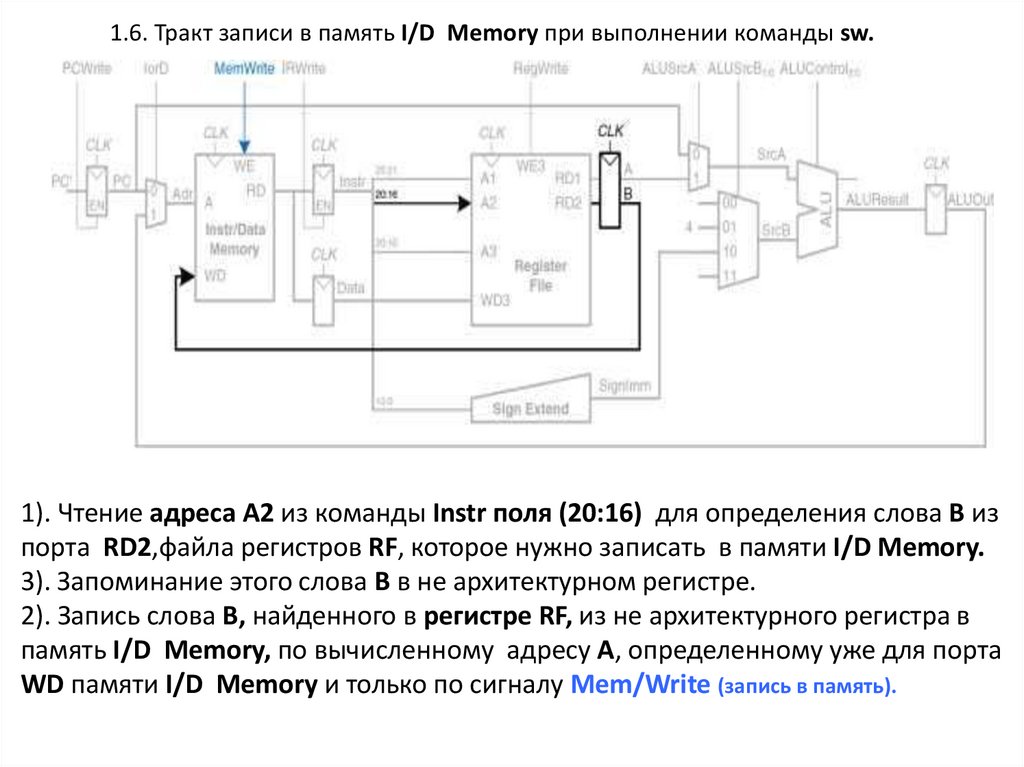

1.6. Тракт записи в память I/D Memory при выполнении команды sw.1). Чтение адреса А2 из команды Instr поля (20:16) для определения слова В из

порта RD2,файла регистров RF, которое нужно записать в памяти I/D Memory.

3). Запоминание этого слова В в не архитектурном регистре.

2). Запись слова В, найденного в регистре RF, из не архитектурного регистра в

память I/D Memory, по вычисленному адресу А, определенному уже для порта

WD памяти I/D Memory и только по сигналу Mem/Write (запись в память).

16.

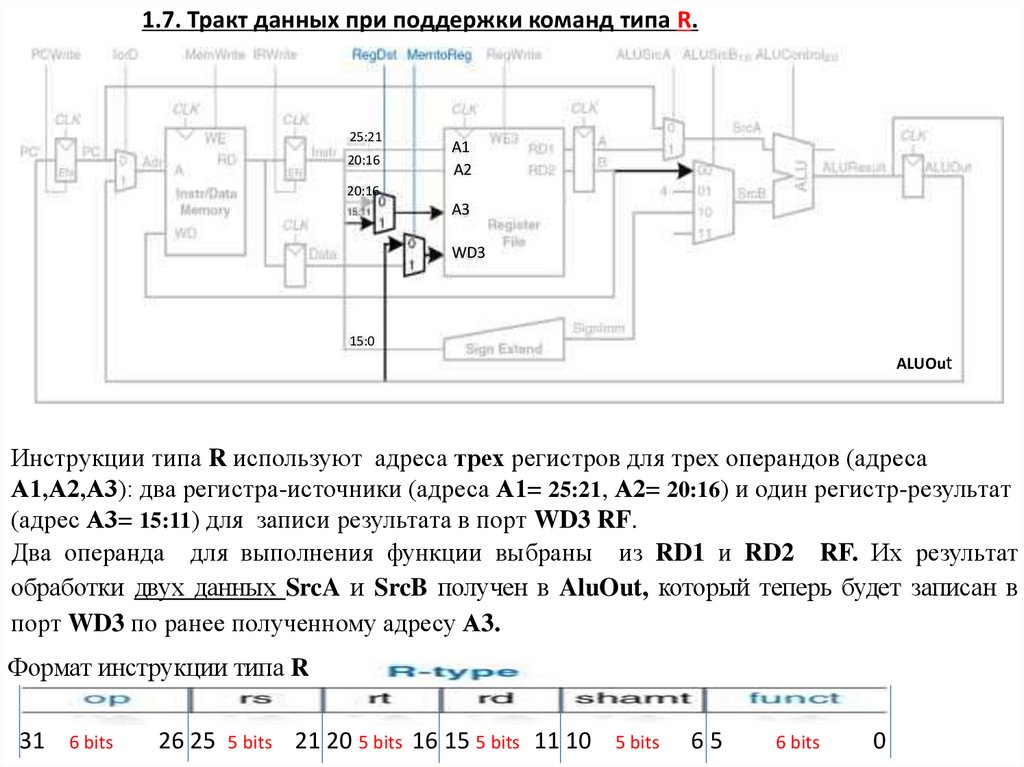

1.7. Тракт данных при поддержки команд типа R.25:21

20:16

A1

A2

20:16

A3

WD3

15:0

ALUOut

Инструкции типа R используют адреса трех регистров для трех операндов (адреса

А1,А2,А3): два регистра-источники (адреса А1= 25:21, А2= 20:16) и один регистр-результат

(адрес А3= 15:11) для записи результата в порт WD3 RF.

Два операнда для выполнения функции выбраны из RD1 и RD2 RF. Их результат

обработки двух данных SrcA и SrcB получен в AluOut, который теперь будет записан в

порт WD3 по ранее полученному адресу А3.

Формат инструкции типа R

31

6 bits

26 25

5 bits

21 20 5 bits 16 15 5 bits 11 10

5 bits

65

6 bits

0

17.

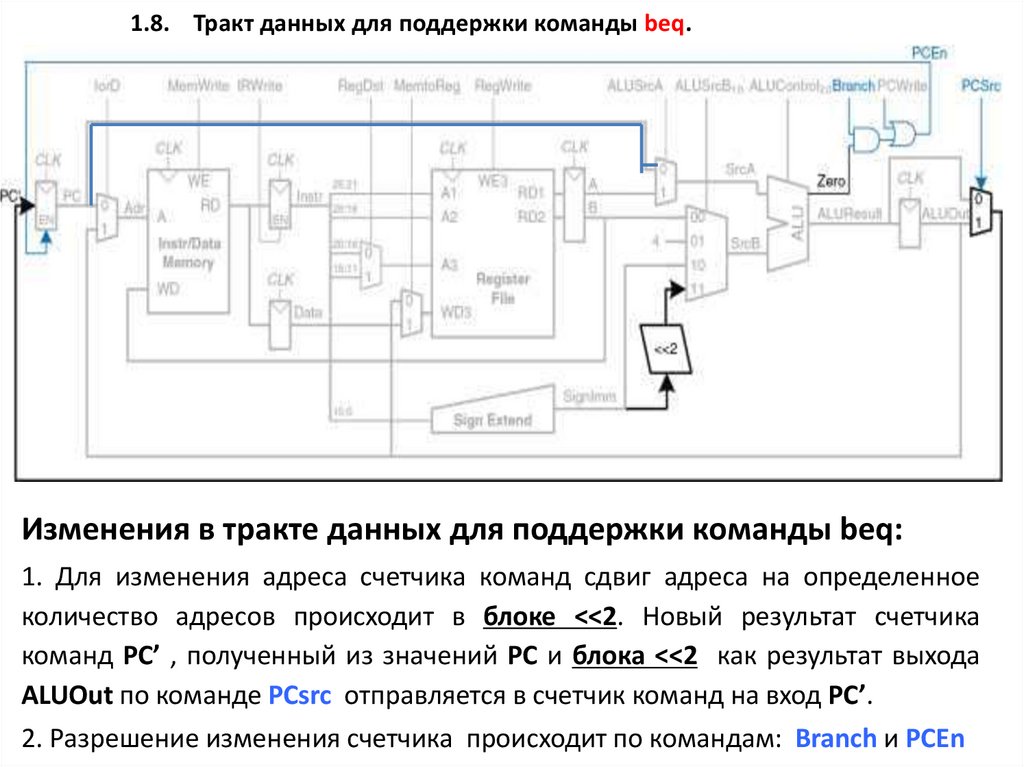

1.8. Тракт данных для поддержки команды beq.Изменения в тракте данных для поддержки команды beq:

1. Для изменения адреса счетчика команд сдвиг адреса на определенное

количество адресов происходит в блоке <<2. Новый результат счетчика

команд РС’ , полученный из значений РC и блока <<2 как результат выхода

ALUOut по команде PCsrc отправляется в счетчик команд на вход PC’.

2. Разрешение изменения счетчика происходит по командам: Branch и РСEn

18.

Схема многотактного процессора MIPS.19.

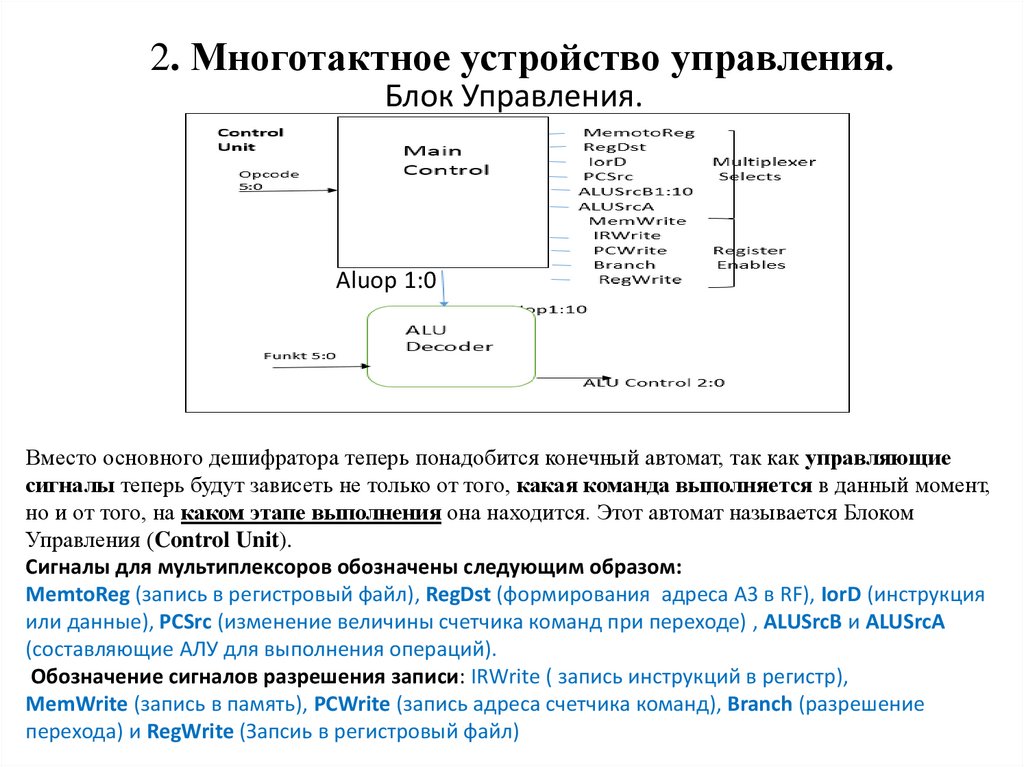

2. Многотактное устройство управления.Блок Управления.

Aluop 1:0

Вместо основного дешифратора теперь понадобится конечный автомат, так как управляющие

сигналы теперь будут зависеть не только от того, какая команда выполняется в данный момент,

но и от того, на каком этапе выполнения она находится. Этот автомат называется Блоком

Управления (Control Unit).

Сигналы для мультиплексоров обозначены следующим образом:

MemtoReg (запись в регистровый файл), RegDst (формирования адреса А3 в RF), IorD (инструкция

или данные), PCSrc (изменение величины счетчика команд при переходе) , ALUSrcB и ALUSrcA

(составляющие АЛУ для выполнения операций).

Обозначение сигналов разрешения записи: IRWrite ( запись инструкций в регистр),

MemWrite (запись в память), PCWrite (запись адреса счетчика команд), Branch (разрешение

перехода) и RegWrite (Запсиь в регистровый файл)

20.

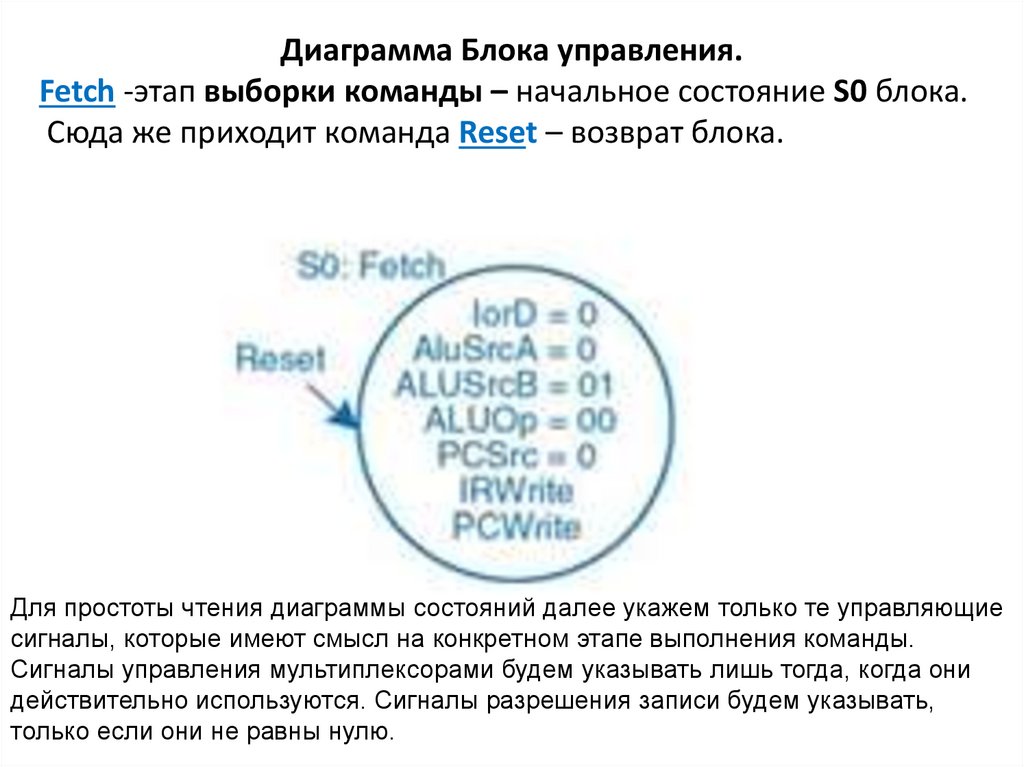

Диаграмма Блока управления.Fetch -этап выборки команды – начальное состояние S0 блока.

Сюда же приходит команда Reset – возврат блока.

Для простоты чтения диаграммы состояний далее укажем только те управляющие

сигналы, которые имеют смысл на конкретном этапе выполнения команды.

Сигналы управления мультиплексорами будем указывать лишь тогда, когда они

действительно используются. Сигналы разрешения записи будем указывать,

только если они не равны нулю.

21.

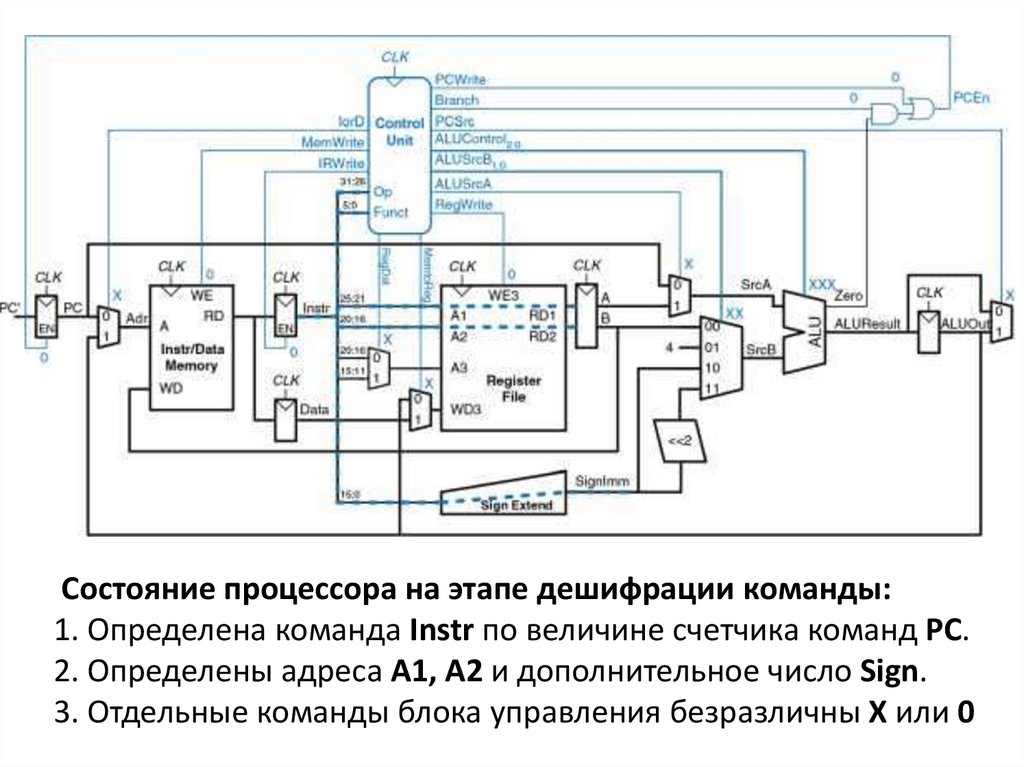

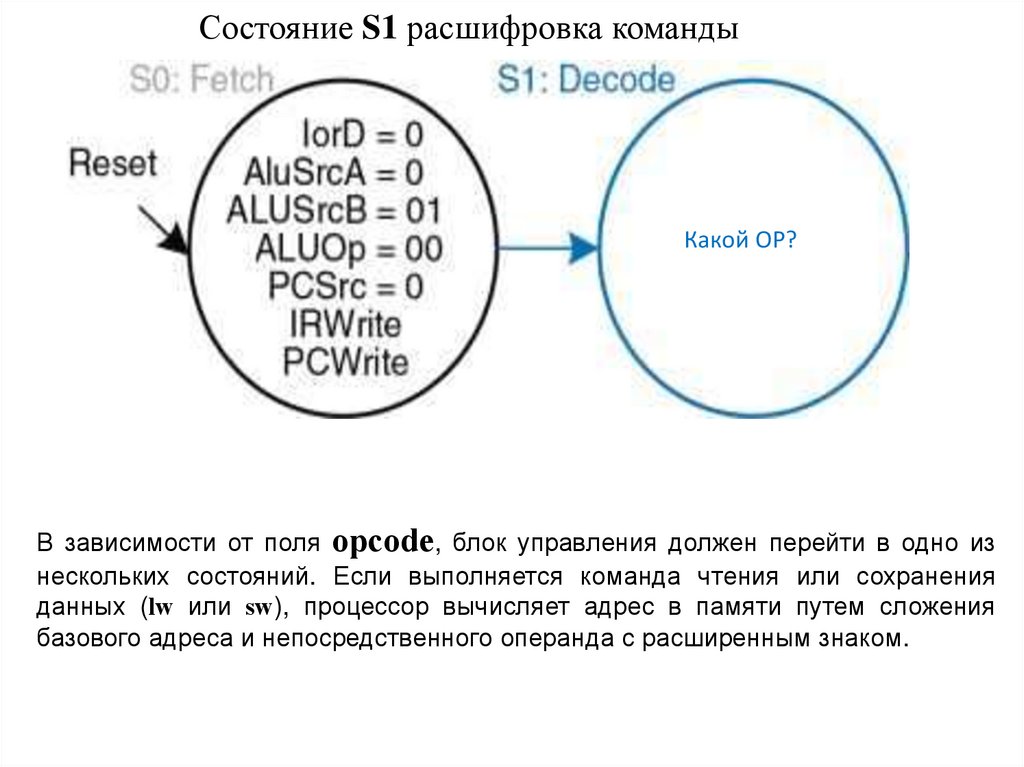

Состояние процессора на этапе дешифрации команды:1. Определена команда Instr по величине счетчика команд РС.

2. Определены адреса А1, А2 и дополнительное число Sign.

3. Отдельные команды блока управления безразличны Х или 0

22.

Состояние S1 расшифровка командыКакой OP?

В зависимости от поля opcode, блок управления должен перейти в одно из

нескольких состояний. Если выполняется команда чтения или сохранения

данных (lw или sw), процессор вычисляет адрес в памяти путем сложения

базового адреса и непосредственного операнда с расширенным знаком.

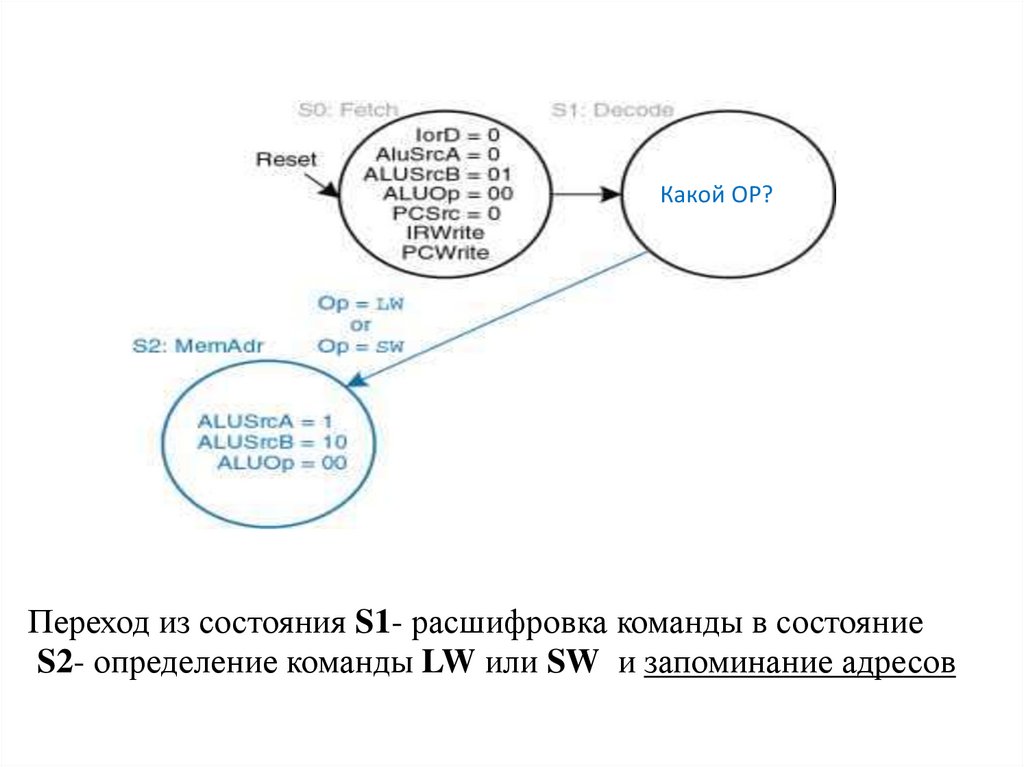

23.

Какой OP?Переход из состояния S1- расшифровка команды в состояние

S2- определение команды LW или SW и запоминание адресов

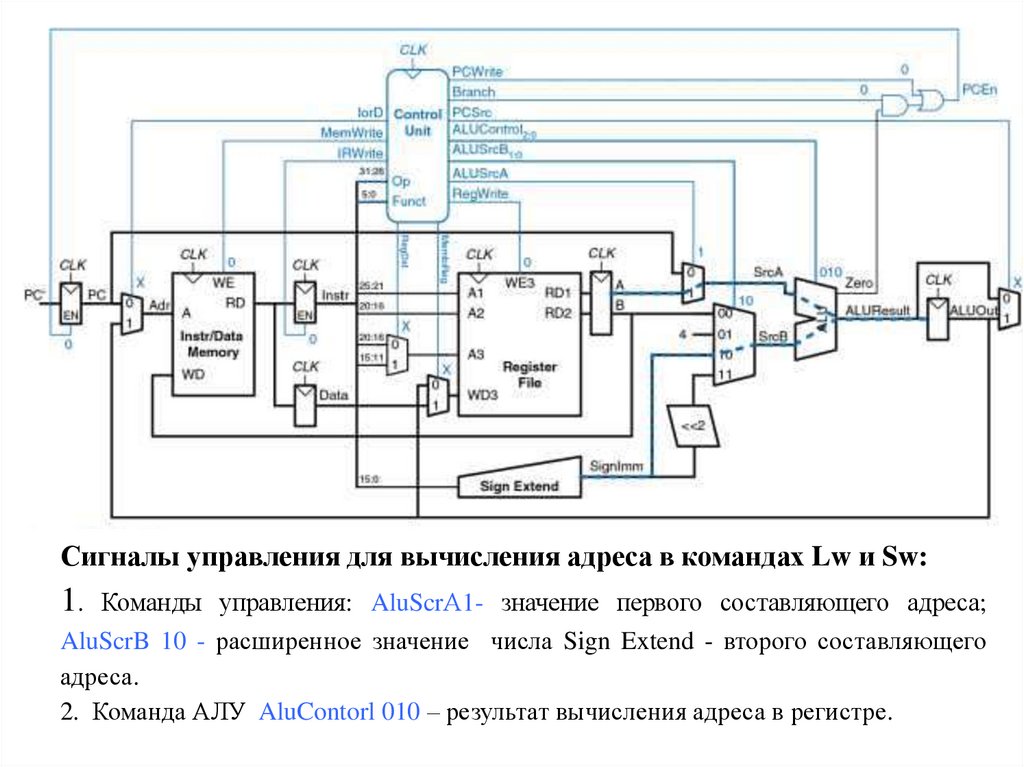

24.

Сигналы управления для вычисления адреса в командах Lw и Sw:1.

Команды управления: AluScrА1- значение первого составляющего адреса;

AluScrB 10 - расширенное значение числа Sign Extend - второго составляющего

адреса.

2. Команда АЛУ AluContorl 010 – результат вычисления адреса в регистре.

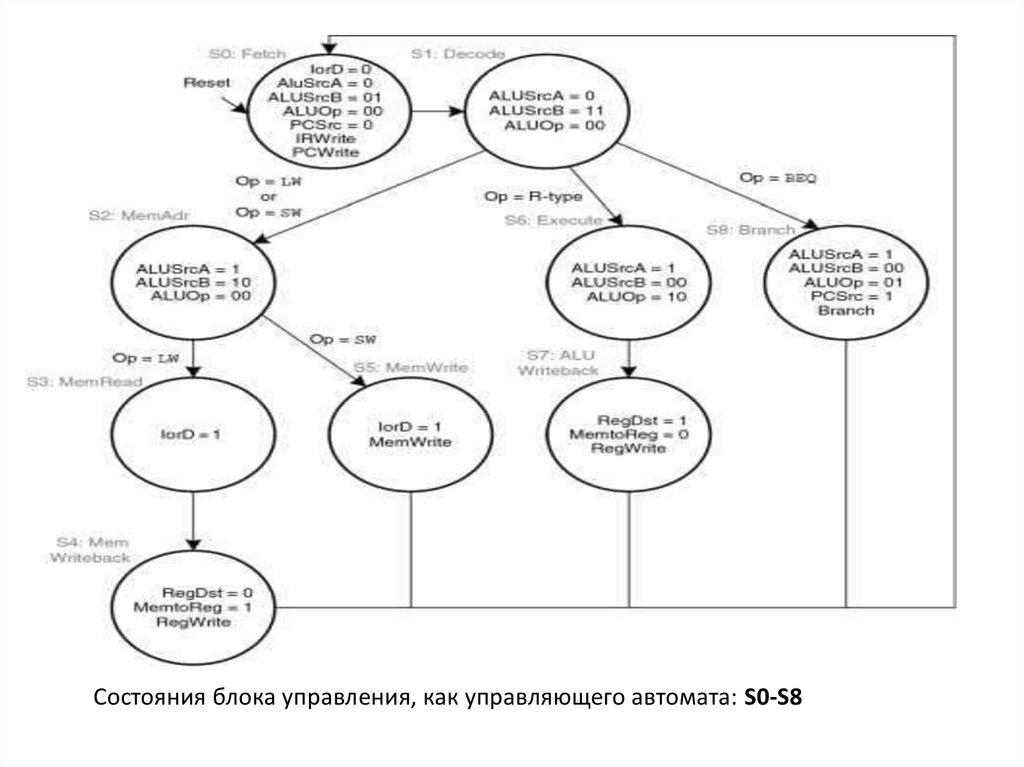

25.

Op=?Этап исполнения команды состояние S3:

Ор =Lw – чтение слова ,управление - IorD=1.

Этап запоминание команды в регистровом

файле (RF) состояние S4:

сигнал управления – RegDst =0;

сигнал разрешения записи в (RF) -MtmtoReg=1.

Этап возврата в начальное состояние - состояние S0

26.

Состояния блока управления, как управляющего автомата: S0-S827.

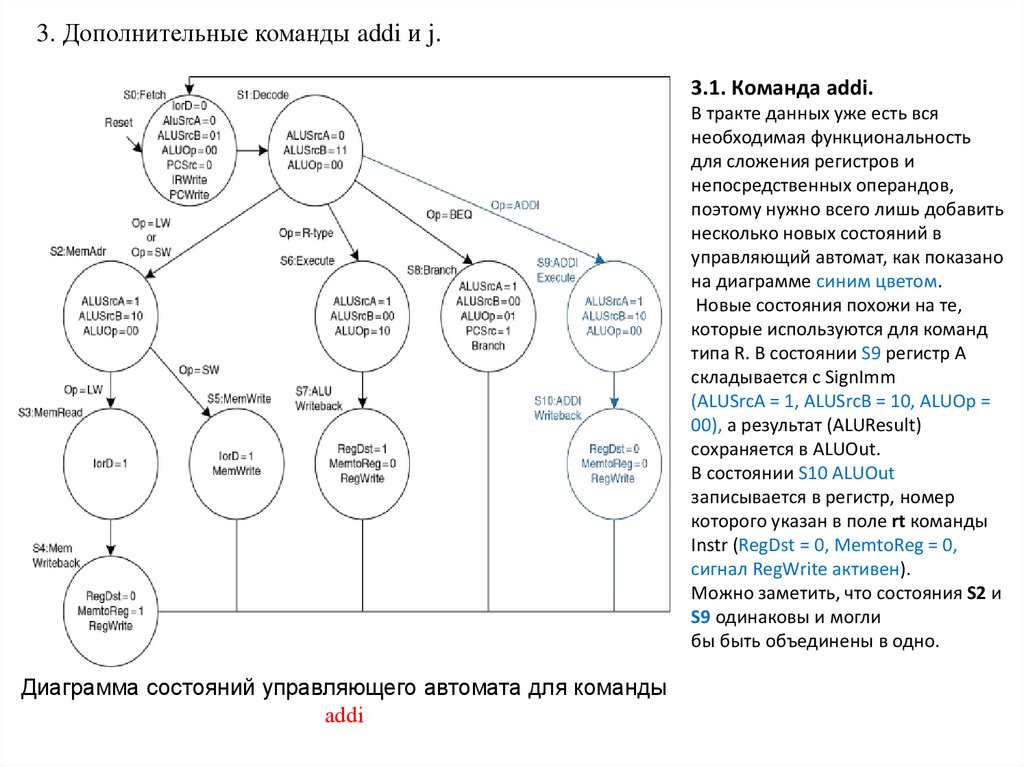

3. Дополнительные команды addi и j.3.1. Команда addi.

В тракте данных уже есть вся

необходимая функциональность

для сложения регистров и

непосредственных операндов,

поэтому нужно всего лишь добавить

несколько новых состояний в

управляющий автомат, как показано

на диаграмме синим цветом.

Новые состояния похожи на те,

которые используются для команд

типа R. В состоянии S9 регистр A

складывается с SignImm

(ALUSrcA = 1, ALUSrcB = 10, ALUOp =

00), а результат (ALUResult)

сохраняется в ALUOut.

В состоянии S10 ALUOut

записывается в регистр, номер

которого указан в поле rt команды

Instr (RegDst = 0, MemtoReg = 0,

сигнал RegWrite активен).

Можно заметить, что состояния S2 и

S9 одинаковы и могли

бы быть объединены в одно.

Диаграмма состояний управляющего автомата для команды

addi

28.

3.2. Команда J31:28

27:0

25:0 adr

Тракт данных команды J

Для команды j необходимо добавить в тракт данных логику вычисления значения счетчика PC’

Для этого надо будет добавить еще одно новое состояние в управляющий автомат.

Адрес безусловного перехода вычисляется путем сдвига 26-битного поля addr (25:0 adr) на два разряда

влево, что обеспечивает 28 бит адреса (27:0). Оставшиеся четыре старших бита копируются из

старших битов счетчика команд PC (31:28). Получившийся адрес подается на

мультиплексор PCSrc, для чего число его входов данных нужно увеличить с двух до трех.

opcode 6b

31

25

Adr 26b

0

26

27:0

4b=PC+4

Adr 26b

2b=0

(31:28)

(27:2)=(25:0)

(1:0)

29.

Диаграмма состояний управляющего автомата для команды jВыводы по многотактному процессору:

1. Таковая частота должна быть увеличена, т.к. команды разделены на этапы.

2. За счет многократного использования отдельных элементов процессора его объем

и масса уменьшены.

3. Скорость обработки команд можно считать увеличенной за счет увеличения тактовой

частоты частоты, но за счет использования дополнительных регистров памяти скорость

обработки команд замедляется.

electronics

electronics