Similar presentations:

Основные части вычислительной системы

1. Лекция 3

Основные частивычислительной системы

Общая шина

Передача данных,

управляющих

сигналов

Управление,

обработка

информации

Хранение

информации

Монитор,

клавиатура, мышь

2. Основные части вычислительной системы

ПамятьРеле

Транзисторы

Ферритовые

сердечники

Перфокарты

Магнитные диски

Дискеты

Лазерные диски

Флеш-память

…

память

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

0

1

Одна ячейка

памяти – 1 бит

3. Память

Перфокарты и перфолентыКарточка с программой на Фортране (Fortran): Z (1) = Y + W (1)

Аппарат для чтения перфокарт.

http://nnm.uz/interesting/other/6622-interesnye-fakty-o-kompyutere-2.html

Перфолента

Аппарат для

написания кода

на перфокарте.

4. Перфокарты и перфоленты

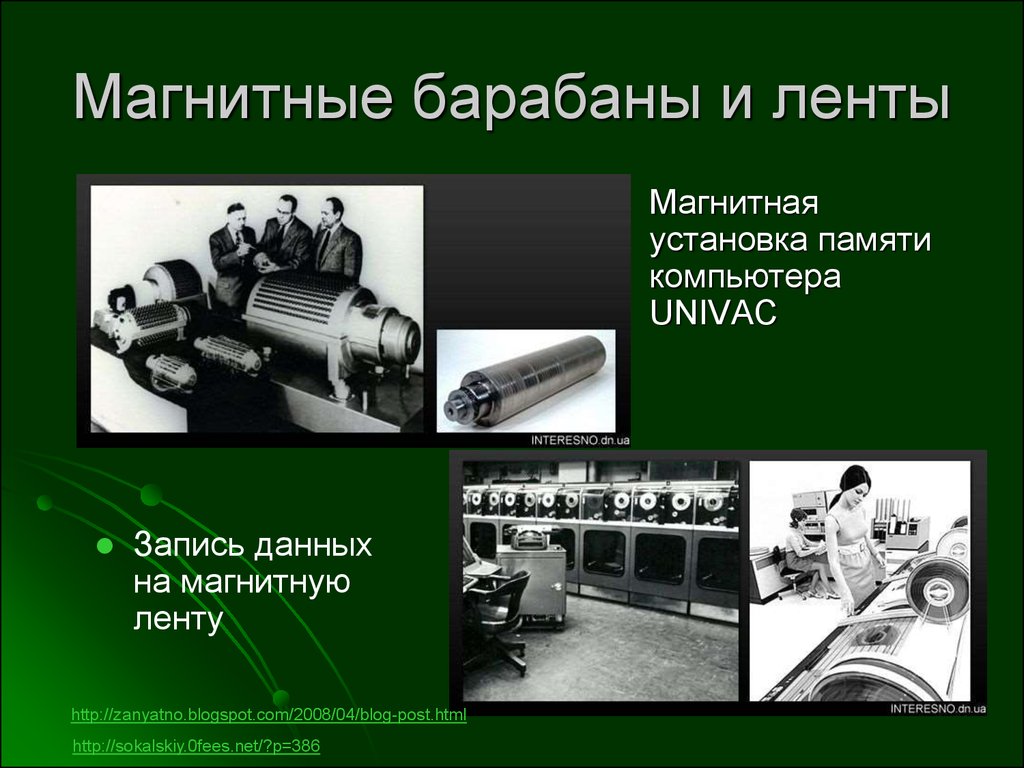

Магнитные барабаны и лентыЗапись данных

на магнитную

ленту

http://zanyatno.blogspot.com/2008/04/blog-post.html

http://sokalskiy.0fees.net/?p=386

Магнитная

установка памяти

компьютера

UNIVAC

5. Магнитные барабаны и ленты

Типы памятиПостоянное

запоминающее

устройство

ПЗУ

ППЗУ

Оперативное

запоминающее

устройство

6. Типы памяти

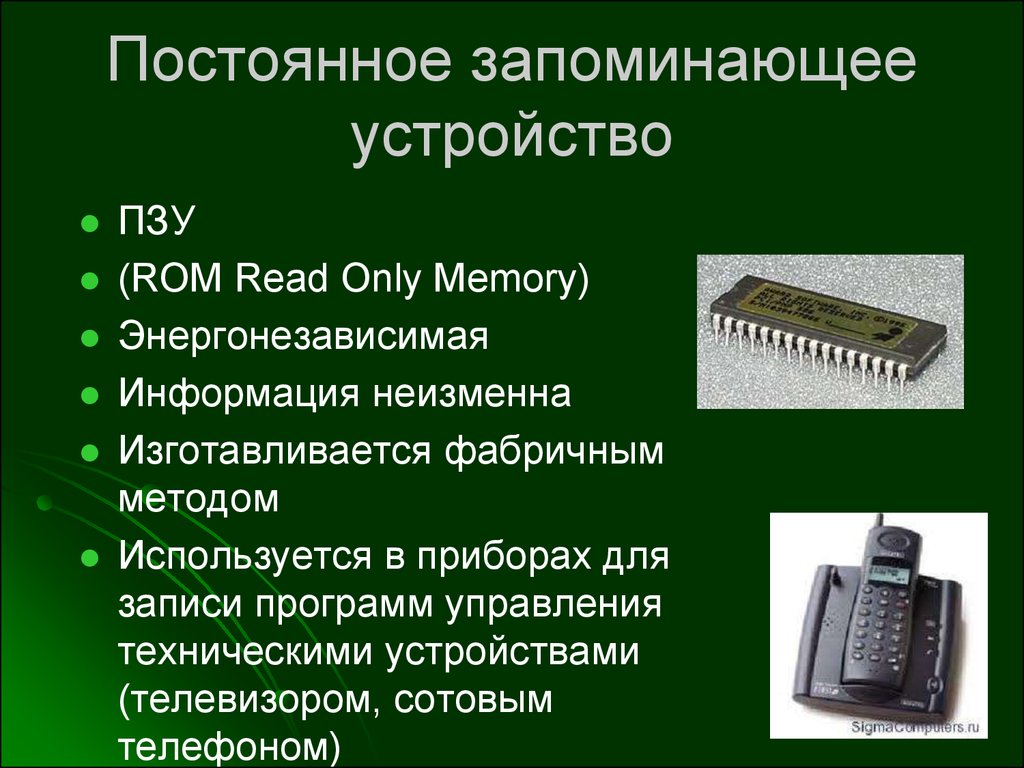

Постоянное запоминающееустройство

ПЗУ

(ROM Read Only Memory)

Энергонезависимая

Информация неизменна

Изготавливается фабричным

методом

Используется в приборах для

записи программ управления

техническими устройствами

(телевизором, сотовым

телефоном)

7. Постоянное запоминающее устройство

Перепрограммируемое ПЗУPROM (Programmable ROM)

программируемое пользователем

EPROM (erasable programmable readonly memory), перепрограммируемое

Микросхема ПЗУ AMD AM2716

Стирание ультрафиолетом

выпущенная в 1979 году

Циклов перезаписи не слишком много

EEPROM (Electrically Erasable

Programmable Read-Only Memory)

Микросхема EPROM Intel

1702 с ультрафиолетовым

стиранием.

8. Перепрограммируемое ПЗУ

Оперативное запоминающееустройство

ОЗУ

(RAM Random Access Memory)

Основной тип памяти для хранения

выполняемых программ и обрабатываемых

данных

Гарвардская

архитектура:

данные и программы хранятся отдельно

9. Оперативное запоминающее устройство

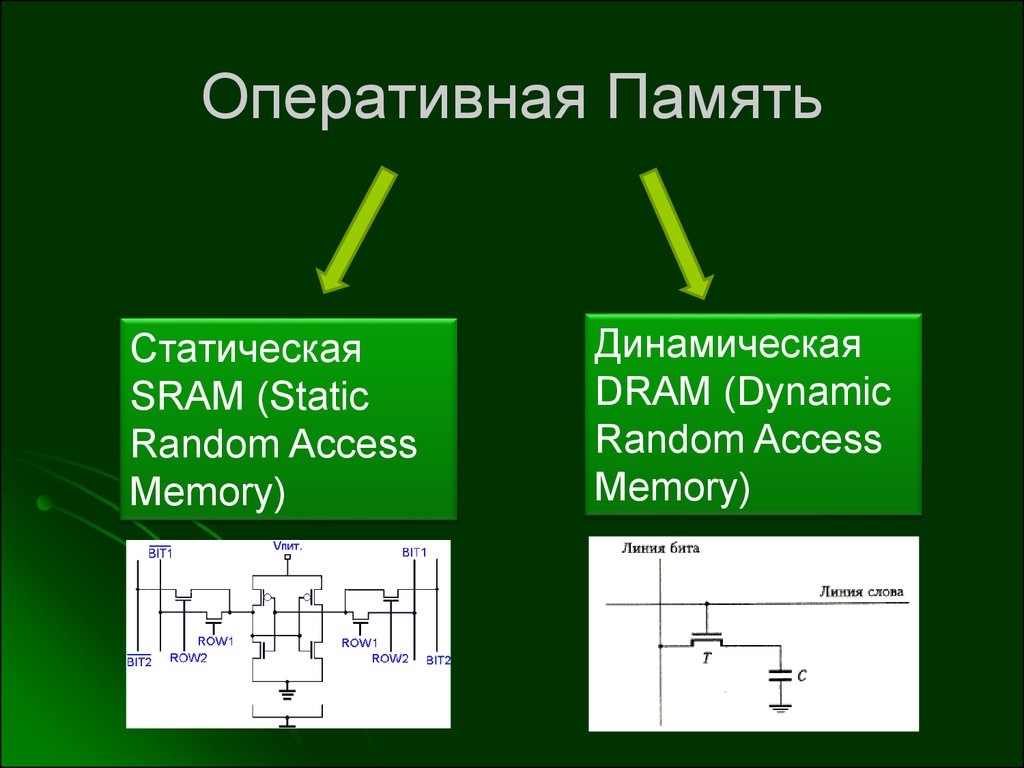

Оперативная ПамятьСтатическая

SRAM (Static

Random Access

Memory)

Динамическая

DRAM (Dynamic

Random Access

Memory)

10. Оперативная Память

Динамическая памятьЧитаемые

данные

Адресная шина:

выбор ячейки

один транзистор и

один конденсатор

Заряд сохраняется

несколько десятков

миллисекунд

При записи заряд

стирается

Регенерация

Полученные на усилителе сигнала

данные тут же записываются обратно

Замедляет работу памяти в целом

11. Динамическая память

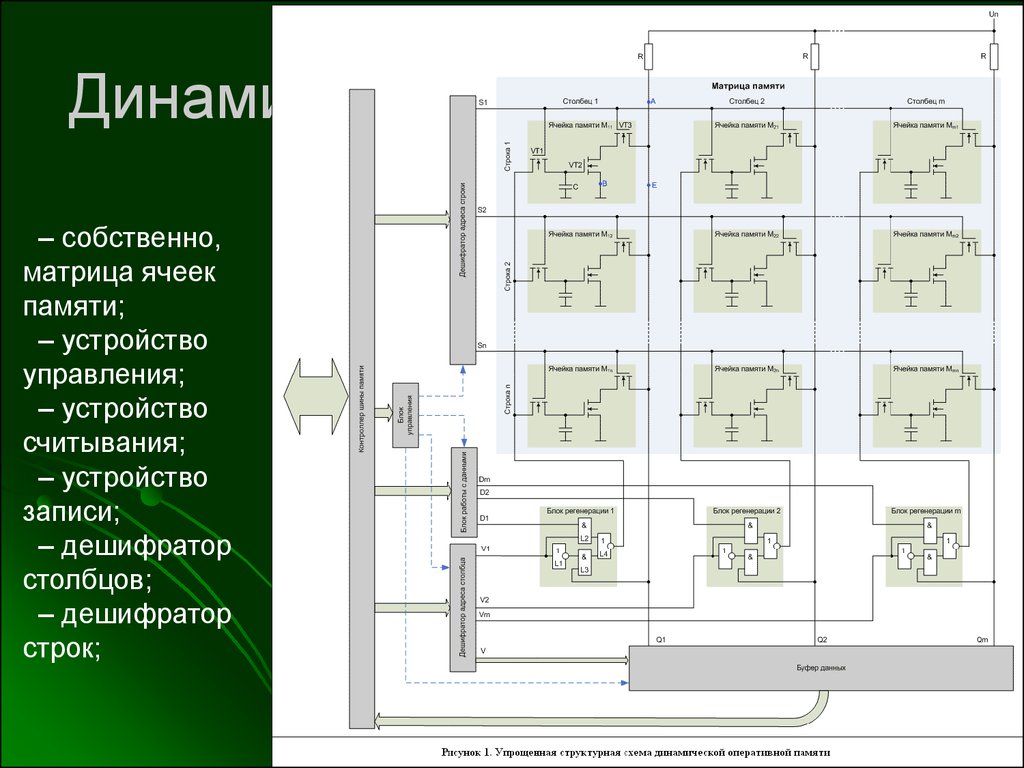

состоит– собственно,

матрица ячеек

памяти;

– устройство

управления;

– устройство

считывания;

– устройство

записи;

– дешифратор

столбцов;

– дешифратор

строк;

12. Динамическая память состоит

Динамическая память13. Динамическая память

Поскольку адрес строки являетсястаршей частью адреса, то для

последовательных адресов памяти

адрес строки одинаков (исключение

составляет переход через границу

строки).

http://www.ord.com.ru/files/book3/p231.ht

ml

14.

Типы памятиPM DRAM (Page Mode DRAM) использовалась до

середины 90-х годов.

1995 год: FPM DRAM (Fast Page Mode DRAM)

быстрая страничная память. Поддержка сохраненных

адресов: если новое считываемое из памяти слово

находится в той же строке, что и предыдущее, то

выборка данных осуществляется из буфера данных.

Запись данных в память осуществляется так же, как

и в PM DRAM. Следующий тип памяти, заменивший

FPM DRAM, появился через год (в 1996 году) и

назывался EDO-DRAM.

15. Типы памяти

1996 год: EDO-DRAM (Extended Data Out DRAM) –динамическая память с усовершенствованным

выходом. Адрес следующего считываемого слова

передается до завершения считывания данных (до

передачи данных процессору). Регистры – защелки.

При повышении частоты – нестабильная работа

SDRAM (Synchronous DRAM) – синхронная

динамическая память с произвольным доступом.

Память работает синхронно с контроллером памяти,

что гарантирует завершение цикла чтения/записи

строк в заданное время. Увеличено количество

матриц (одна регенерирует, другая работает)

16. Типы памяти

DDR SDRAM (Double Data Rate SDRAM) –синхронная динамическая память с произвольным

доступом и удвоенной частотой передачи данных:

обмен данными по внешней шине идет не только по

фронту тактового импульса, но и по спаду.

Увеличена разрядность внутренней шины данных (от

ячеек матриц памяти до буферов ввода-вывода)

То есть за 1 такт считывается столько данных,

сколько может передаваться по внешней шине за

два такта. Ширина внешней шины данных - 64 бита,

внутренней – 128 бит.

Увеличена сложность. Тайминги

17. Типы памяти

DDR2 SDRAM: ширина внутренней шины данных ещеувеличена в два раза и превосходит внешнюю шину

данных в четыре раза.

2005 год: DDR3 SDRAM .Повторное увеличение

вдвое ширины внутренней шины данных памяти

(снижение внутренней тактовой частоты памяти в

два раза). Новый технологический процесс, в начале

– до 90 нм, затем – до 65 нм, 50 нм, 40 нм.

2012-2015 гг: DDR4 продолжит тенденции DDR

памяти. Увеличение ширины внутренней шины,

улучшение технологии производства до 32-36 нм,

увеличение тактовых частот внешней и внутренней

шины, снижение напряжения.

18. Типы памяти

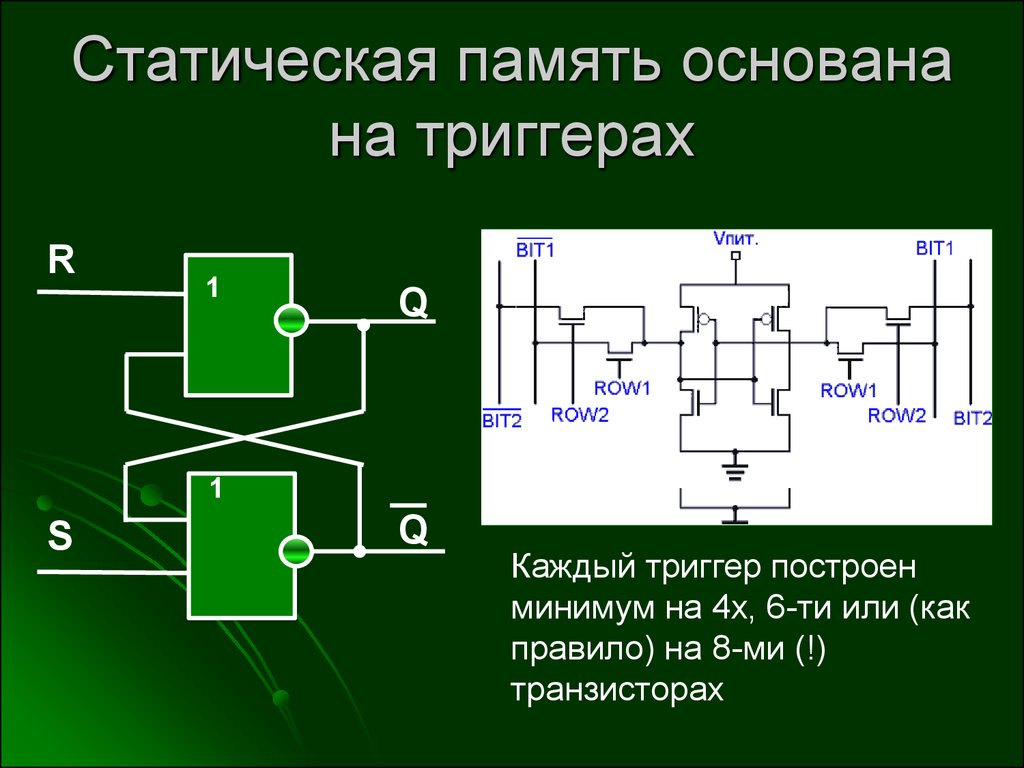

Статическая память основанана триггерах

R

1

Q

1

S

Q

Каждый триггер построен

минимум на 4х, 6-ти или (как

правило) на 8-ми (!)

транзисторах

19. Статическая память основана на триггерах

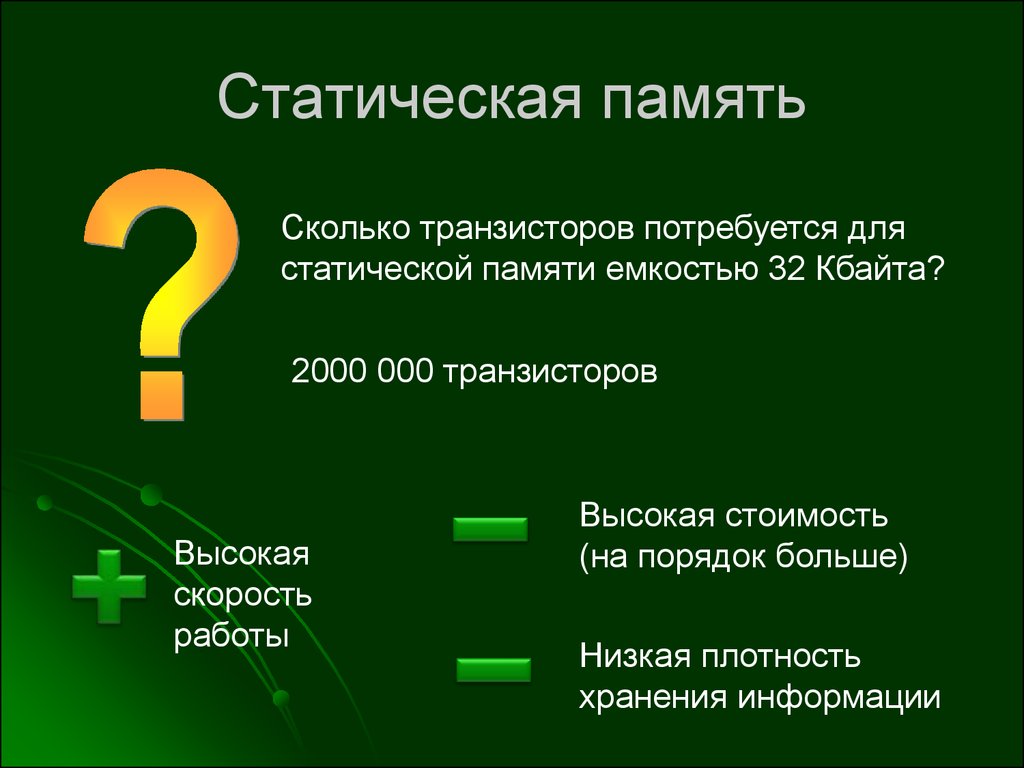

Статическая памятьСколько транзисторов потребуется для

статической памяти емкостью 32 Кбайта?

2000 000 транзисторов

Высокая

скорость

работы

Высокая стоимость

(на порядок больше)

Низкая плотность

хранения информации

20. Статическая память

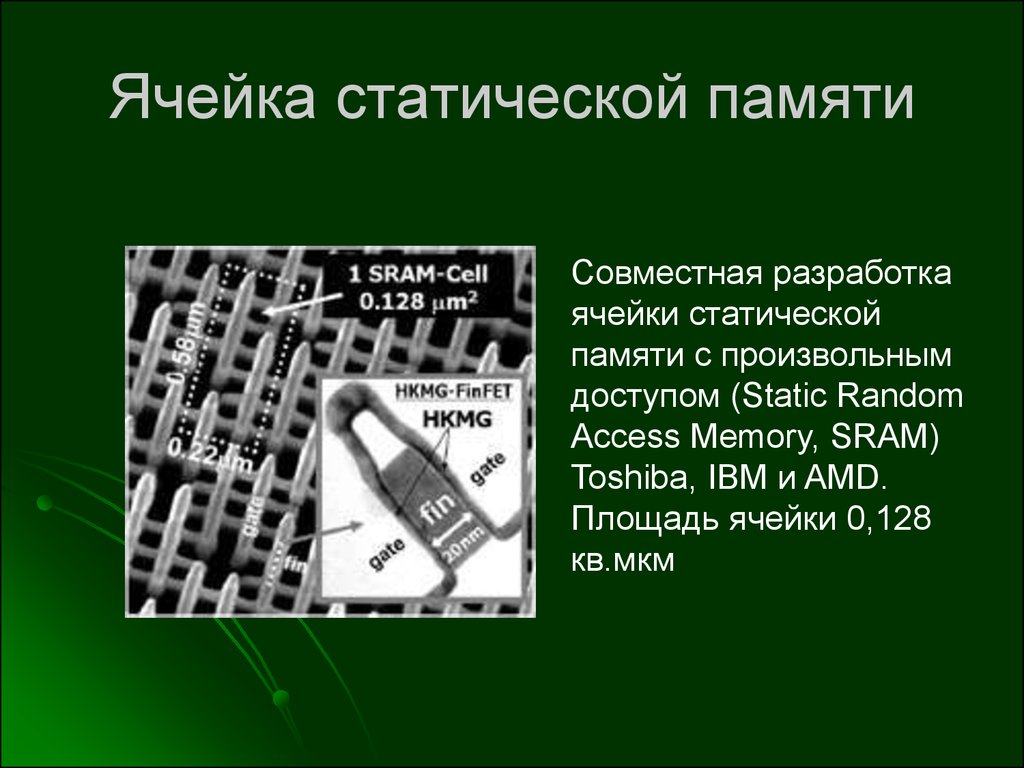

Ячейка статической памятиСовместная разработка

ячейки статической

памяти с произвольным

доступом (Static Random

Access Memory, SRAM)

Toshiba, IBM и AMD.

Площадь ячейки 0,128

кв.мкм

21. Ячейка статической памяти

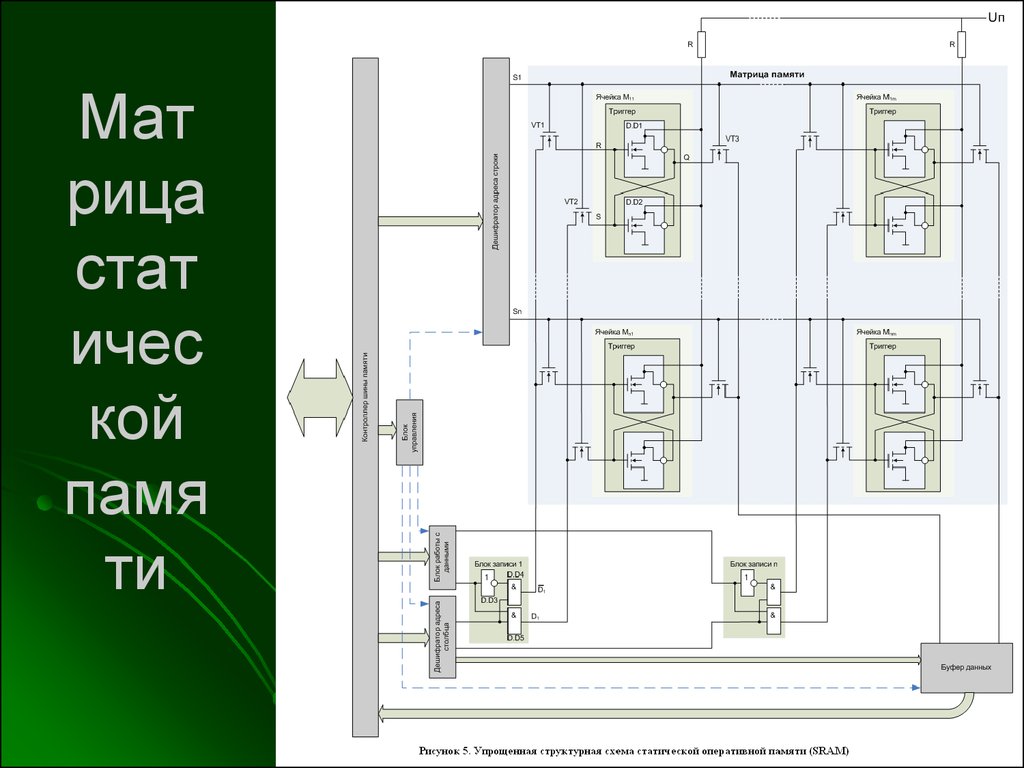

Матрица

стат

ичес

кой

памя

ти

22. Матрица статической памяти

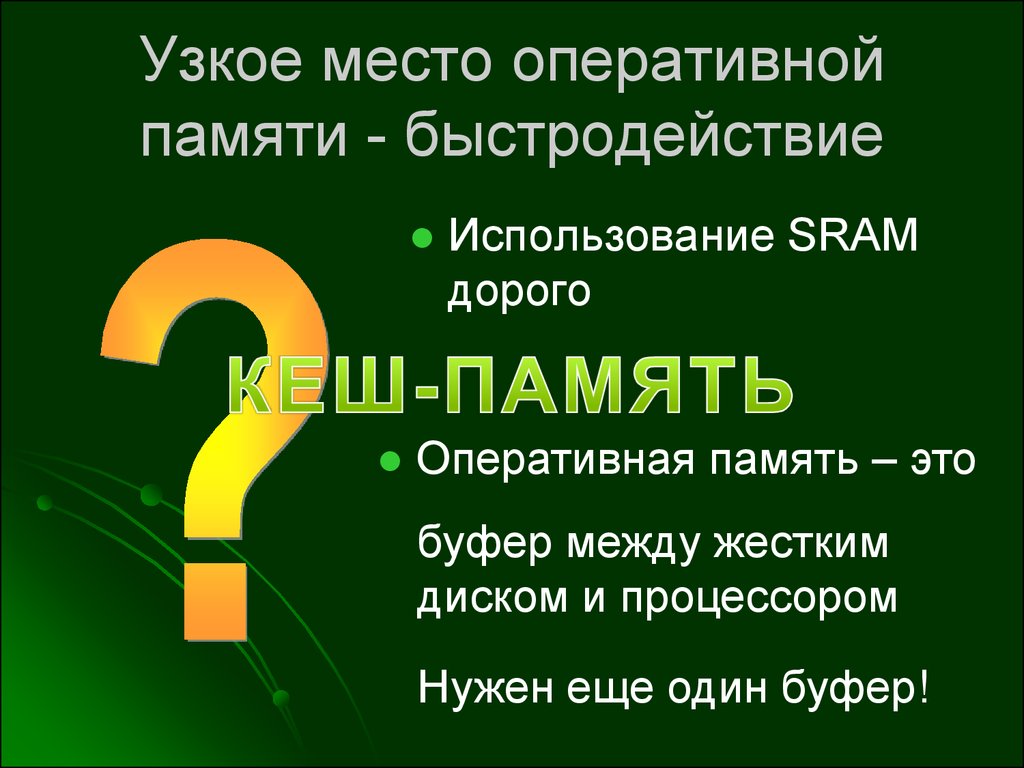

Узкое место оперативнойпамяти - быстродействие

80-90 гг.: тактовая частота

микропроцессора ~ 10 MHz; время

доступа оперативной памяти ~200 ns

Наше время: 1000 - 2000 MHz CPU и 20

ns DRAM

~3000 MHz CPU и 8 ns DRAM

23. Узкое место оперативной памяти - быстродействие

Использование SRAMдорого

Оперативная память – это

буфер между жестким

диском и процессором

Нужен еще один буфер!

24. Узкое место оперативной памяти - быстродействие

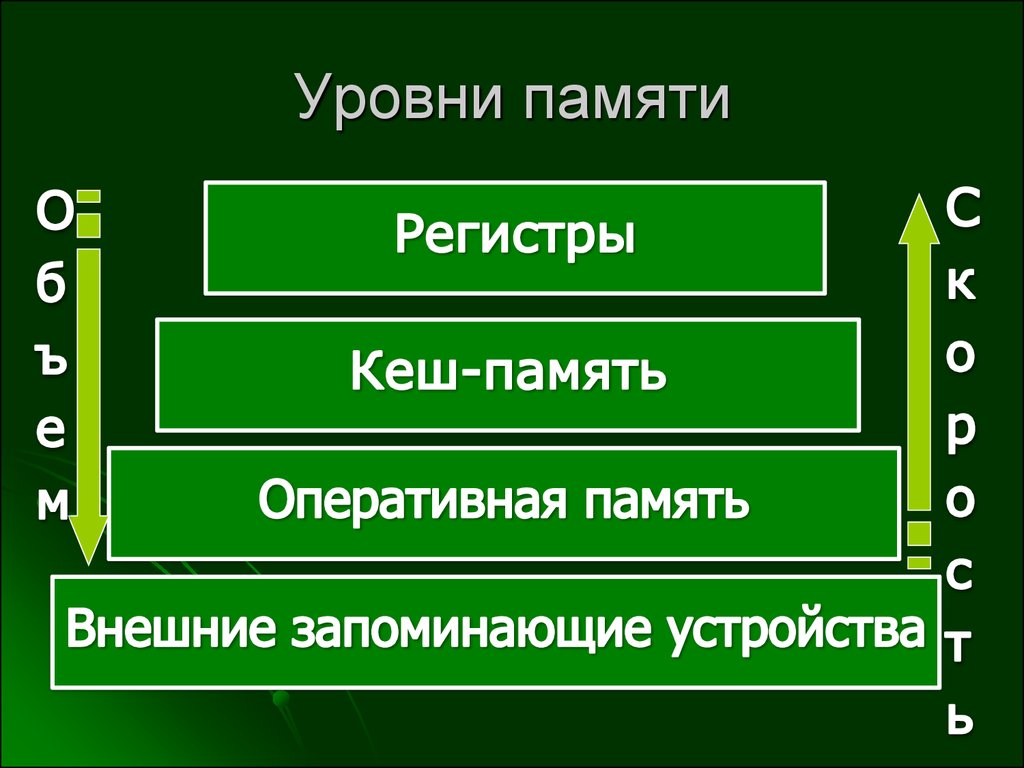

Уровни памяти25. Уровни памяти

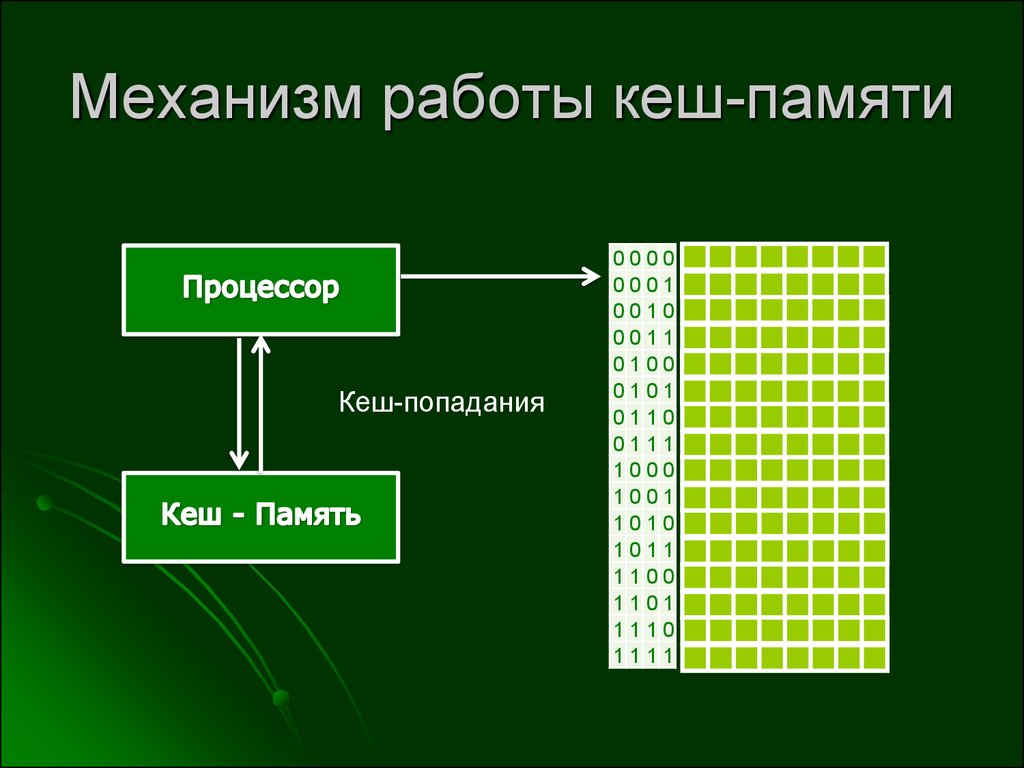

Кеш - памятьСверхоперативная

память

Невидима и прозрачна

для программиста

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

26.

Механизм работы кеш-памятиКеш-попадания

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

27. Механизм работы кеш-памяти

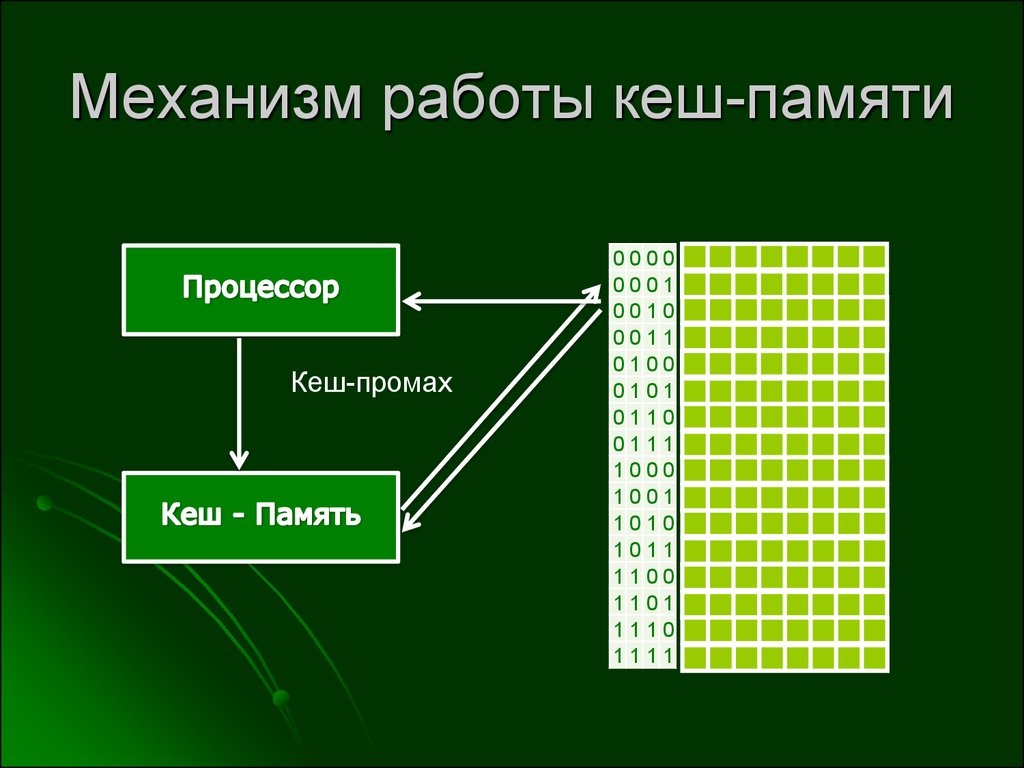

Кеш-промах0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

28. Механизм работы кеш-памяти

Архитектура Look AsideЗатраты энергии

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

29. Архитектура Look Aside

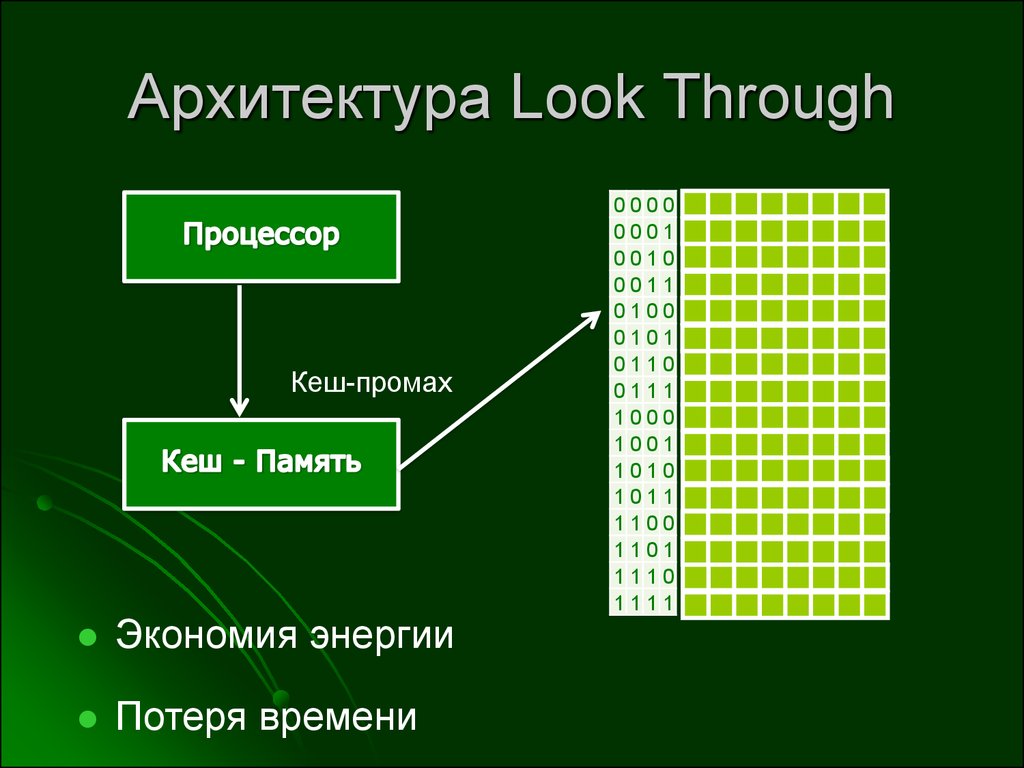

Архитектура Look ThroughКеш-промах

Экономия энергии

Потеря времени

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

30. Архитектура Look Through

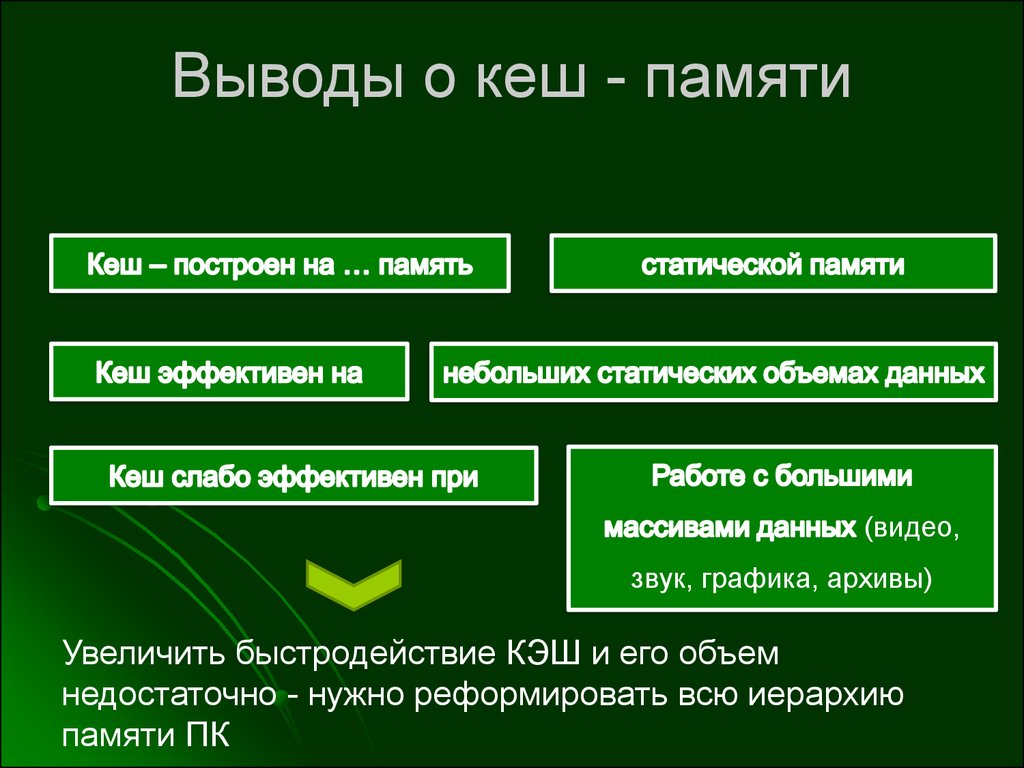

Выводы о кеш - памяти(видео,

звук, графика, архивы)

Увеличить быстродействие КЭШ и его объем

недостаточно - нужно реформировать всю иерархию

памяти ПК

31.

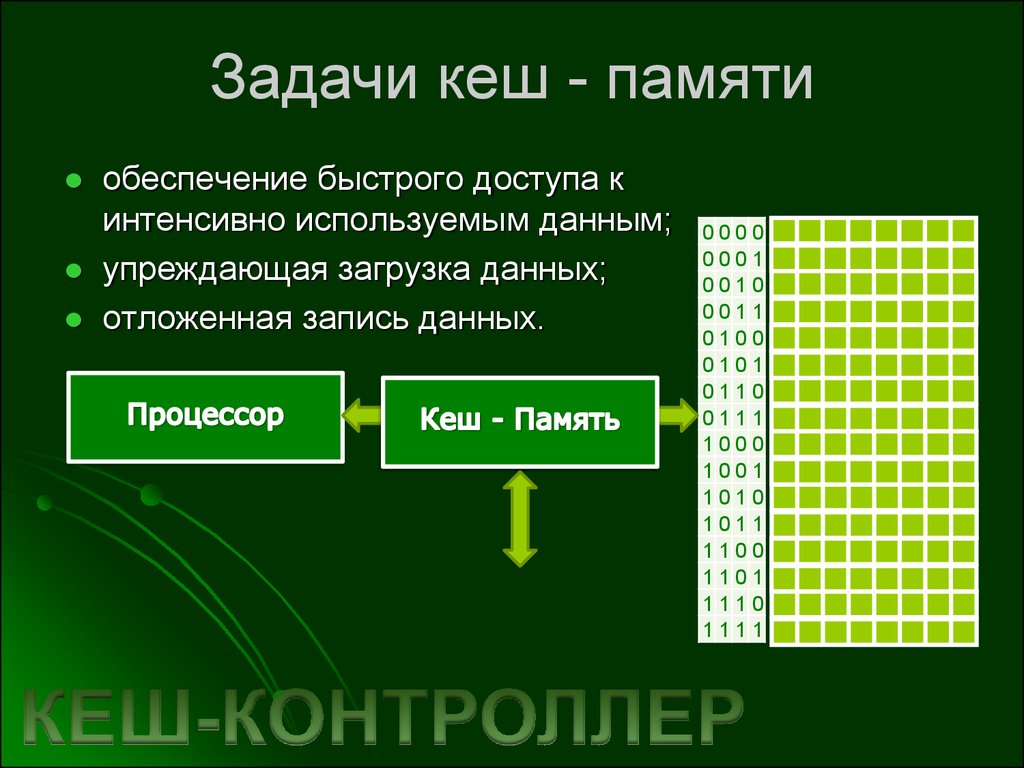

Задачи кеш - памятиобеспечение быстрого доступа к

интенсивно используемым данным;

упреждающая загрузка данных;

отложенная запись данных.

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

32.

Задачи кеш - контроллераа) накопление нужных данных

б) своевременное удаление

неиспользуемых данных.

Кеш заполняется

Стратегии

кеширования:

помещать копию

запрошенных данных

в кеш? – обращение

было - помещаем

Стратегии замещения:

Частотный анализ (сложно)

LRU - Least Recently Used

FIFO - First Input First Output

33.

Задачи кеш - контроллераСогласование интерфейсов процессора

и контроллера памяти:

• процессор оперирует байтами или

словами.

• обмен с физической оперативной

памятью - четыре 64-разрядных ячейки.

34.

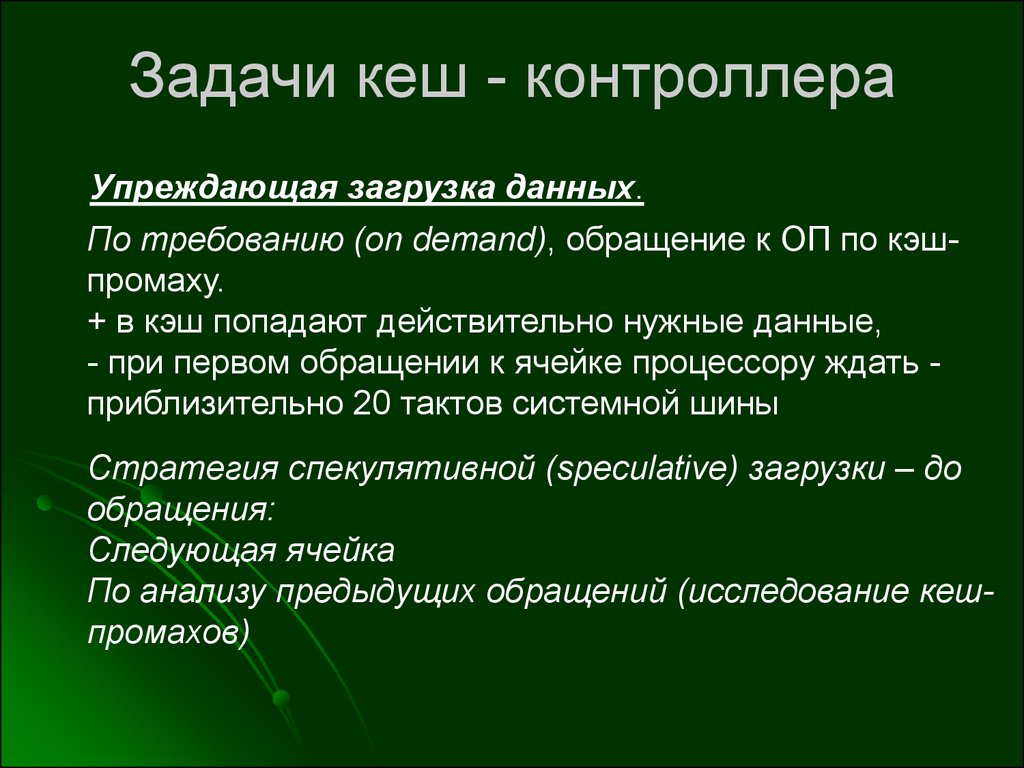

Задачи кеш - контроллераУпреждающая загрузка данных.

По требованию (on demand), обращение к ОП по кэшпромаху.

+ в кэш попадают действительно нужные данные,

- при первом обращении к ячейке процессору ждать приблизительно 20 тактов системной шины

Стратегия спекулятивной (speculative) загрузки – до

обращения:

Следующая ячейка

По анализу предыдущих обращений (исследование кешпромахов)

35.

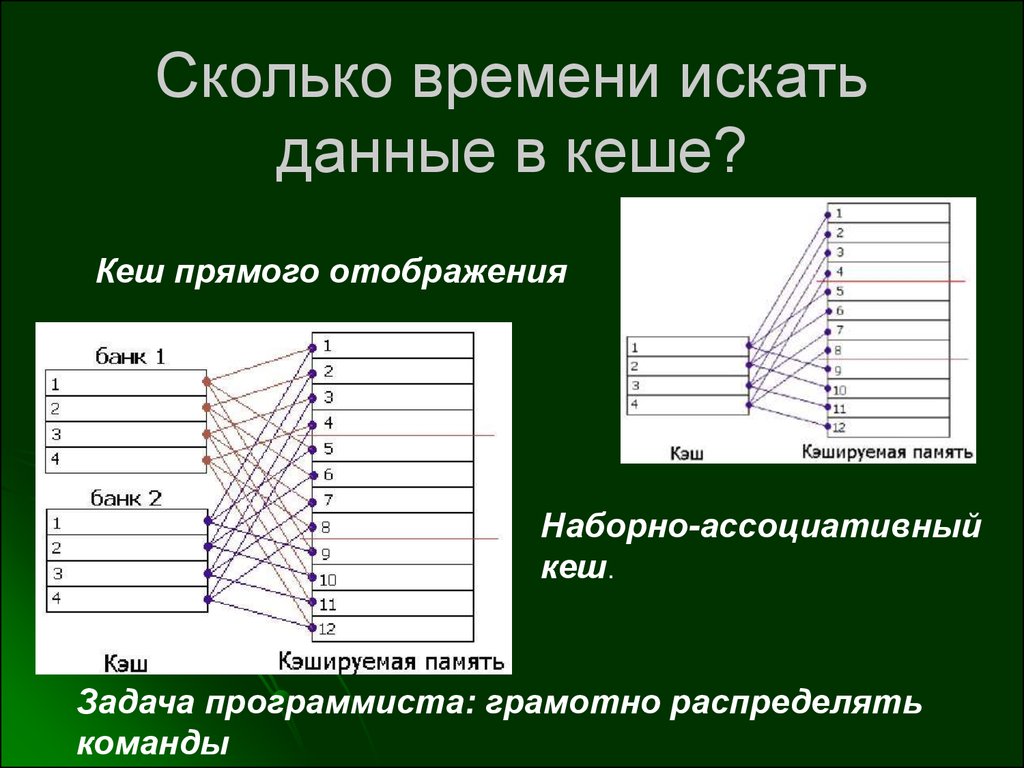

Сколько времени искатьданные в кеше?

Кеш прямого отображения

Наборно-ассоциативный

кеш.

Задача программиста: грамотно распределять

команды

36.

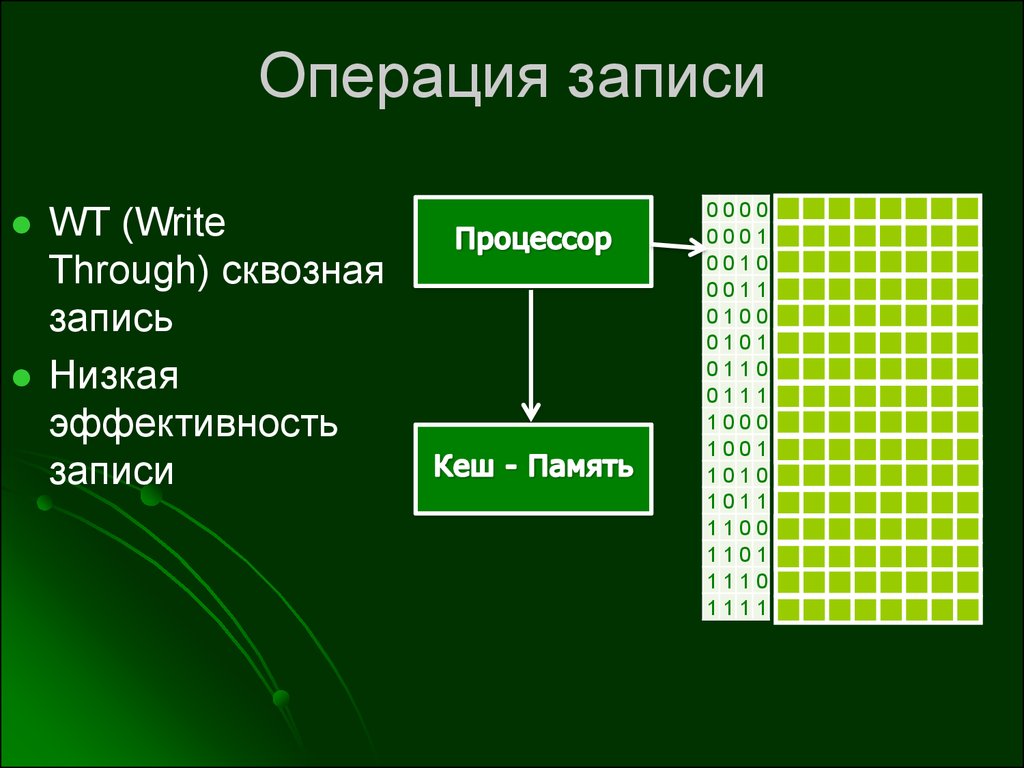

Операция записиWT (Write

Through) сквозная

запись

Низкая

эффективность

записи

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

37.

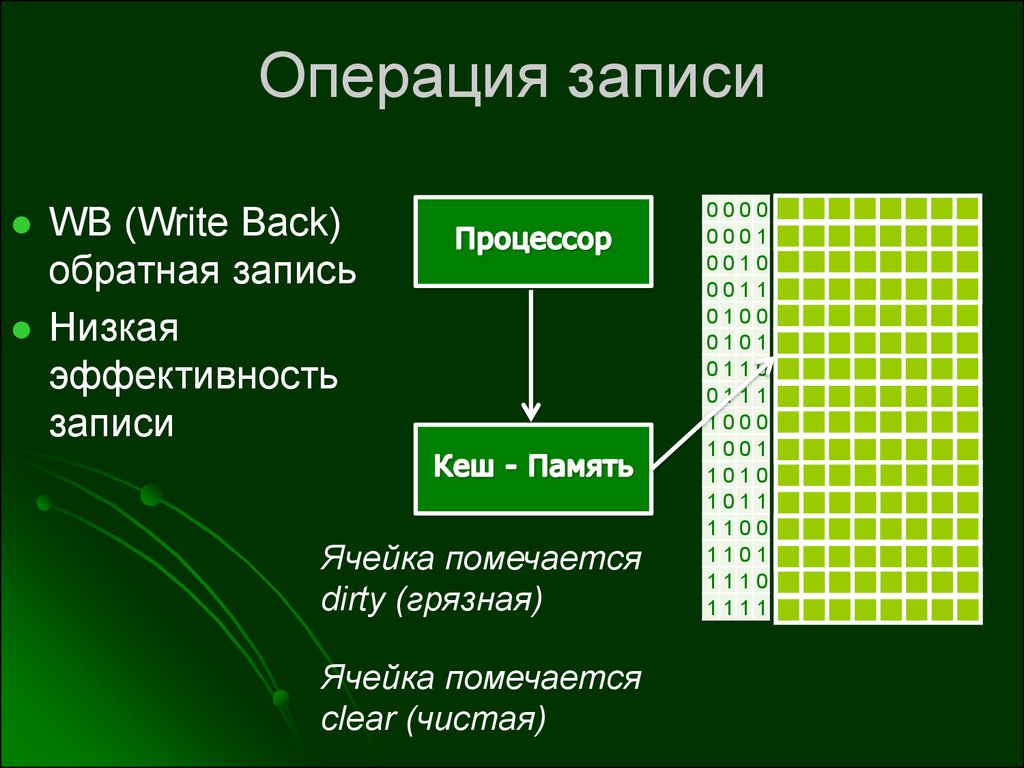

Операция записиWB (Write Back)

обратная запись

Низкая

эффективность

записи

Ячейка помечается

dirty (грязная)

Ячейка помечается

clear (чистая)

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

38.

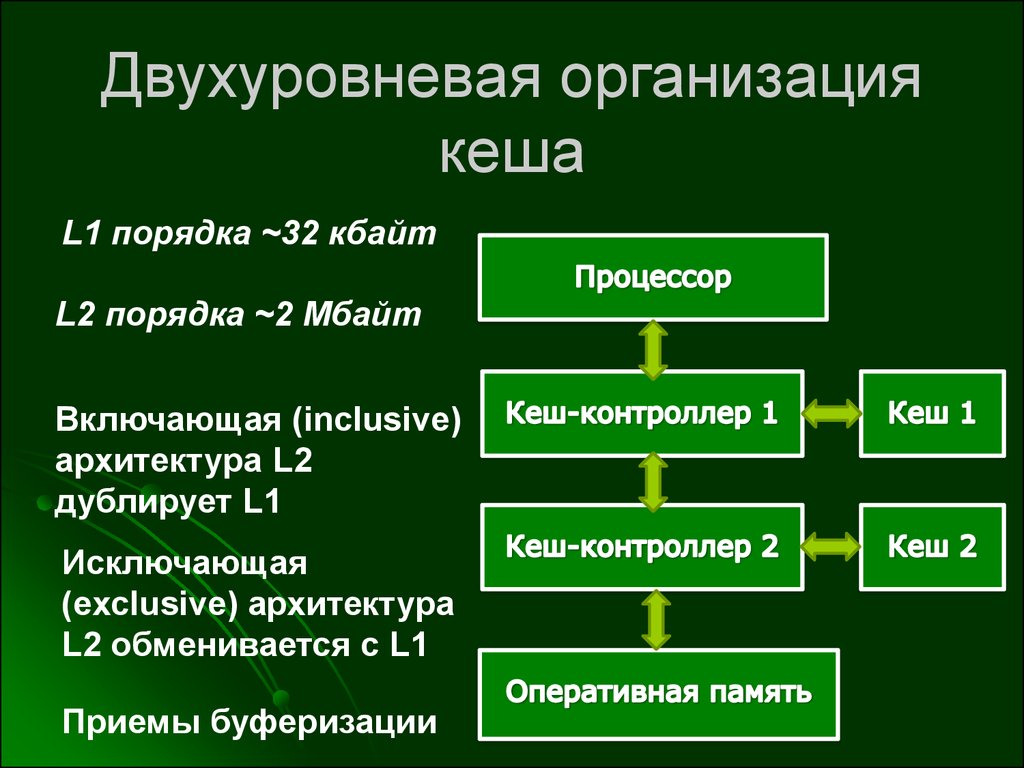

Двухуровневая организациякеша

L1 порядка ~32 кбайт

L2 порядка ~2 Мбайт

Включающая (inclusive)

архитектура L2

дублирует L1

Исключающая

(exclusive) архитектура

L2 обменивается с L1

Приемы буферизации

informatics

informatics