Similar presentations:

Организация ЭВМ и систем. Основные характеристики системы памяти. Кэш-память. (Лекция 10)

1. Организация ЭВМ и систем

Лекция № 10• Основные характеристики системы

памяти

• Распределение адресного пространства

• Новые технологии памяти

• Кэш-память

• Типы кэш-памяти

• Особенности обновления информации в

кэш-памяти

2. Организация интерфейса памяти

Появления32-разрядного

МП

определило

использование 3 новых концепций организации

интерфейса памяти.

Расширение шины локальной памяти. Было

использовано для увеличения емкости этой памяти

по сравнению с тем, который мог быть на

процессорной плате.

Расслоение (интерливинг) памяти. Используется

для повышения скорости следующих друг за другом

обращений к памяти.

Виртуальное управление памятью. В 32-разрядных

МП два вида организации виртуальной памяти:

1.

2.

3.

Страничная

Сегментная

3. Иерархия подсистемы памяти ПК

Регистровая память (сверхоперативноезапоминающее устройство).

2. Буферная память (кэш-память – для согласования

скорости работы ЦП и основной памяти).

• I-го уровня – L1

• II-го уровня – L2

3. Основная память (ОЗУ, ПЗУ).

4. Массовая (внешняя память).

1.

4. Кэш-память

Кэш-памятьпредставляет

собой

быстродействующее ЗУ, размещенное на одном

кристалле с ЦП или внешнее по отношению к ЦП, служит

высокоскоростным буфером между ЦП и относительно

медленной основной памятью.

Идея кэш-памяти основана на прогнозировании

наиболее вероятных обращений ЦП к ОП. В основу

такого подхода положен принцип временной и

пространственной локальности программы.

Кэш-память представляет собой 2 сверхоперативные

памяти:

• Память отображения данных.

• Память тегов.

5.

1.2.

3.

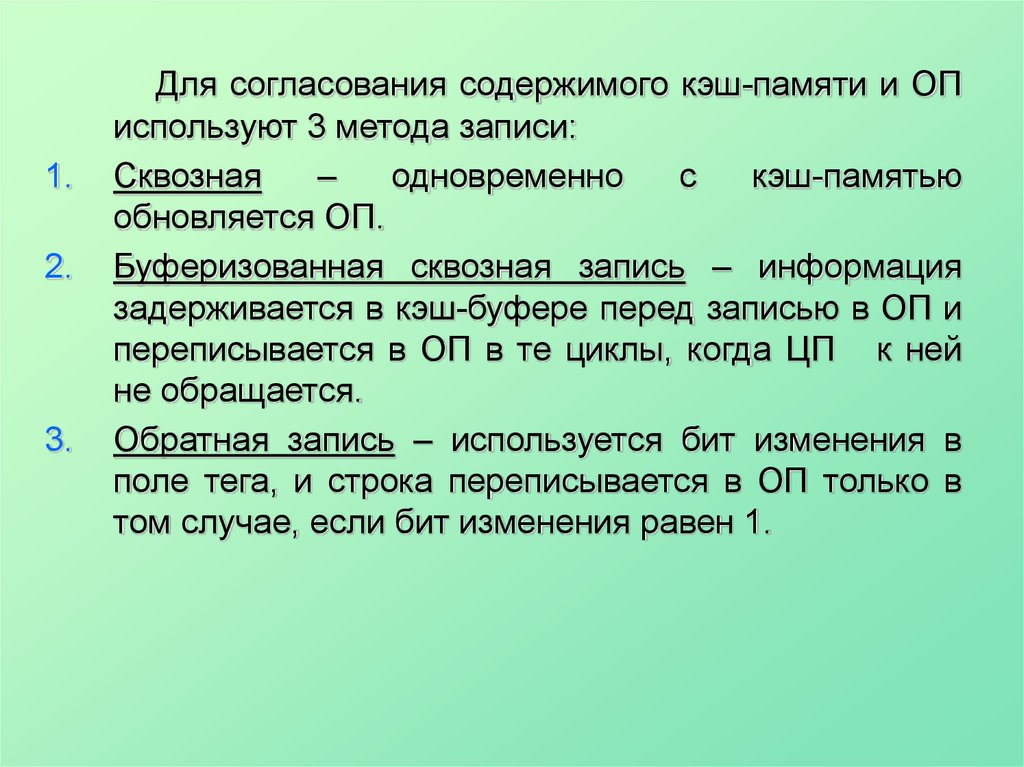

Для согласования содержимого кэш-памяти и ОП

используют 3 метода записи:

Сквозная

–

одновременно

с

кэш-памятью

обновляется ОП.

Буферизованная сквозная запись – информация

задерживается в кэш-буфере перед записью в ОП и

переписывается в ОП в те циклы, когда ЦП к ней

не обращается.

Обратная запись – используется бит изменения в

поле тега, и строка переписывается в ОП только в

том случае, если бит изменения равен 1.

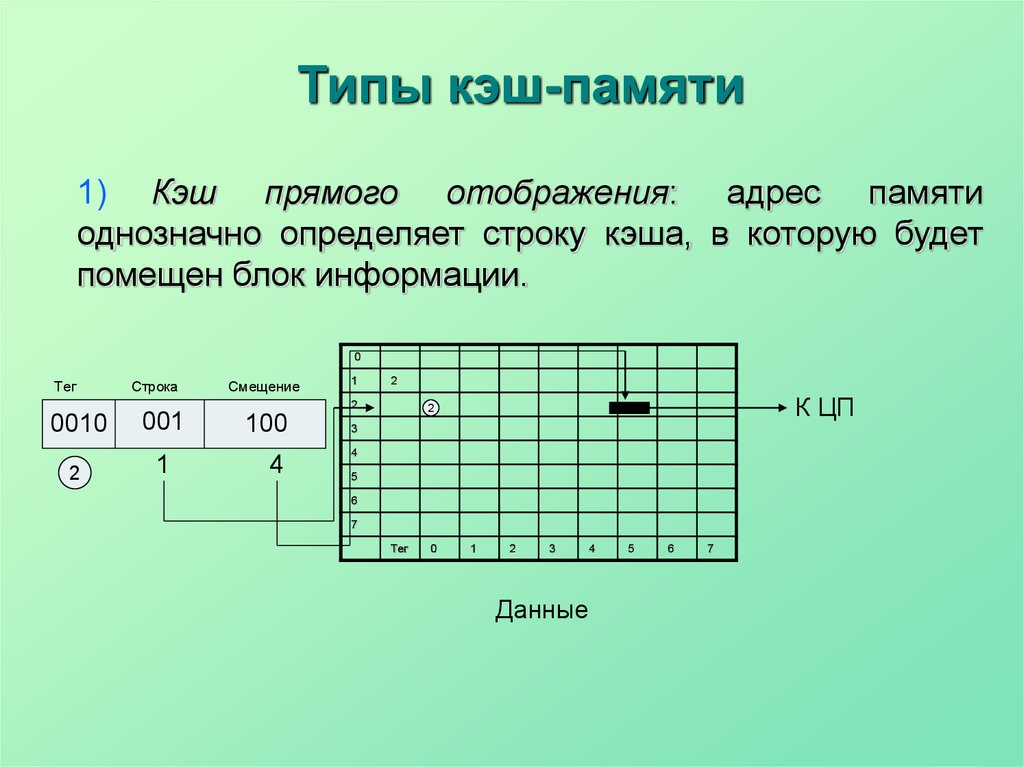

6. Типы кэш-памяти

1) Кэш прямого отображения: адрес памятиоднозначно определяет строку кэша, в которую будет

помещен блок информации.

0

Тег

Строка

Смещение

1

2

2

0010

001

2

1

100

4

К ЦП

2

3

4

5

6

7

Тег

0

1

2

3

4

Данные

5

6

7

7.

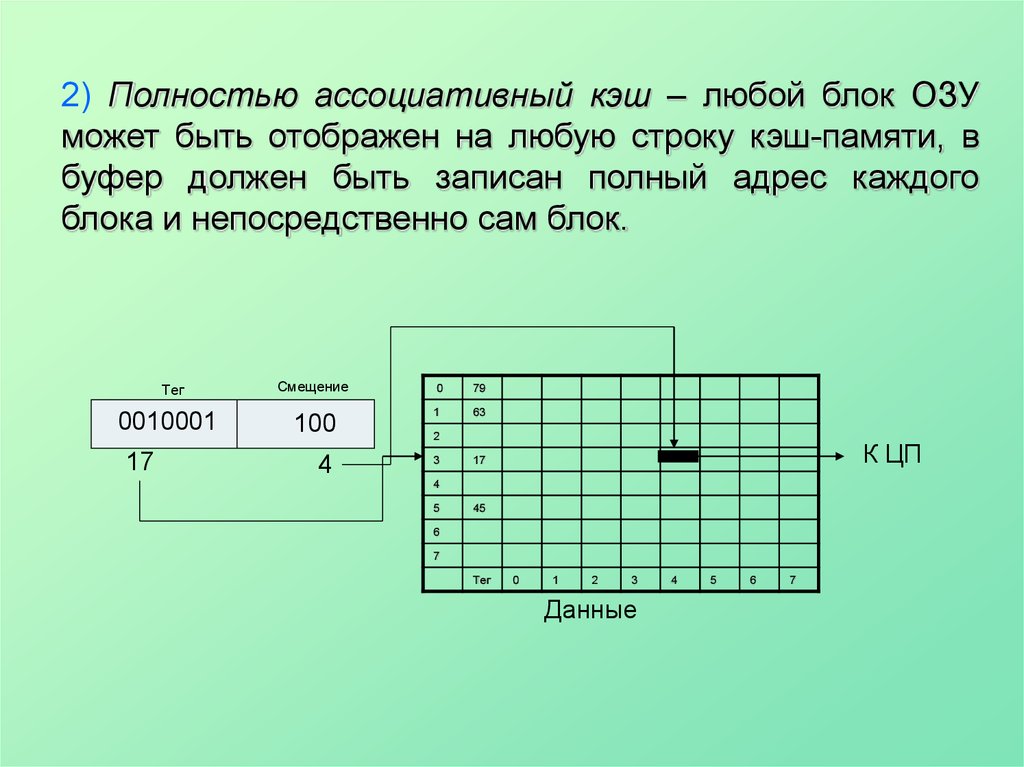

2) Полностью ассоциативный кэш – любой блок ОЗУможет быть отображен на любую строку кэш-памяти, в

буфер должен быть записан полный адрес каждого

блока и непосредственно сам блок.

Тег

0010001

17

Смещение

100

4

0

79

1

63

2

3

К ЦП

17

4

5

45

6

7

Тег

0

1

2

3

Данные

4

5

6

7

8.

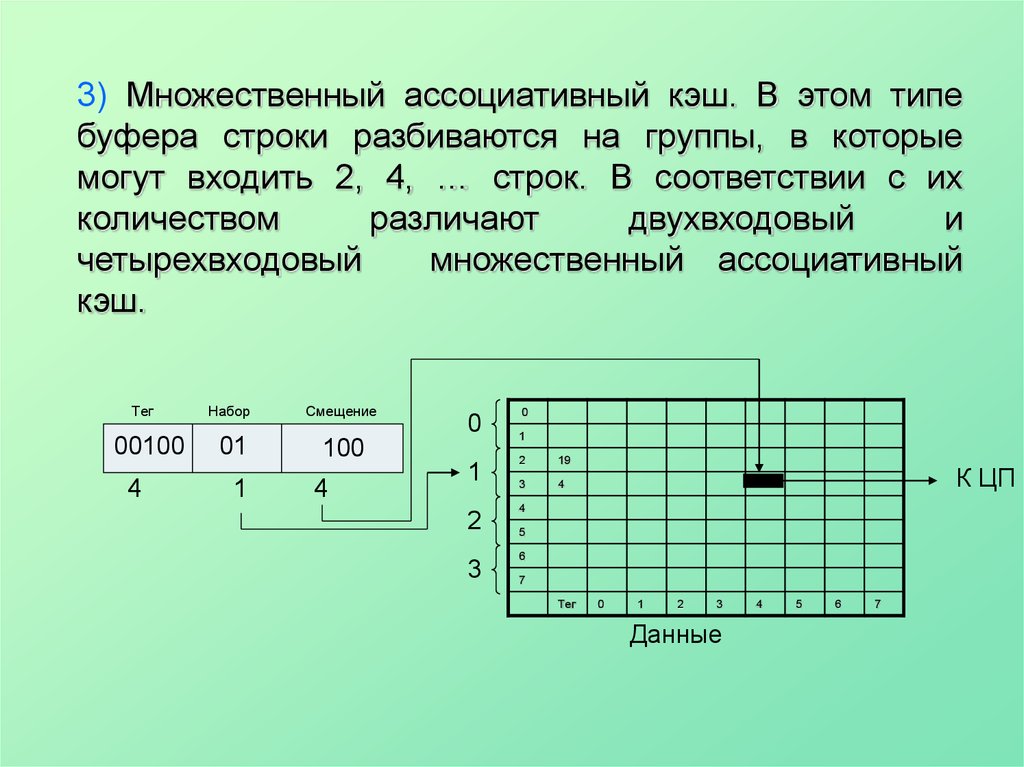

3) Множественный ассоциативный кэш. В этом типебуфера строки разбиваются на группы, в которые

могут входить 2, 4, … строк. В соответствии с их

количеством

различают

двухвходовый

и

четырехвходовый

множественный ассоциативный

кэш.

Тег

00100

4

Набор

Смещение

01

100

1

4

0

1

2

3

0

1

2

19

3

4

К ЦП

4

5

6

7

Тег

0

1

2

3

Данные

4

5

6

7

9. Типы кэш-памяти

• Кэш Гарвардской архитектуры – раздельные кэшкоманд и кэш-данных.• Кэш Принстонской архитектуры (Джона фон Неймана)

– смешанные кэш-команд и кэш-данных.

10. Размер и эффективность кэш-памяти

Размер кэшпамятиНет кэш, DRAM c

2 TW

16 Кб

Попадания, %

Выигрыш, %

0

0

81

35

32 Кб

86

38

64 Кб

88

39

128 Кб

89

39

Нет кэш, SRAM

без TW

100

47

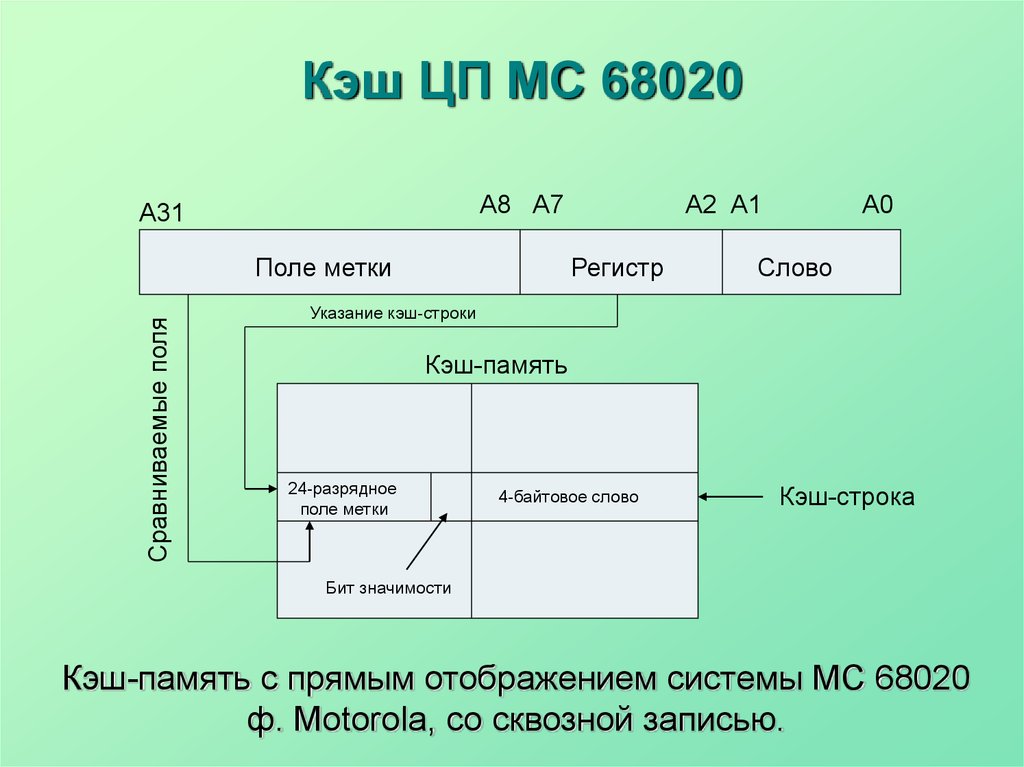

11. Кэш ЦП МС 68020

А8 А7А31

Сравниваемые поля

Поле метки

А2 А1

Регистр

А0

Слово

Указание кэш-строки

Кэш-память

24-разрядное

поле метки

4-байтовое слово

Кэш-строка

Бит значимости

Кэш-память с прямым отображением системы МС 68020

ф. Motorola, со сквозной записью.

12. Новые технологии памяти

Дляповышения

быстродействия

DRAM

используются 2 основных схемотехнических решения:

• Включение в микросхемы динамической памяти

некоторого количества статической памяти.

• Синхронная работа памяти и ЦП, т.е. использование

внутренней конвейерной архитектуры и чередование

адресов.

13. Новые технологи памяти

CDRAM (Cache DRAM)

Добавление

SRAM (8, 16 Кб)

EDRAM (Enhanced DRAM )

3-х ступенчатый конвейер

банка памяти с доступом

SDRAM (Synchronous DRAM) 2типа

«пинг-понг».

Функционирует по протоколу

RDRAM (Rambus DRAM) расщепления транзакций

набор

EDO (Extended Data Out) DRAM Добавлен

регистров – «защелок»

BEDO DRAM (Burst EDO DRAM)

– Double Data Rate – данные передаются по

DDR400SDRAM DDRпереднему

и заднему фронтам импульса.

14. FPM DRAM

• Идет последовательное обращение к ячейкам однойстроки матрицы. При этом сигнал RAS# удерживается

на низком уровне, а адрес строки выставляется на

шине адреса всего один раз.

• Преимущество: экономим время - адрес строки

выставляем один раз вместо четырех. Способность

работать в таком режиме обеспечивает контроллер

памяти.

Преимуществами

FPM

позволяет

воспользоваться

конвейерная

организация

применяемая в процессорах Intel начиная с 80286.

• Стандартная память со временем доступа 60 нс при

частоте системной шины 66МГц может обеспечить

лучший режим 5-3-3-3. Время доступа внутри страницы

- 35нс.

15. EDO DRAM

• Выходные данные сохраняются в специальномрегистре - регистре-защелке. Считывание из него

производится внешними схемами вплоть до спада

следующего импульса CAS#. Время доступа внутри

страницы

снижается

до

25нс,

повышая

производительность на 40%. Наилучший режим

чтения - 5-2-2-2.

• Установка

регистра-защелки

практически

не

увеличивает стоимость микросхемы, однако ее

применение дает эффект соизмеримый с установкой

внешнего асинхронного кэша.

16. BEDO DRAM

Является развитием конвейерной архитектуры.Кроме регистра-защелки появляется счетчик адреса

колонок для пакетного цикла, что позволяет выставлять

адрес колонки только в его начале, а в последующих

передачах только запрашивать очередные данные. В

результате удлинения конвейера выходные данные как

бы отстают на один сигнал CAS#, зато следующие

появляются без тактов ожидания. При этом стартовый

адрес следующего пакета пересылается вместе с

последним CAS# сигналом предыдущего. Наилучший

цикл - 5-1-1-1. Если чипсет способен генерировать

обращения к памяти в режиме смежных циклов, то

выигрыш в производительности

17. SDRAM

Synchronous (синхронная) DRAM синхронизирована ссистемным таймером, управляющим центральным

процессором. Часы, управляющие микропроцессором,

также управляют работой SDRAM, уменьшая временные

задержки в процессе циклов ожидания и ускоряя поиск

данных. Эта синхронизация позволяет контроллеру

памяти точно знать время готовности данных. Таким

образом, скорость доступа увеличивается благодаря

тому, что данные доступны во время каждого такта

таймера, в то время как у EDO RAM данные бывают

доступны один раз за два такта, а у FPM - один раз за три

такта. Технология SDRAM позволяет использовать

множественные

банки

памяти,

функционирующие

одновременно, дополнительно к адресации целыми

блоками.

18.

МикросхемыSDRAM

имеют

программируемые

параметры и свои наборы команд. Длина пакетного

цикла чтения-записи может программироваться (1, 2, 4,

8, 256 элементов). Цикл может быть прерван

специальной командой без утери данных. Конвейерная

организация позволяет инициировать следующий цикл

чтения до окончания предыдущего.

SDRAM II (DDR)

Synchronous DRAM II, или DDR (Double Data Rate удвоенная скорость передачи данных) - следующее

поколение существующей SDRAM. DDR основана на тех

же принципах, что и SDRAM, однако включает некоторые

усовершенствования,

позволяющие

увеличить

быстродействие.

19.

Основные отличия от стандартного SDRAM: вопервыхиспользуется

более

"продвинутая"

синхронизация, отсутствующая в SDRAM; а во-вторых

DDR использует DLL (delay-locked loop - цикл с

фиксированной задержкой) для выдачи сигнала

DataStrobe, означающего доступность данных на

выходных контактах.

Используя один сигнал DataStrobe на каждые 16

выводов, контроллер может осуществлять доступ к

данным более точно и синхронизировать входящие

данные, поступающие из разных модулей, находящихся

в одном банке. DDR фактически увеличивает скорость

доступа вдвое, по сравнению с SDRAM, используя при

этом ту же частоту. В результате, DDR позволяет читать

данные по восходящему и падающему уровню таймера,

выполняя два доступа за время одного обращения

стандартной SDRAM.

20. RDRAM

RDRAM - многофункциональный протоколобмена данными между микросхемами, позволяющий

передачу данных по упрощенной шине, работающей на

высокой частоте. RDRAM представляет собой

интегрированную на системном уровне технологию.

Ключевыми элементами RDRAM являются:

• модули DRAM, базирующиеся на Rambus;

• ячейки Rambus ASIC (RACs);

• схема соединения чипов, называемая Rambus Channel.

21.

RamBus, впервые использованный в графическихрабочих станциях в 1995 году, использует уникальную

технологию RSL (Rambus Signal Logic - сигнальная

логика Rambus), позволяющую использование частот

передачи данных до 600MHz на обычных системах и

материнских платах.

Rambus использует низковольтовые сигналы и

обеспечивает передачу данных по обоим уровням

сигнала системного таймера. RDRAM использует 8битовый интерфейс, в то время как EDO RAM и SDRAM

используют 4-, 8- и 16-битовый интерфейс. RAMBUS

запатентована 11 крупнейшими производителями DRAM,

обеспечивающими 85% всего рынка памяти.

22. Direct Rambus

Технология Direct Rambus - еще одно расширениеRDRAM. Direct RDRAM имеют те же уровни сигналов

(RSL: Rambus Signaling Level - уровень сигналов

Rambus), но более широкую шину (16 бит), более

высокие частоты (выше 800MHz) и улучшенный протокол

(эффективность выше на 90%). Однобанковый модуль

RDRAM

будет

обеспечивать

скорость

передачи

1.6Гбайт/сек, двухбанковый - 3.2Гбайт/сек. Direct Rambus

использует два 8-битных канала для передачи 1.6Гбайт и

3 канала для получения 2.4Гбайт.

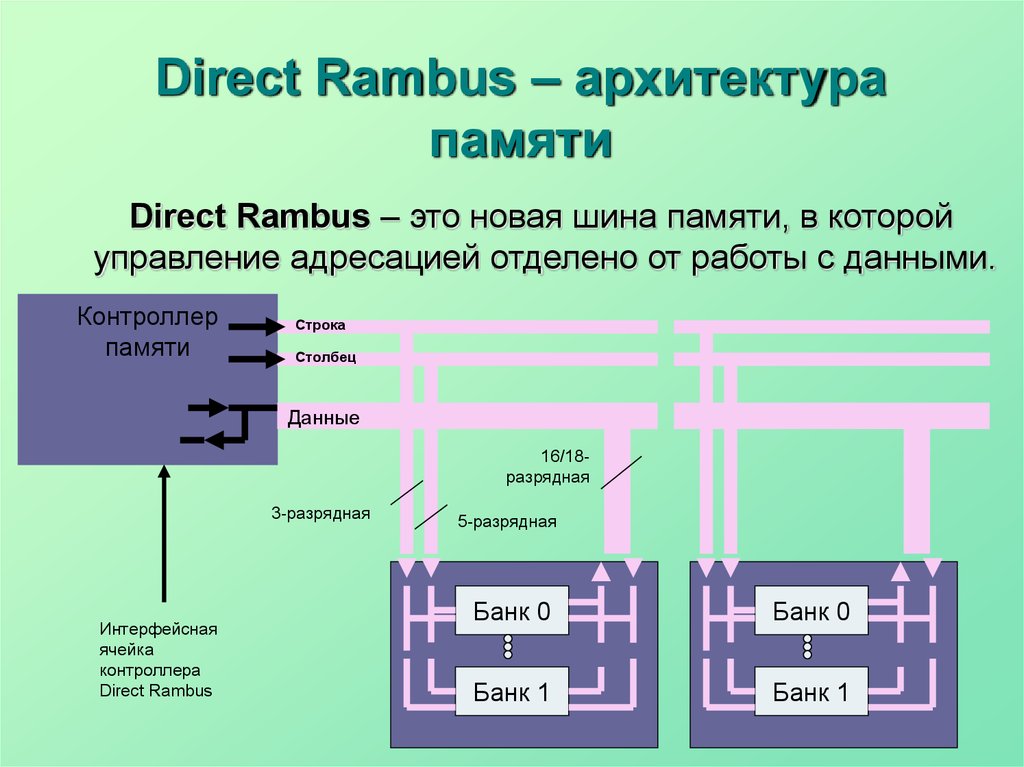

23. Direct Rambus – архитектура памяти

Direct Rambus – это новая шина памяти, в которойуправление адресацией отделено от работы с данными.

Контроллер

памяти

Строка

Столбец

Данные

16/18разрядная

3-разрядная

Интерфейсная

ячейка

контроллера

Direct Rambus

5-разрядная

Банк 0

Банк

Банк0 0

Банк 1

Банк

Банк1 1

24. Вопросы для самоконтроля

1.2.

3.

4.

5.

6.

7.

Какая память в ПК является самой быстрой?

Объясните, в чем состоит принцип временной и

пространственной локальности программы.

Какая информация хранится в сегменте состояния

задачи?

Какие способы существуют для согласования

содержимого кэш-памяти и основной памяти?

Перечислите типы кэш-памяти.

Какие схемотехнические решения используются для

повышения быстродействия DRAM?

В каких микросхемах динамической памяти

используется включение некоторого количества

статической памяти?

25. Вопросы для самоконтроля

В каких микросхемах динамической памятииспользуется внутренняя конвейерная архитектура?

9. В каких микросхемах динамической памяти

используются множественные банки памяти,

функционирующие одновременно?

10. В каких микросхемах динамической памяти передача

данных происходит по обоим уровням сигнала

системного таймера?

8.

electronics

electronics