Similar presentations:

Исследование работы элементов компьютерной логики. Лабораторная работа №1

1.

Лабораторная работа № 1ИССЛЕДОВАНИЕ РАБОТЫ

ЭЛЕМЕНТОВ КОМПЬЮТЕРНОЙ

ЛОГИКИ

2.

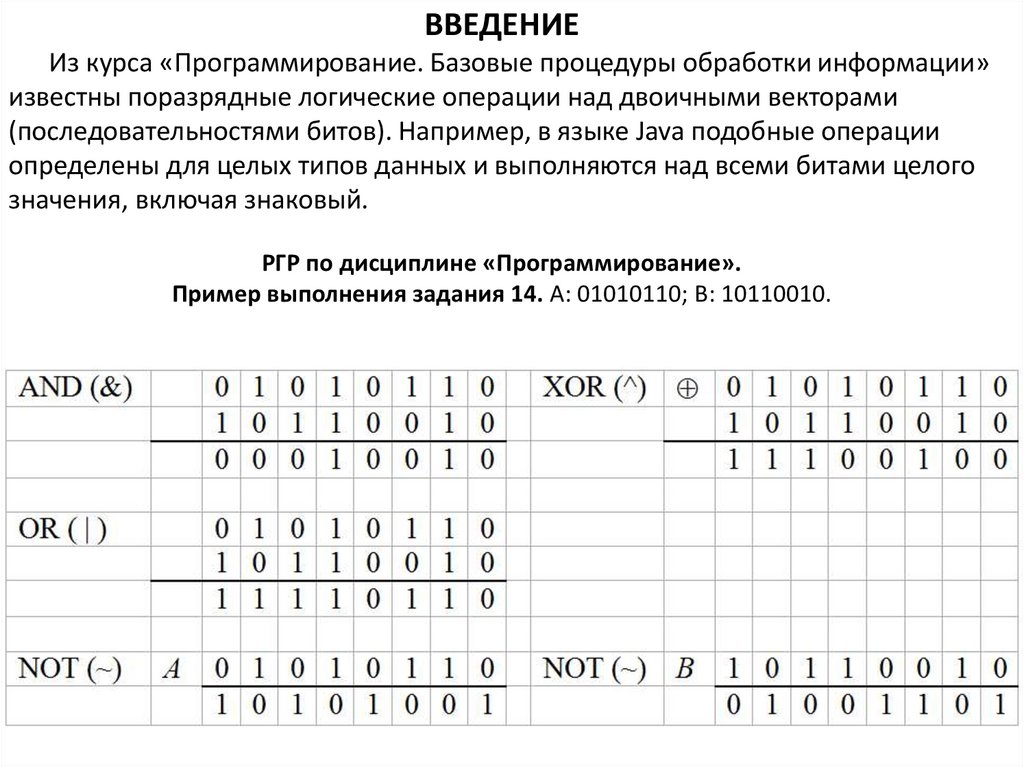

ВВЕДЕНИЕИз курса «Программирование. Базовые процедуры обработки информации»

известны поразрядные логические операции над двоичными векторами

(последовательностями битов). Например, в языке Java подобные операции

определены для целых типов данных и выполняются над всеми битами целого

значения, включая знаковый.

РГР по дисциплине «Программирование».

Пример выполнения задания 14. A: 01010110; B: 10110010.

3.

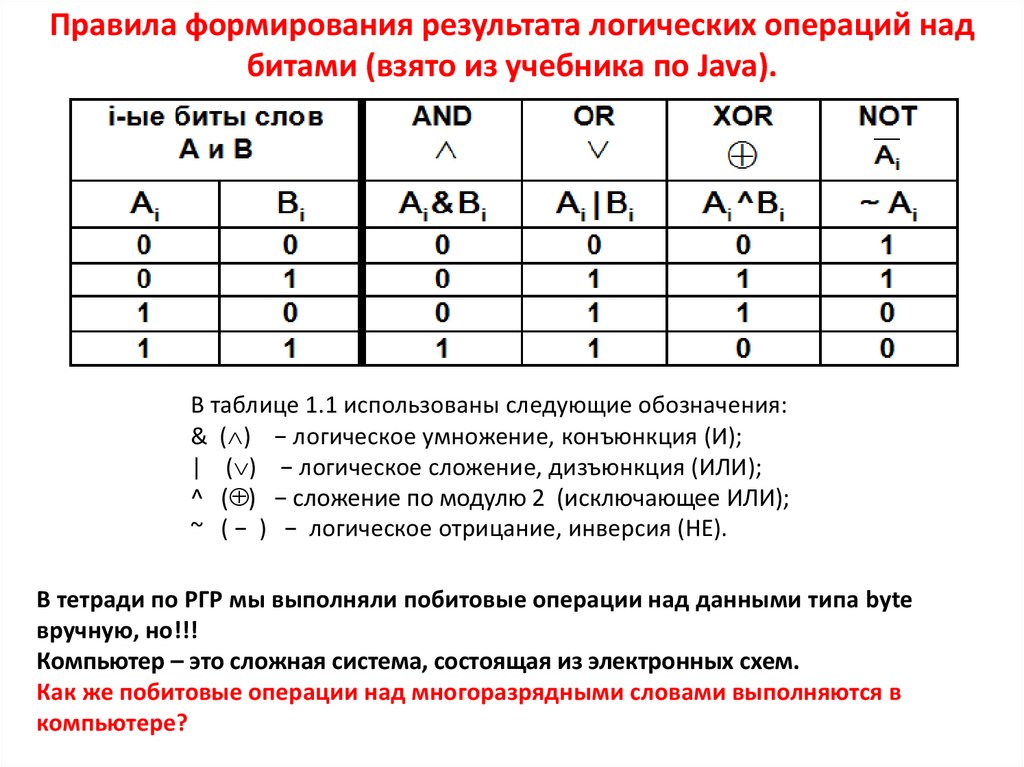

Правила формирования результата логических операций надбитами (взято из учебника по Java).

В таблице 1.1 использованы следующие обозначения:

& ( ) − логическое умножение, конъюнкция (И);

| ( ) − логическое сложение, дизъюнкция (ИЛИ);

^ ( ) − сложение по модулю 2 (исключающее ИЛИ);

~ ( − ) − логическое отрицание, инверсия (НЕ).

В тетради по РГР мы выполняли побитовые операции над данными типа byte

вручную, но!!!

Компьютер – это сложная система, состоящая из электронных схем.

Как же побитовые операции над многоразрядными словами выполняются в

компьютере?

4.

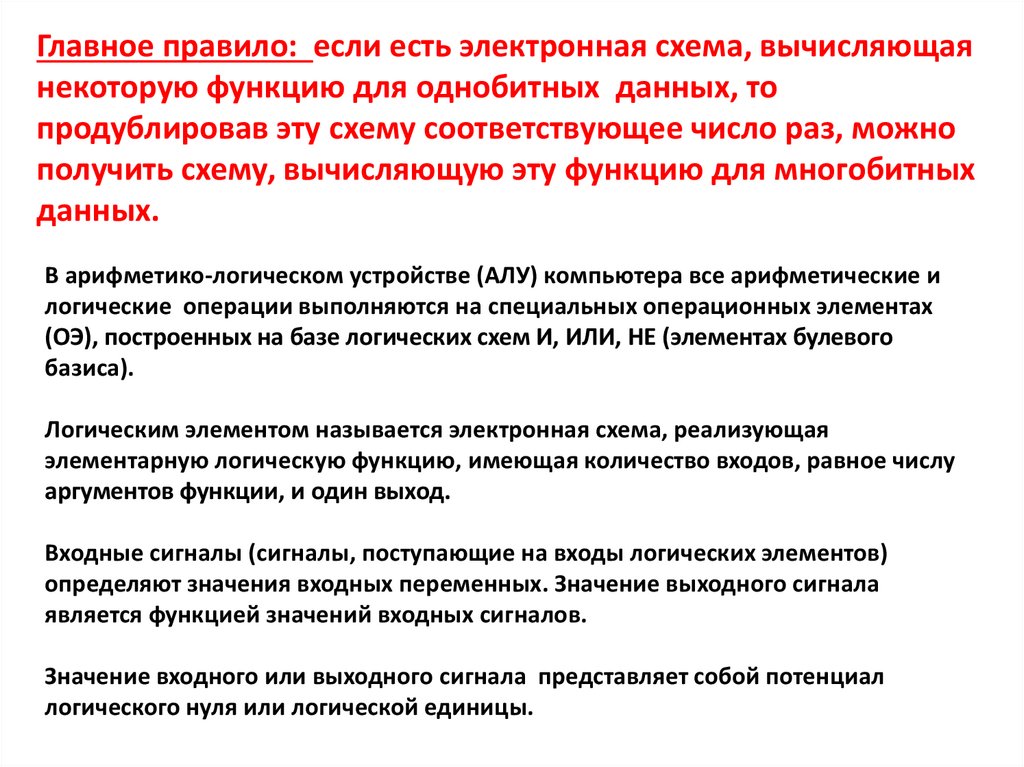

Главное правило: если есть электронная схема, вычисляющаянекоторую функцию для однобитных данных, то

продублировав эту схему соответствующее число раз, можно

получить схему, вычисляющую эту функцию для многобитных

данных.

В арифметико-логическом устройстве (АЛУ) компьютера все арифметические и

логические операции выполняются на специальных операционных элементах

(ОЭ), построенных на базе логических схем И, ИЛИ, НЕ (элементах булевого

базиса).

Логическим элементом называется электронная схема, реализующая

элементарную логическую функцию, имеющая количество входов, равное числу

аргументов функции, и один выход.

Входные сигналы (сигналы, поступающие на входы логических элементов)

определяют значения входных переменных. Значение выходного сигнала

является функцией значений входных сигналов.

Значение входного или выходного сигнала представляет собой потенциал

логического нуля или логической единицы.

5.

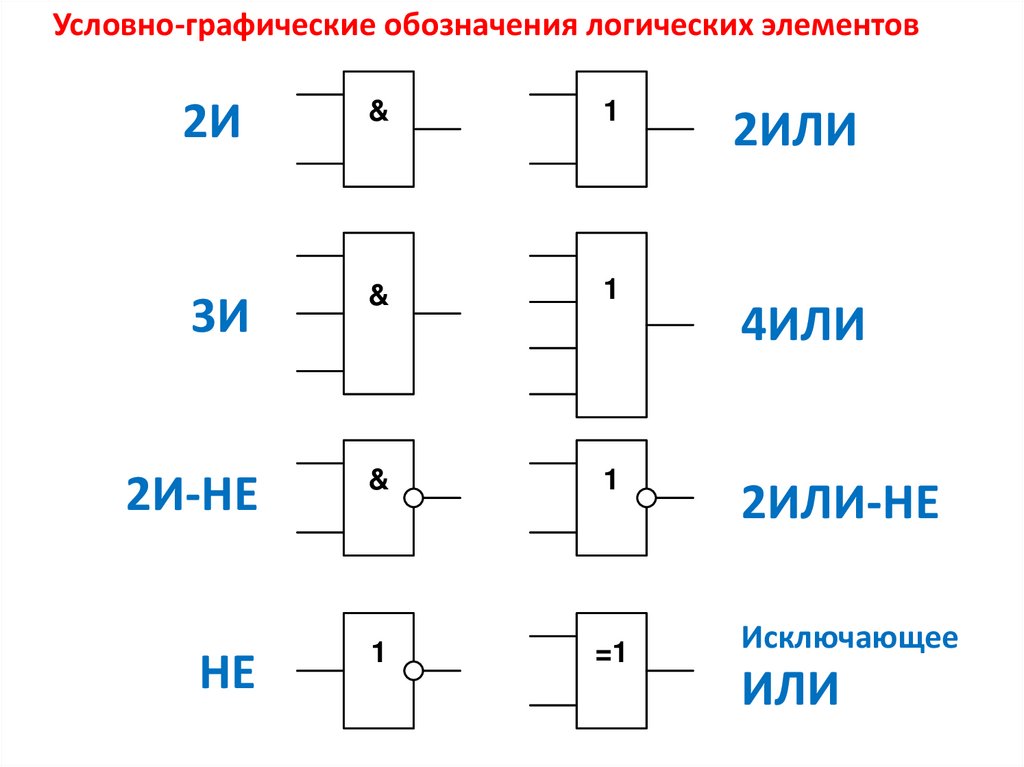

Условно-графические обозначения логических элементов2И

&

1

3И

&

1

2И-НЕ

&

1

НЕ

1

=1

2ИЛИ

4ИЛИ

2ИЛИ-НЕ

Исключающее

ИЛИ

6.

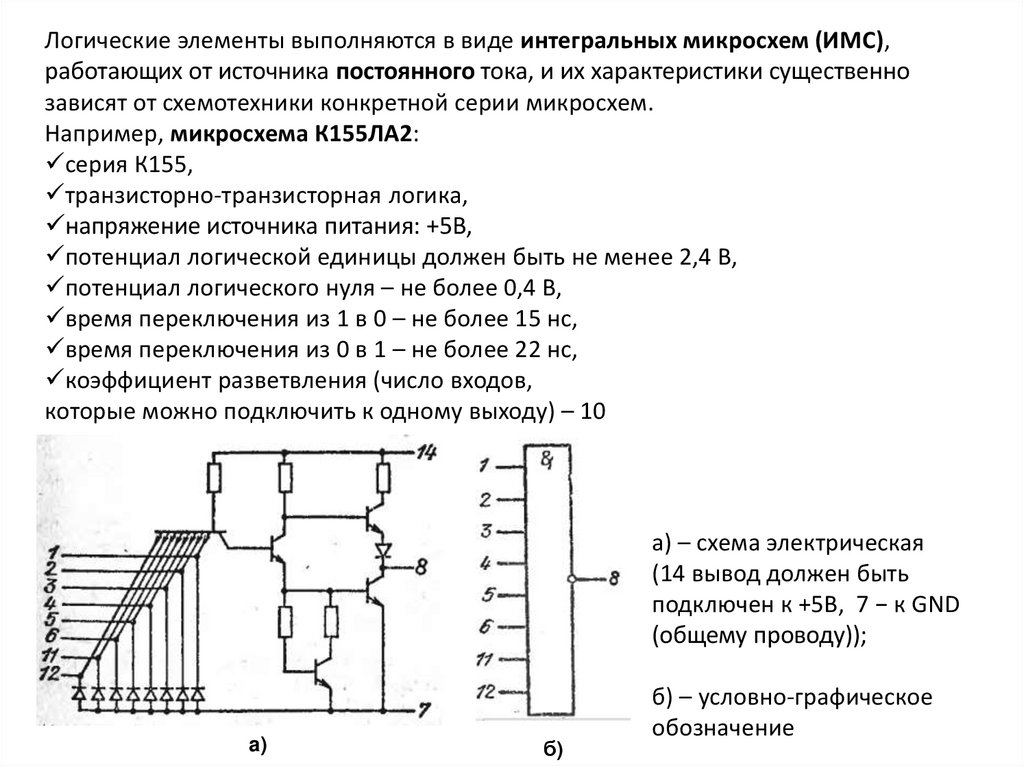

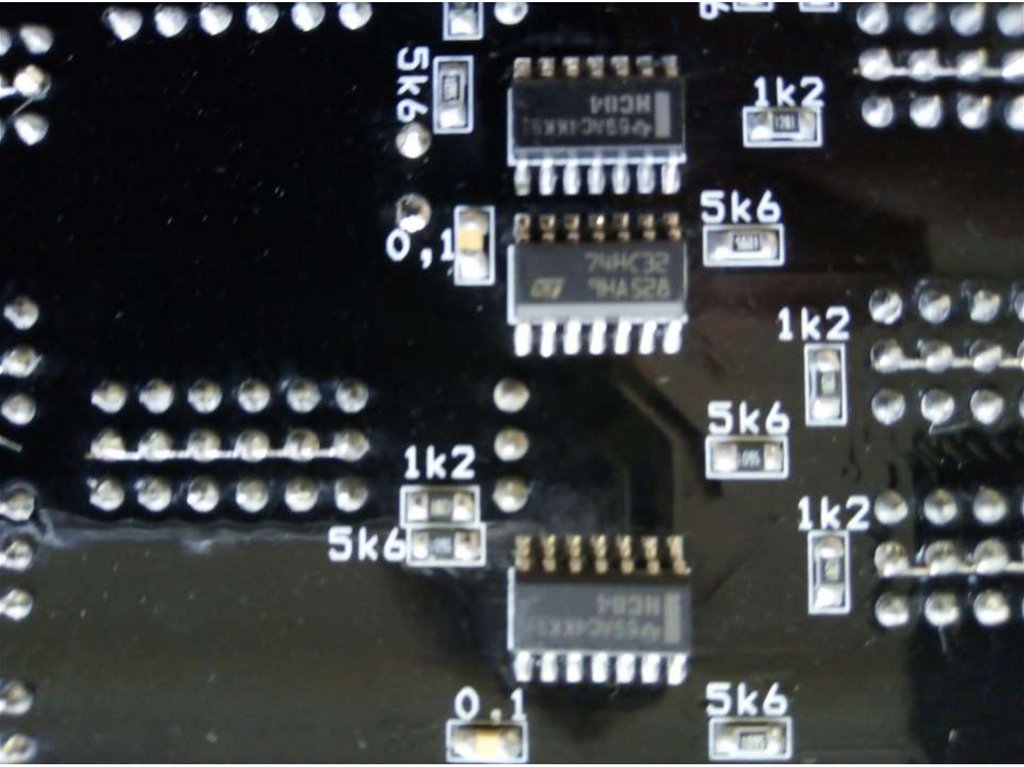

Логические элементы выполняются в виде интегральных микросхем (ИМС),работающих от источника постоянного тока, и их характеристики существенно

зависят от схемотехники конкретной серии микросхем.

Например, микросхема К155ЛА2:

серия К155,

транзисторно-транзисторная логика,

напряжение источника питания: +5В,

потенциал логической единицы должен быть не менее 2,4 В,

потенциал логического нуля – не более 0,4 В,

время переключения из 1 в 0 – не более 15 нс,

время переключения из 0 в 1 – не более 22 нс,

коэффициент разветвления (число входов,

которые можно подключить к одному выходу) – 10

a) – схема электрическая

(14 вывод должен быть

подключен к +5В, 7 − к GND

(общему проводу));

a)

б)

б) – условно-графическое

обозначение

7.

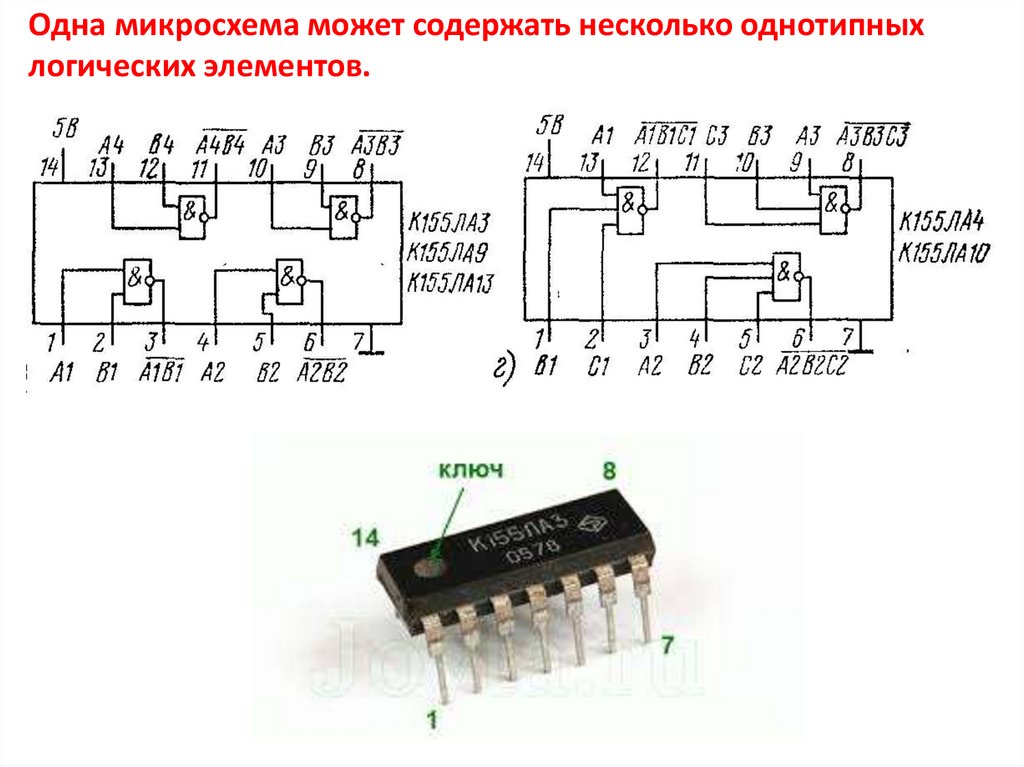

Одна микросхема может содержать несколько однотипныхлогических элементов.

8.

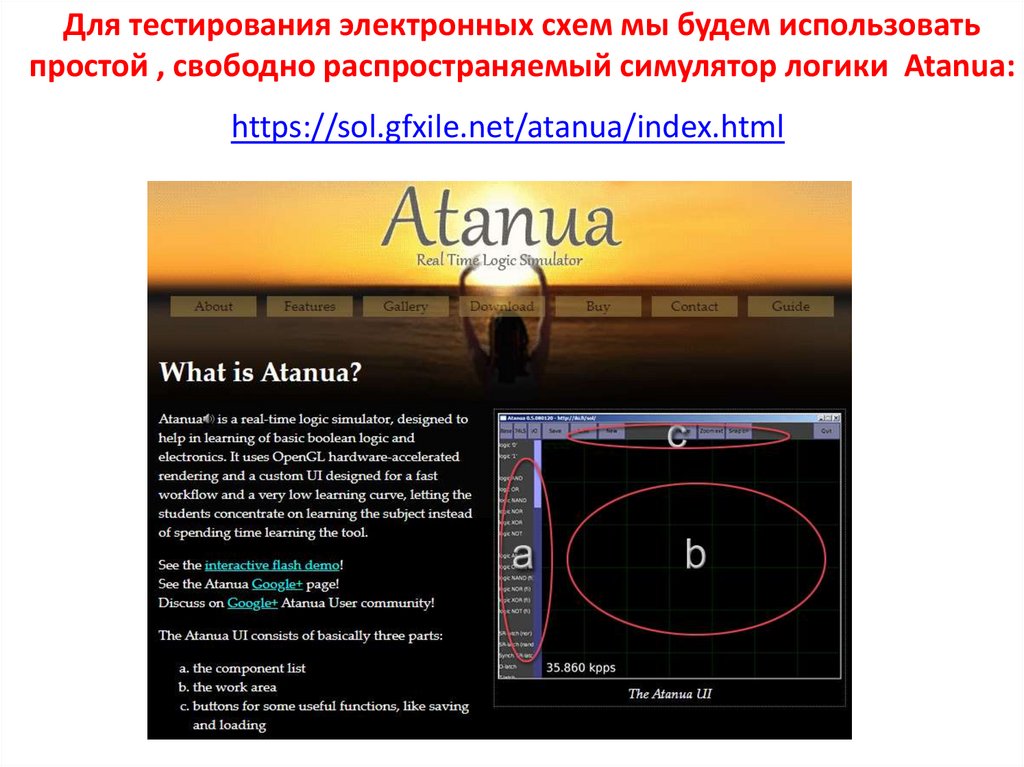

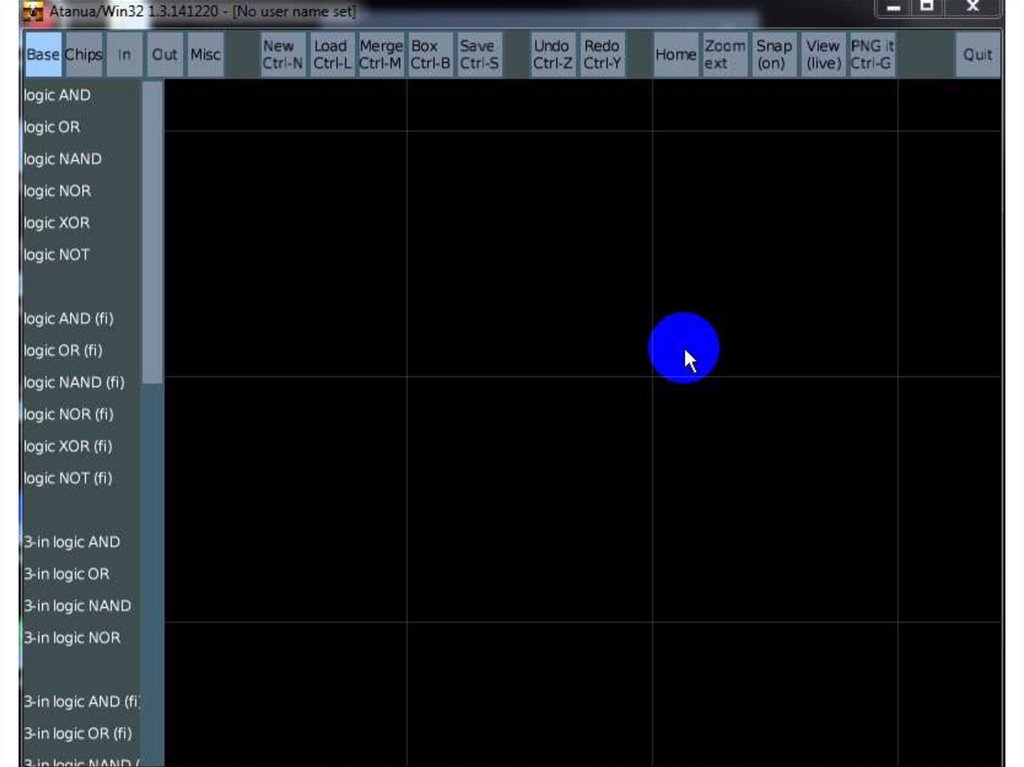

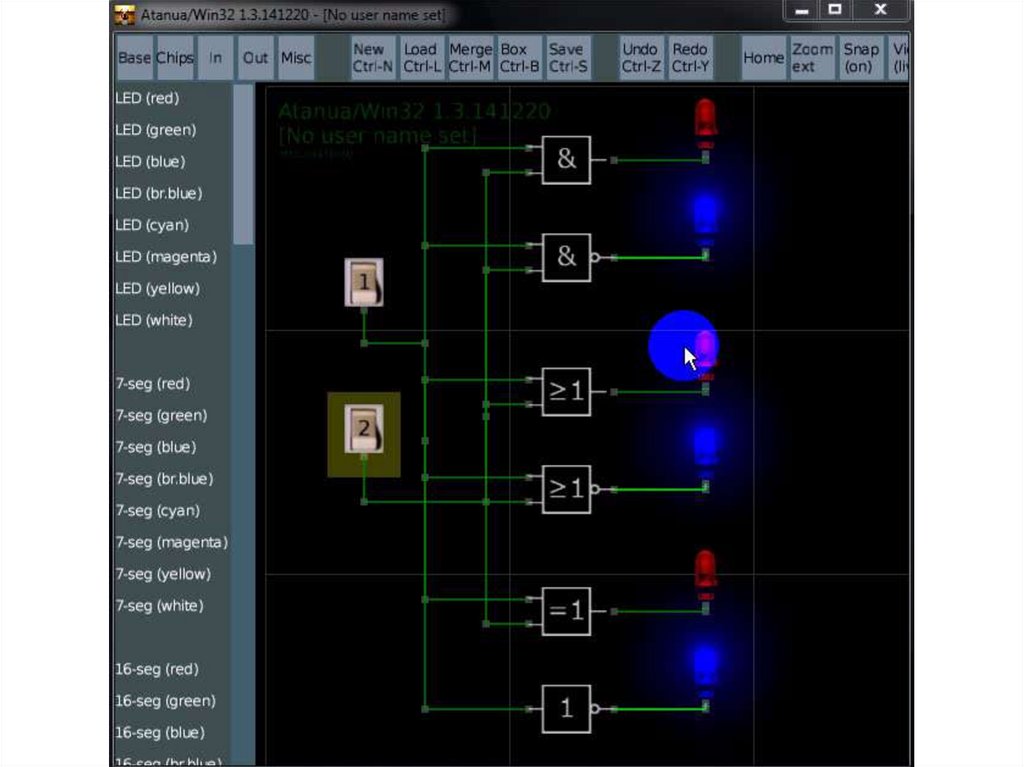

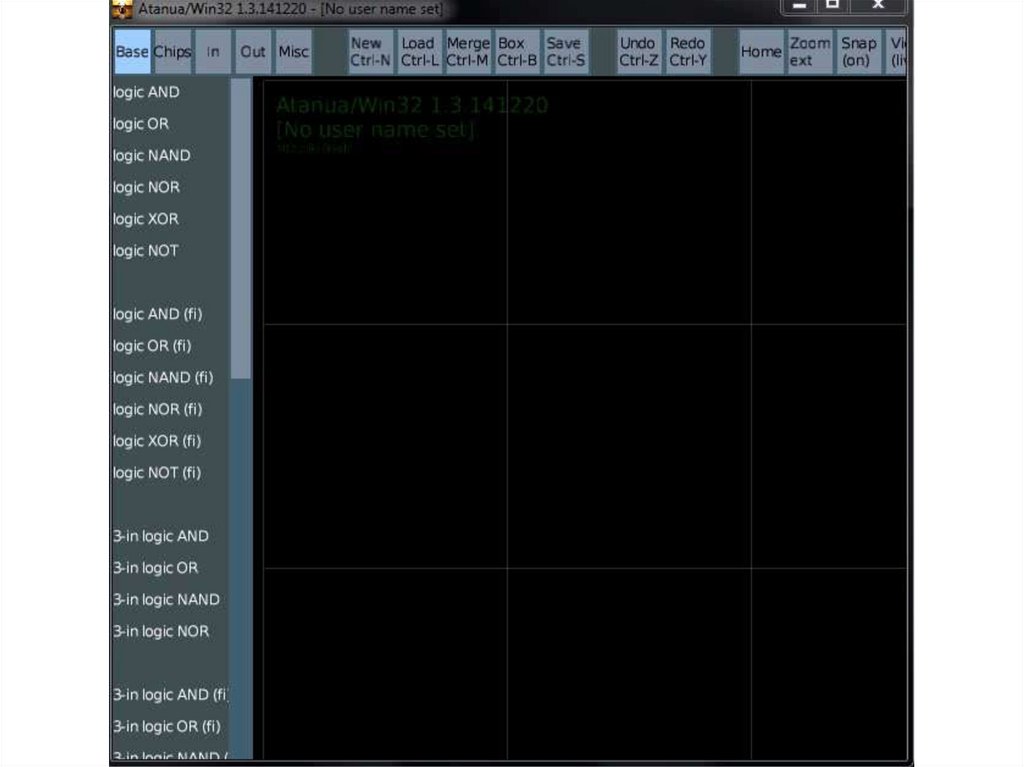

Для тестирования электронных схем мы будем использоватьпростой , свободно распространяемый симулятор логики Atanua:

https://sol.gfxile.net/atanua/index.html

9.

10.

11.

12.

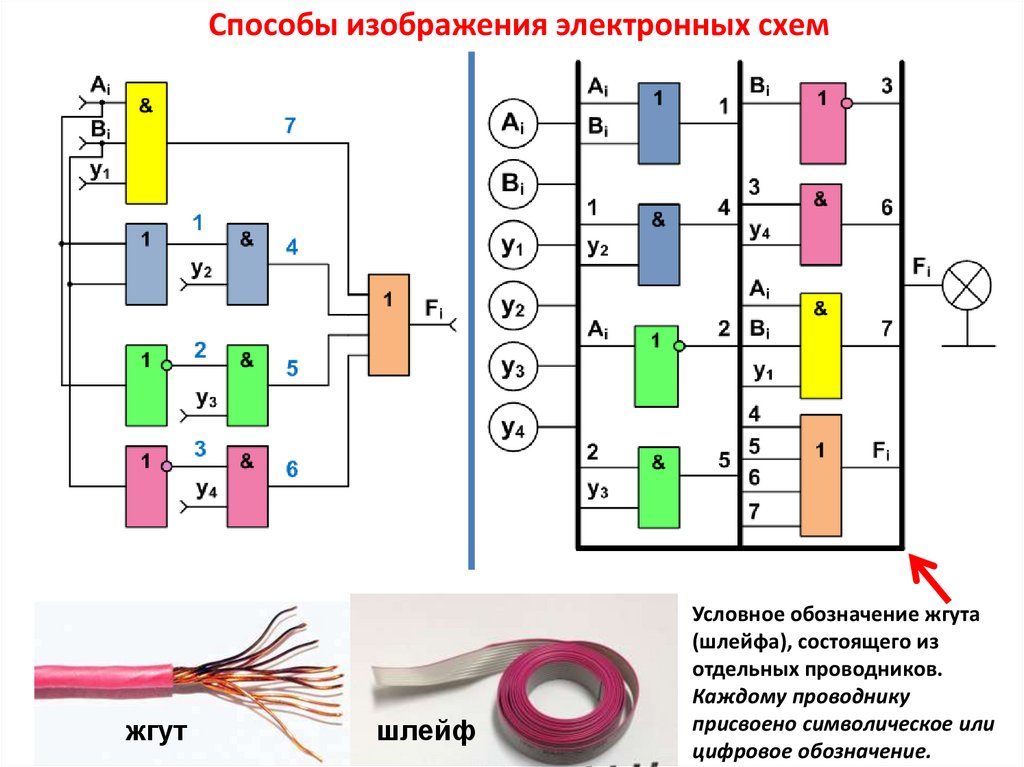

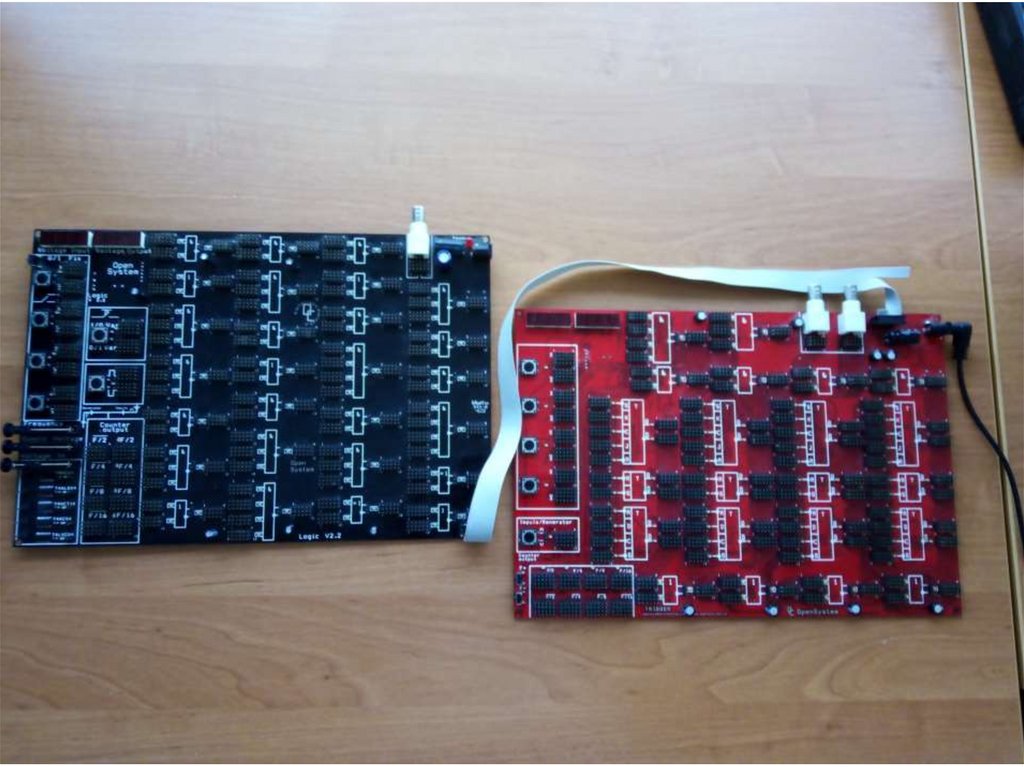

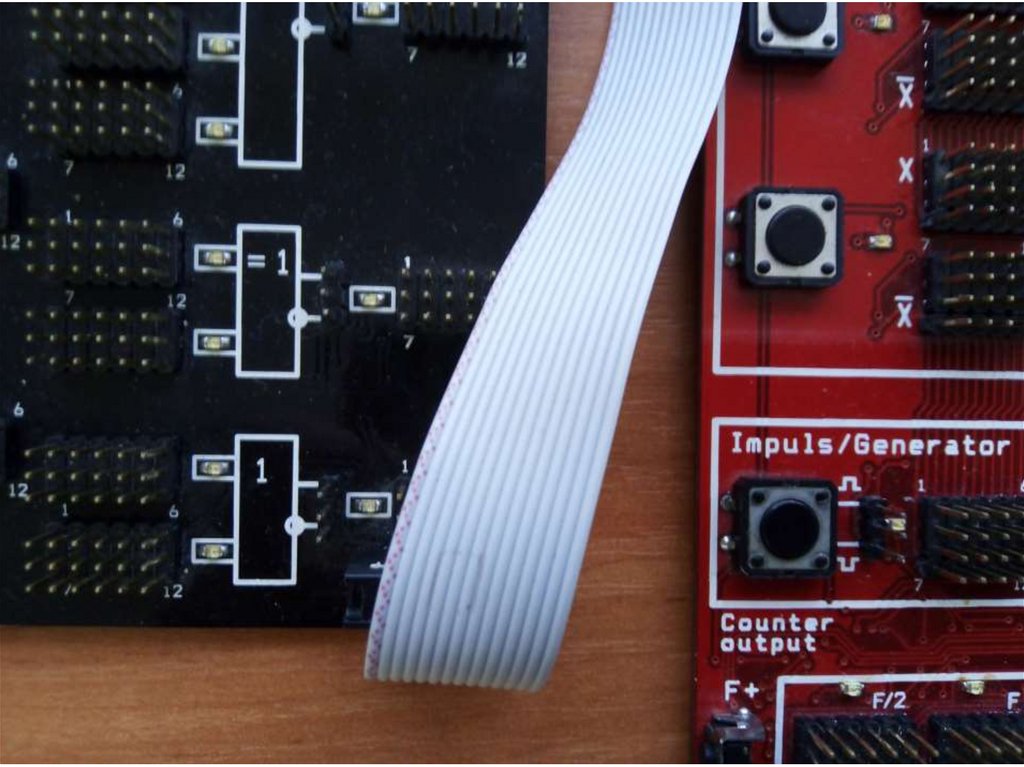

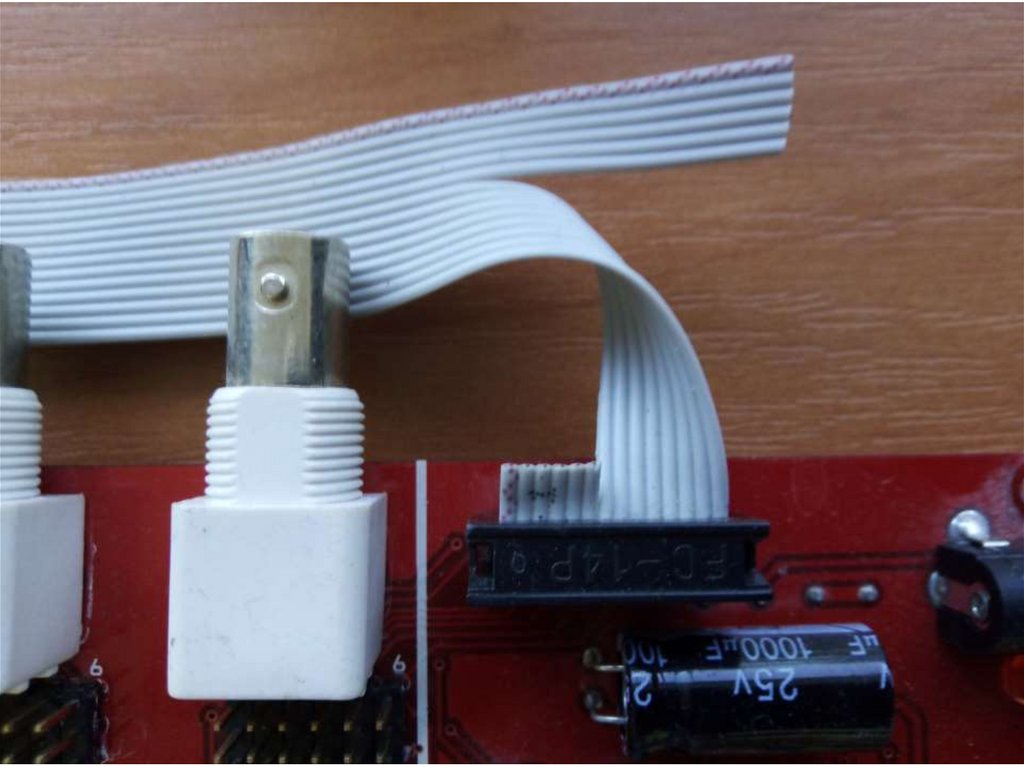

Способы изображения электронных схемжгут

шлейф

Условное обозначение жгута

(шлейфа), состоящего из

отдельных проводников.

Каждому проводнику

присвоено символическое или

цифровое обозначение.

13.

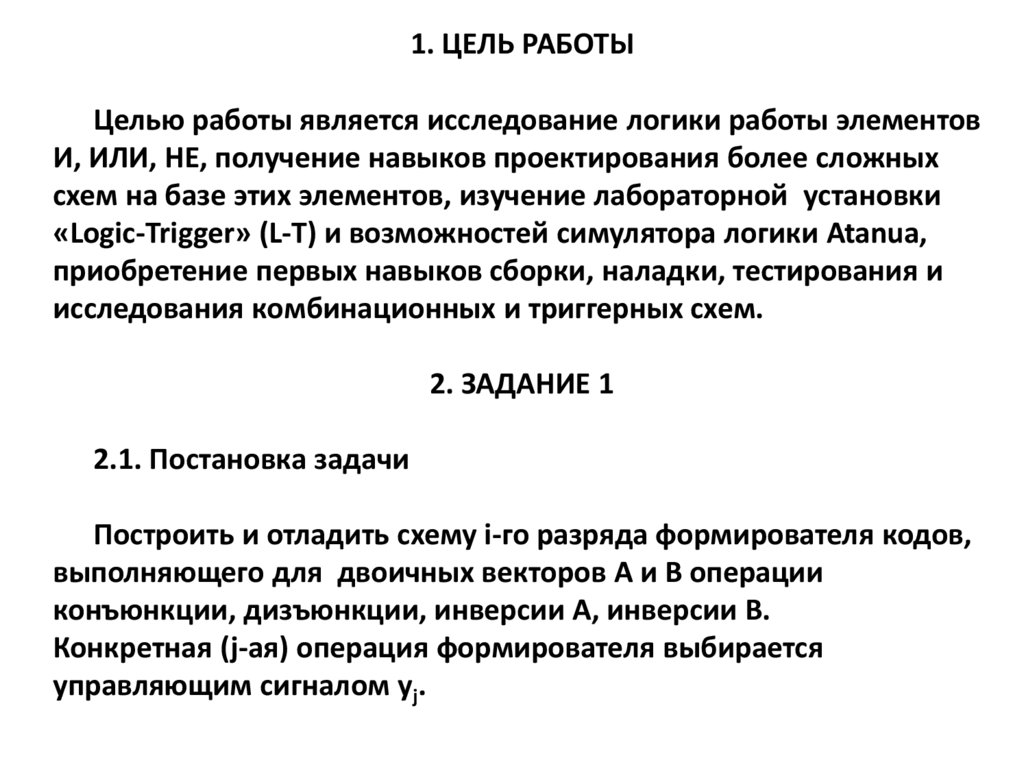

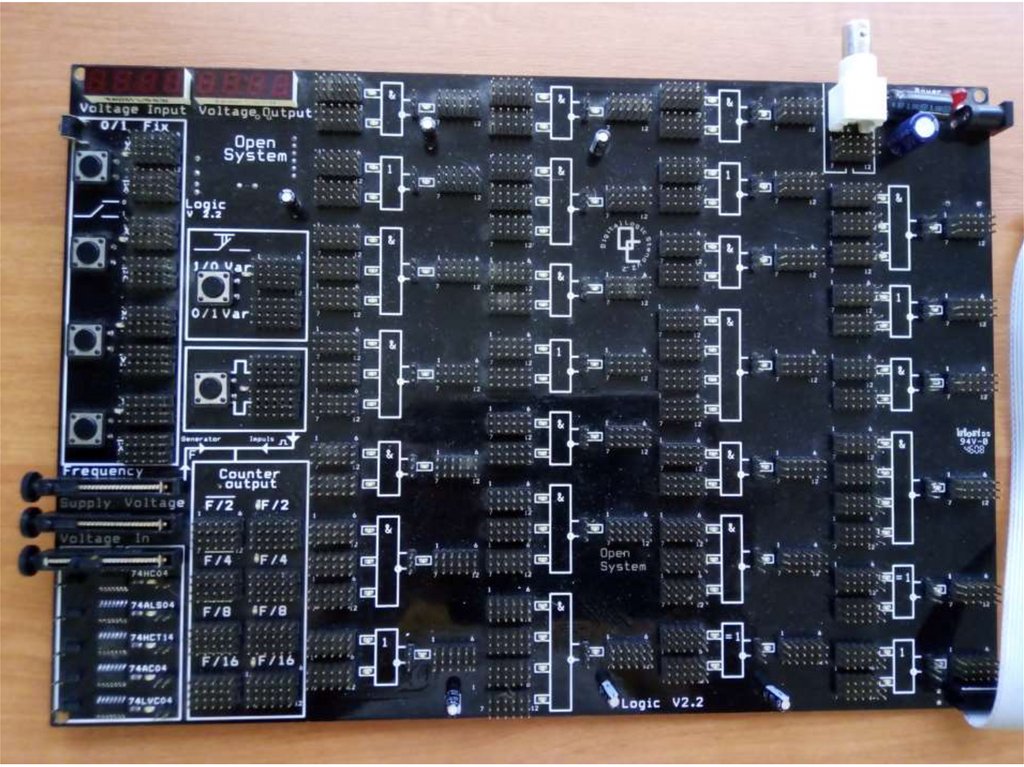

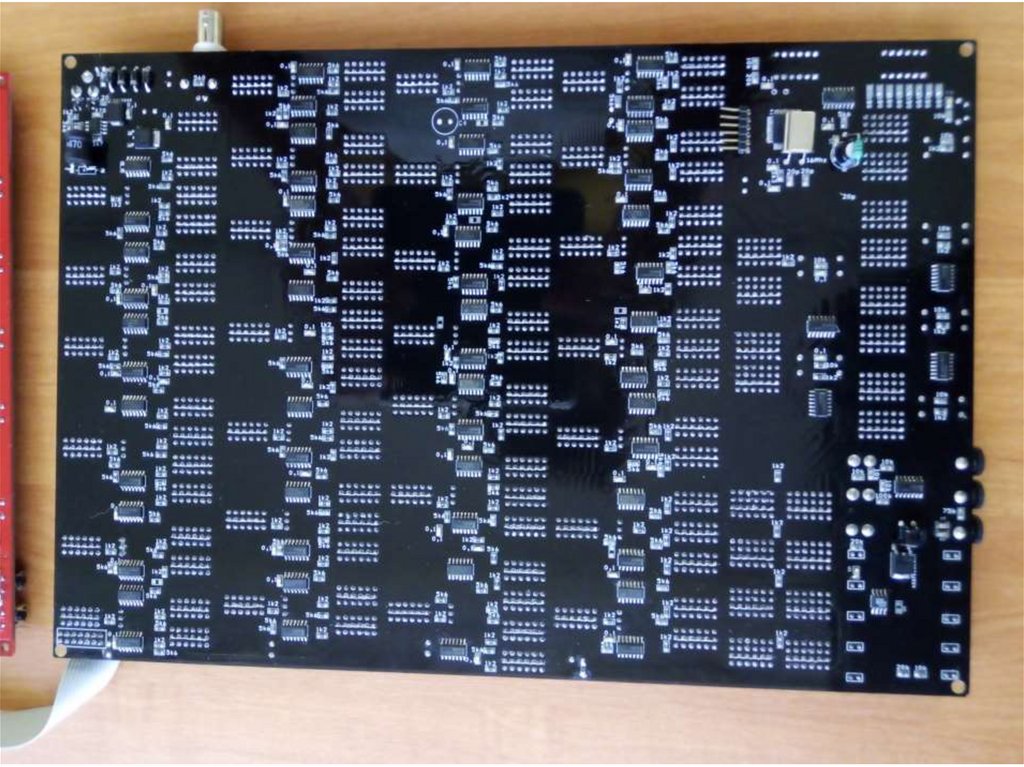

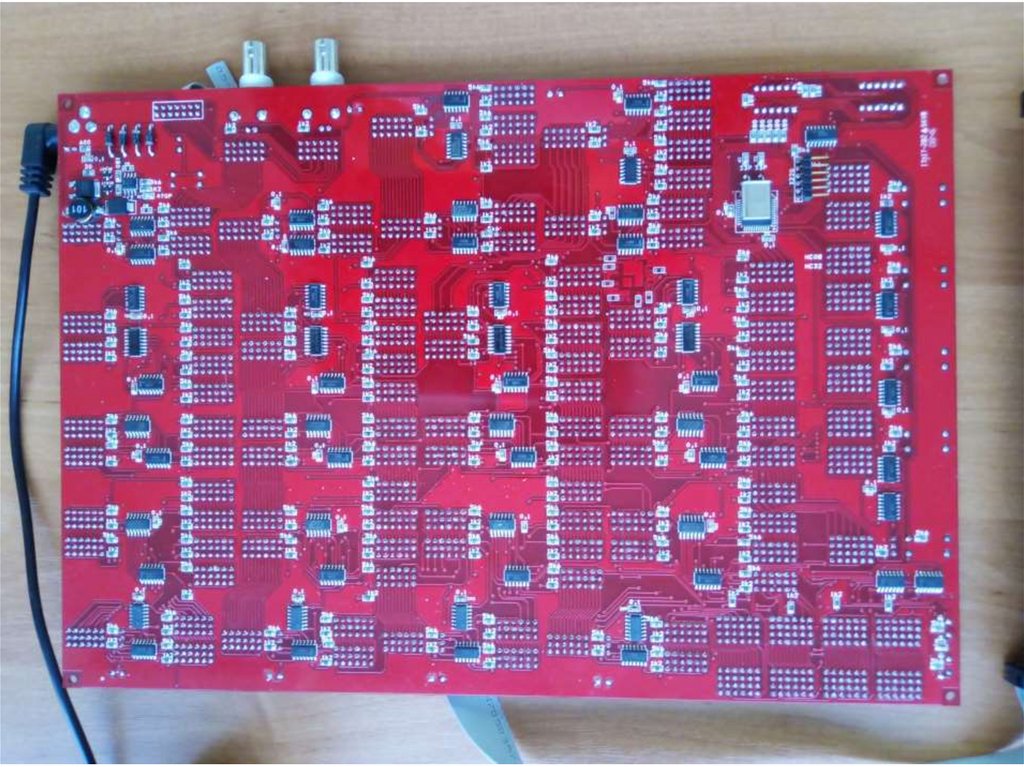

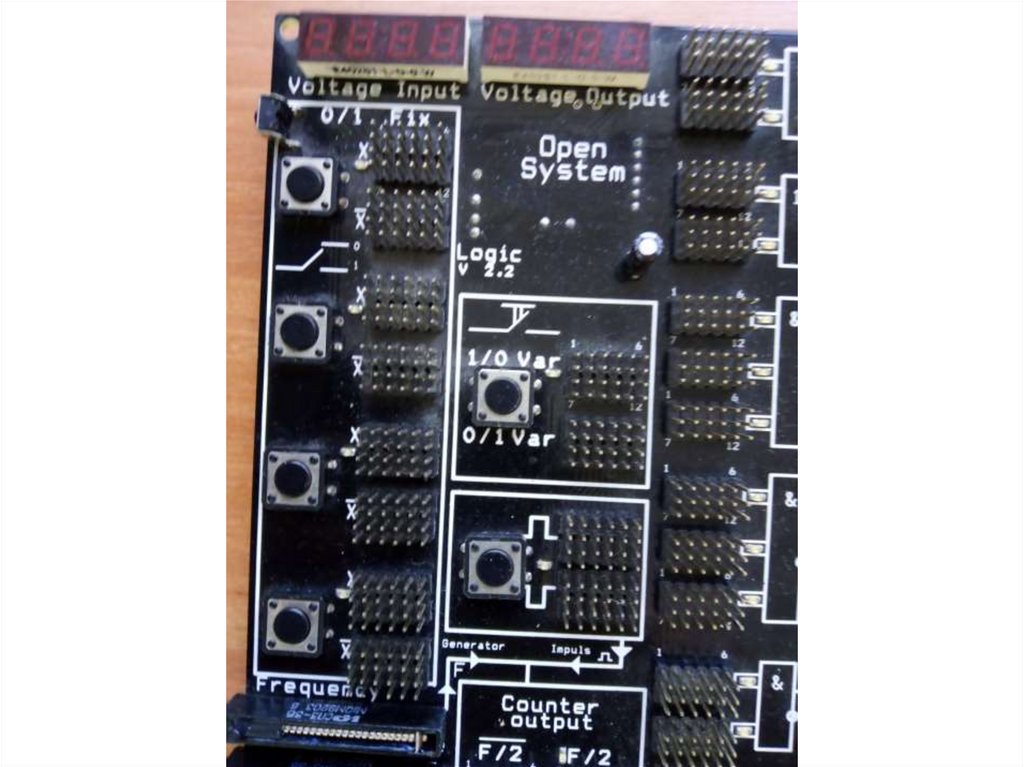

1. ЦЕЛЬ РАБОТЫЦелью работы является исследование логики работы элементов

И, ИЛИ, НЕ, получение навыков проектирования более сложных

схем на базе этих элементов, изучение лабораторной установки

«Logic-Trigger» (L-T) и возможностей симулятора логики Atanua,

приобретение первых навыков сборки, наладки, тестирования и

исследования комбинационных и триггерных схем.

2. ЗАДАНИЕ 1

2.1. Постановка задачи

Построить и отладить схему i-го разряда формирователя кодов,

выполняющего для двоичных векторов А и В операции

конъюнкции, дизъюнкции, инверсии А, инверсии В.

Конкретная (j-ая) операция формирователя выбирается

управляющим сигналом yj.

14.

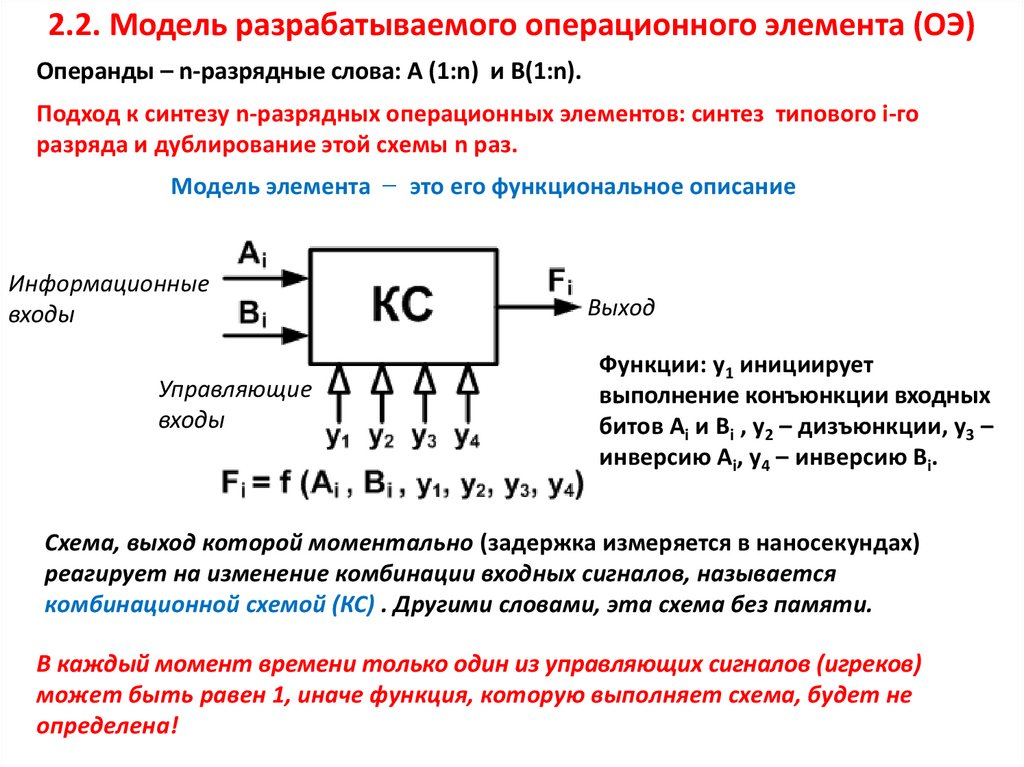

2.2. Модель разрабатываемого операционного элемента (ОЭ)Операнды – n-разрядные слова: А (1:n) и B(1:n).

Подход к синтезу n-разрядных операционных элементов: синтез типового i-го

разряда и дублирование этой схемы n раз.

Модель элемента − это его функциональное описание

Информационные

входы

Управляющие

входы

Выход

Функции: y1 инициирует

выполнение конъюнкции входных

битов Ai и Bi , y2 – дизъюнкции, y3 –

инверсию Ai, y4 – инверсию Bi.

Схема, выход которой моментально (задержка измеряется в наносекундах)

реагирует на изменение комбинации входных сигналов, называется

комбинационной схемой (КС) . Другими словами, эта схема без памяти.

В каждый момент времени только один из управляющих сигналов (игреков)

может быть равен 1, иначе функция, которую выполняет схема, будет не

определена!

15.

2.3. Разработка тестов дляпроверки работоспособности схемы

Тест – набор входных данных и

соответствующий ему набор выходных

данных.

Совокупность тестов для проверки

правильности работы схемы должна быть

полной (проверять все возможные

ситуации), но не избыточной.

Всего для 6 входных сигналов существует

26 = 64 тестовых комбинации.

Однако, для полной проверки приведенной

выше схемы нужно выполнить всего 16

тестов. Будут использоваться те

комбинации, в которых только один из

игреков равен 1. Остальные комбинации

входных сигналов запрещены.

16.

2.4. Разработка и макетирование принципиальной схемы ОЭAi

&

Bi

y1

Ai

1

Bi

&

y2

1

Ai

1

&

y3

Bi

1

&

y4

Fi

17.

18.

19.

20.

21.

22.

23.

24.

25.

26.

27.

28.

29.

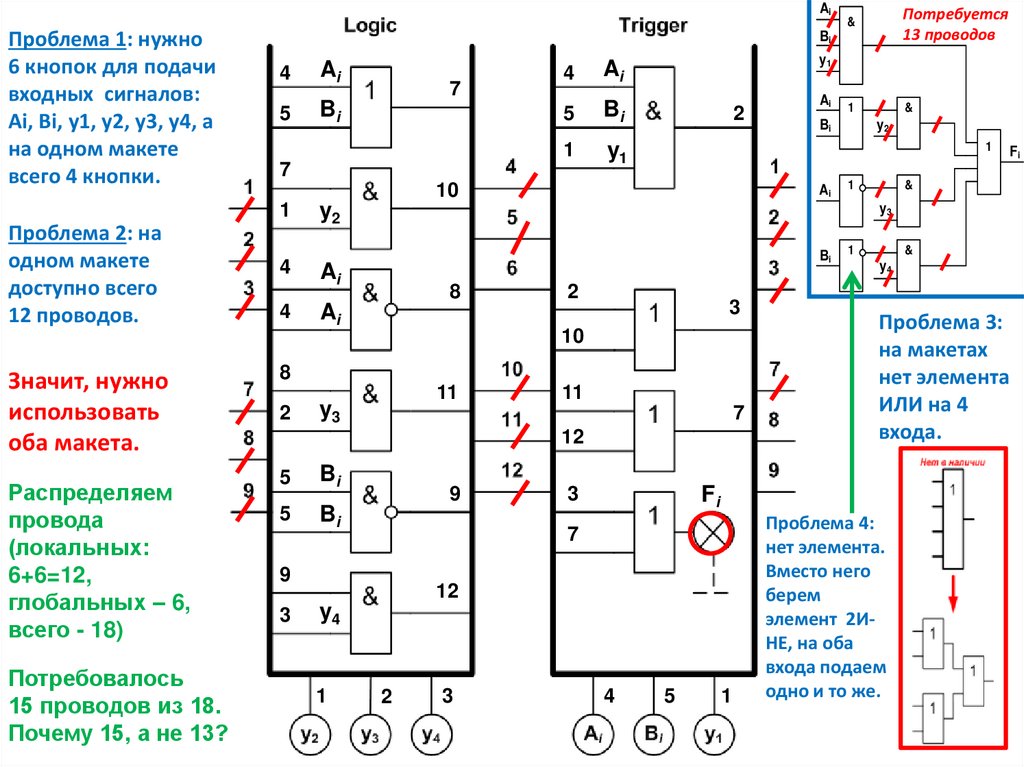

AiПроблема 1: нужно

6 кнопок для подачи

входных сигналов:

Ai, Bi, y1, y2, y3, y4, а

на одном макете

всего 4 кнопки.

4

Ai

5

Bi

7

4

Ai

5

Bi

1

y1

7

1

&

y1

2

4

4

y2

1

y2

Bi

8

2

3

Ai

Распределяем

провода

(локальных:

6+6=12,

глобальных – 6,

всего - 18)

5

Bi

5

Bi

11

y3

11

7

12

9

&

12

y4

2

3

1

&

y4

Проблема 3:

на макетах

нет элемента

ИЛИ на 4

входа.

Fi

3

7

9

1

Fi

y3

Ai

8

3

Bi

Ai

10

2

Ai

1

10

Значит, нужно

использовать

оба макета.

Потребовалось

15 проводов из 18.

Почему 15, а не 13?

Потребуется

13 проводов

Bi

1

Проблема 2: на

одном макете

доступно всего

12 проводов.

&

4

5

1

Проблема 4:

нет элемента.

Вместо него

берем

элемент 2ИНЕ, на оба

входа подаем

одно и то же.

30.

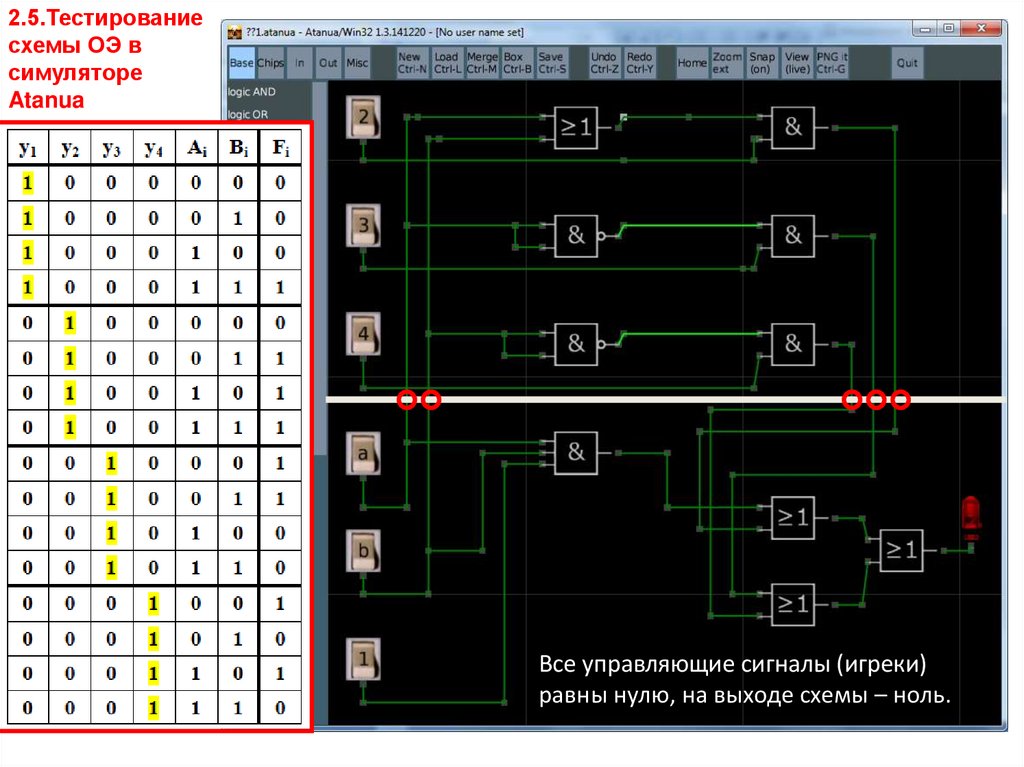

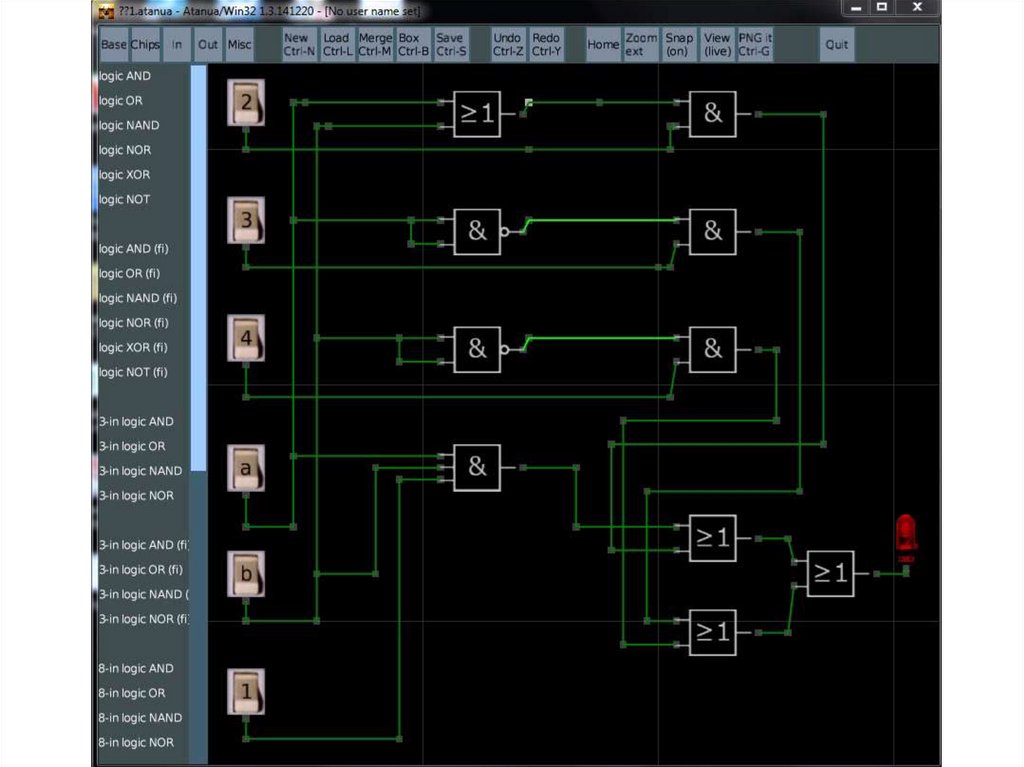

2.5.Тестированиесхемы ОЭ в

симуляторе

Atanua

Все управляющие сигналы (игреки)

равны нулю, на выходе схемы – ноль.

31.

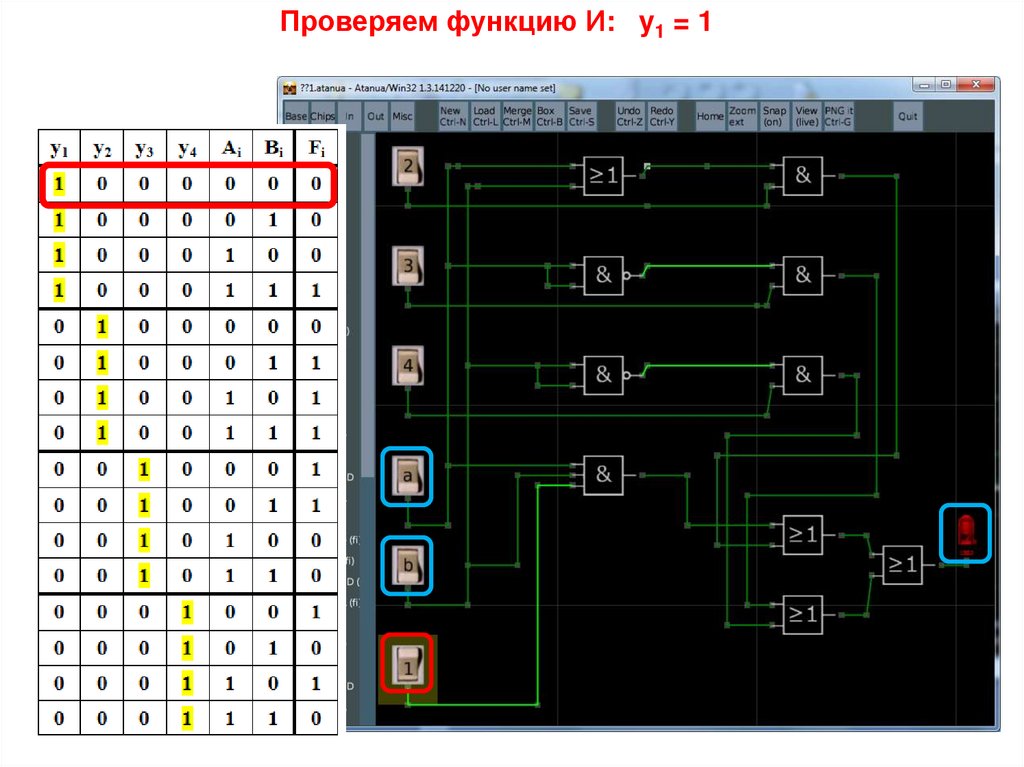

Проверяем функцию И: y1 = 132.

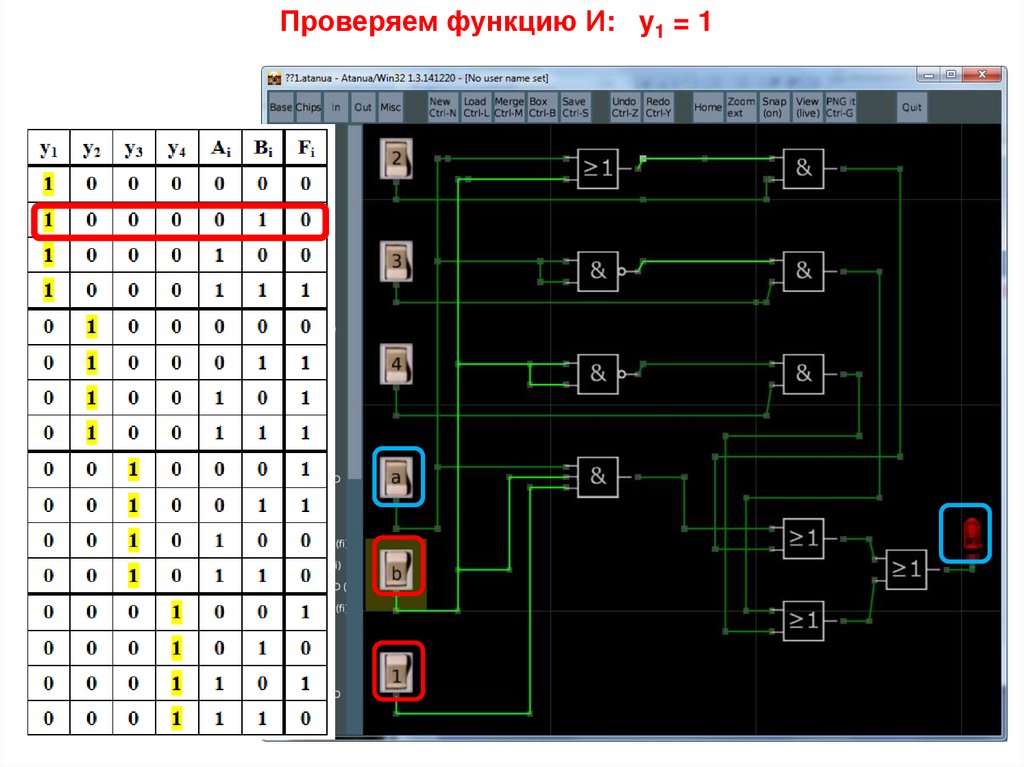

Проверяем функцию И: y1 = 133.

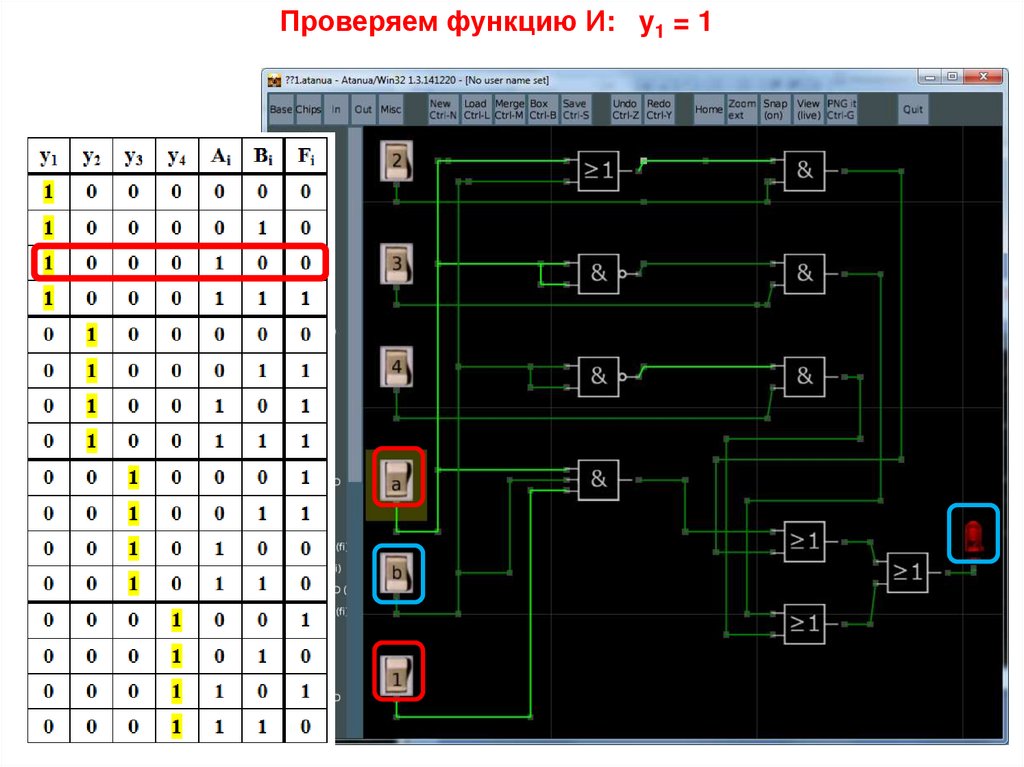

Проверяем функцию И: y1 = 134.

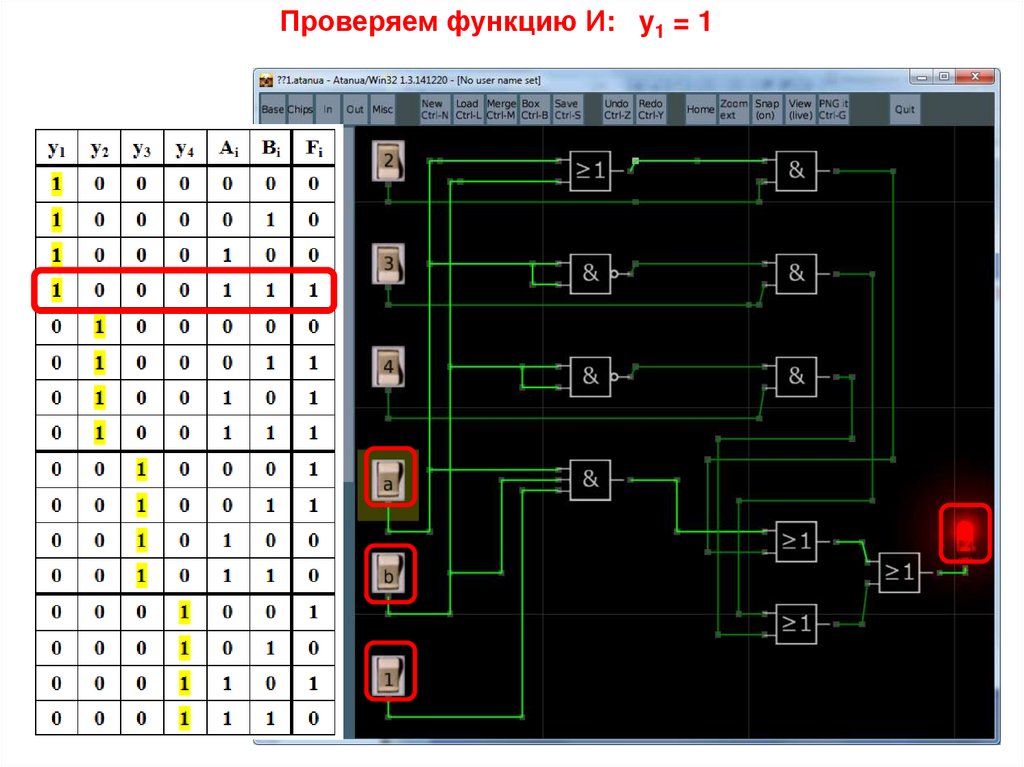

Проверяем функцию И: y1 = 135.

36.

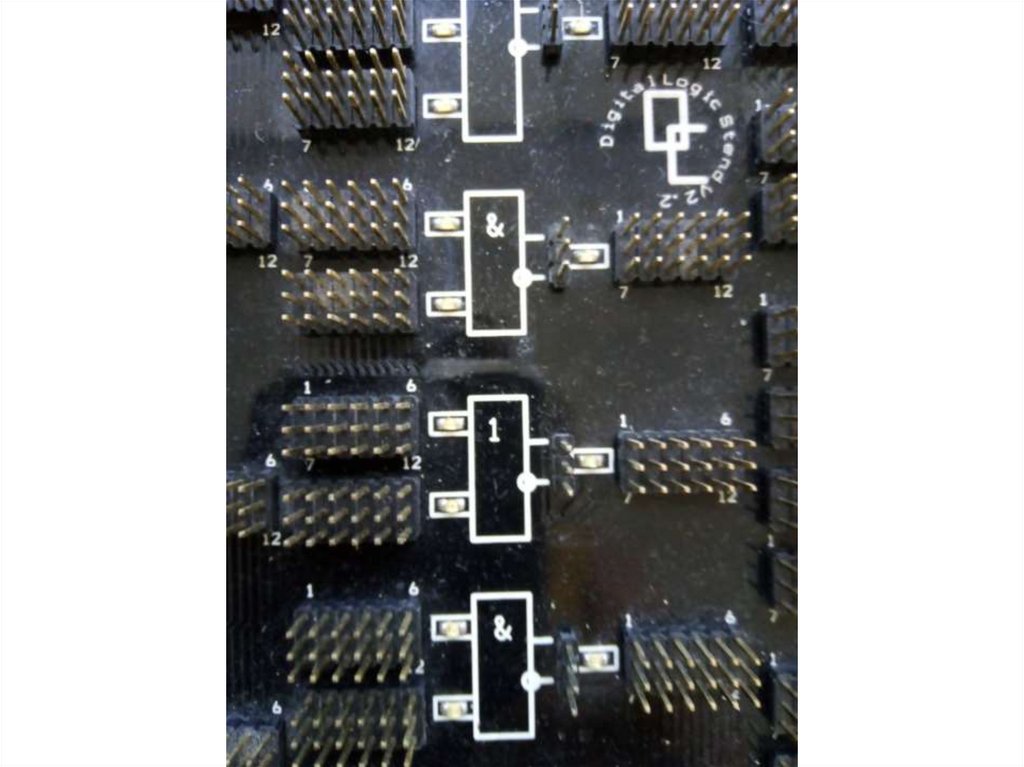

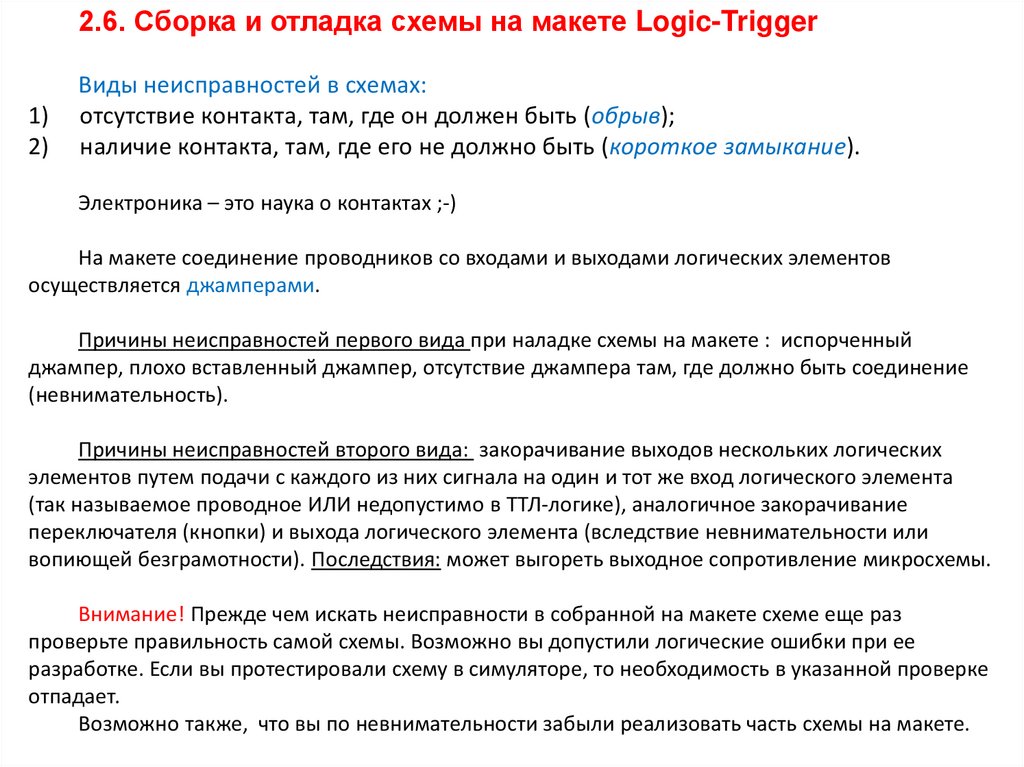

2.6. Сборка и отладка схемы на макете Logic-Trigger1)

2)

Виды неисправностей в схемах:

отсутствие контакта, там, где он должен быть (обрыв);

наличие контакта, там, где его не должно быть (короткое замыкание).

Электроника – это наука о контактах ;-)

На макете соединение проводников со входами и выходами логических элементов

осуществляется джамперами.

Причины неисправностей первого вида при наладке схемы на макете : испорченный

джампер, плохо вставленный джампер, отсутствие джампера там, где должно быть соединение

(невнимательность).

Причины неисправностей второго вида: закорачивание выходов нескольких логических

элементов путем подачи с каждого из них сигнала на один и тот же вход логического элемента

(так называемое проводное ИЛИ недопустимо в ТТЛ-логике), аналогичное закорачивание

переключателя (кнопки) и выхода логического элемента (вследствие невнимательности или

вопиющей безграмотности). Последствия: может выгореть выходное сопротивление микросхемы.

Внимание! Прежде чем искать неисправности в собранной на макете схеме еще раз

проверьте правильность самой схемы. Возможно вы допустили логические ошибки при ее

разработке. Если вы протестировали схему в симуляторе, то необходимость в указанной проверке

отпадает.

Возможно также, что вы по невнимательности забыли реализовать часть схемы на макете.

37.

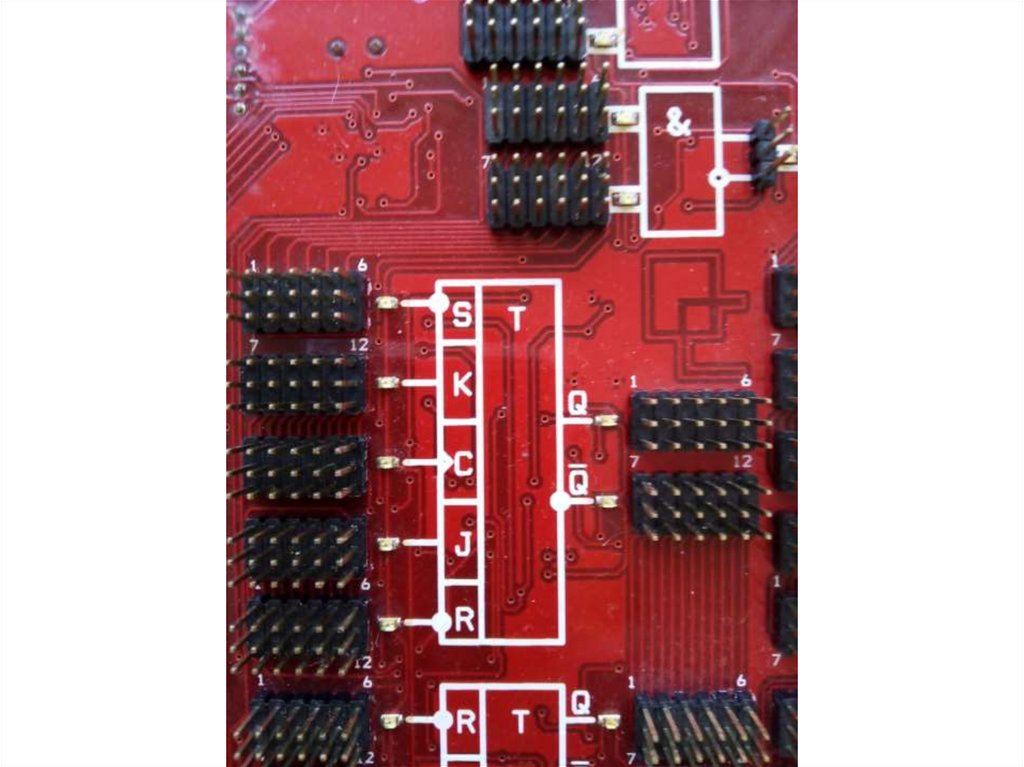

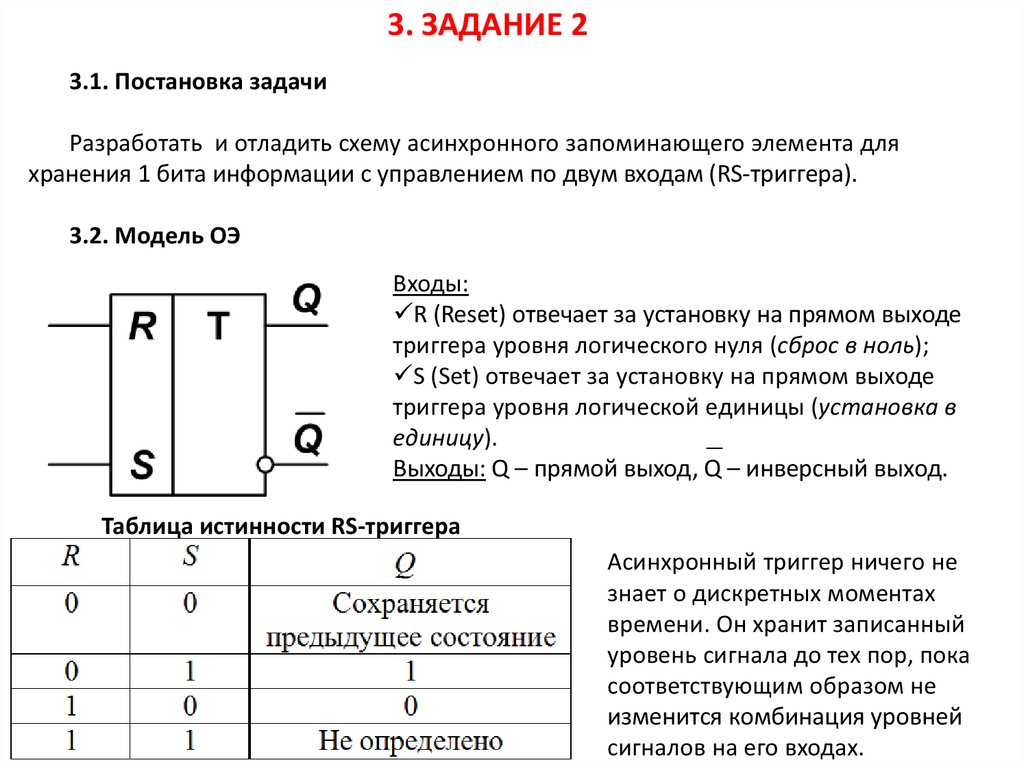

3. ЗАДАНИЕ 23.1. Постановка задачи

Разработать и отладить схему асинхронного запоминающего элемента для

хранения 1 бита информации с управлением по двум входам (RS-триггера).

3.2. Модель ОЭ

Входы:

R (Reset) отвечает за установку на прямом выходе

триггера уровня логического нуля (сброс в ноль);

S (Set) отвечает за установку на прямом выходе

триггера уровня логической единицы (установка в

единицу).

Выходы: Q – прямой выход, Q – инверсный выход.

Таблица истинности RS-триггера

Асинхронный триггер ничего не

знает о дискретных моментах

времени. Он хранит записанный

уровень сигнала до тех пор, пока

соответствующим образом не

изменится комбинация уровней

сигналов на его входах.

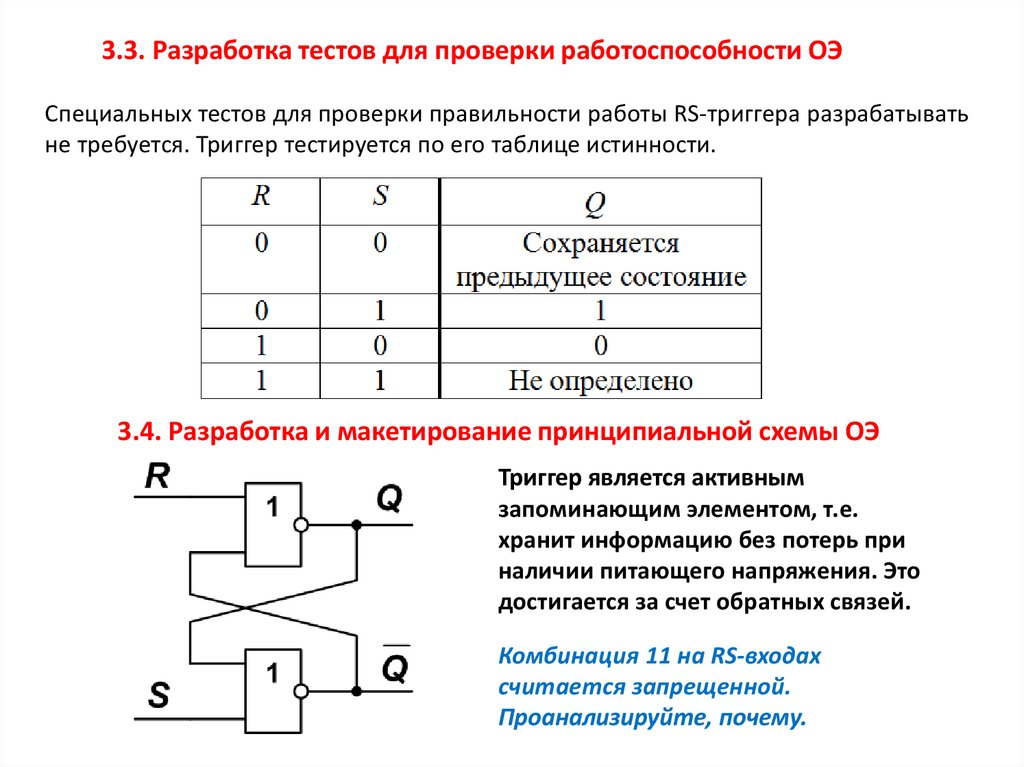

38.

3.3. Разработка тестов для проверки работоспособности ОЭСпециальных тестов для проверки правильности работы RS-триггера разрабатывать

не требуется. Триггер тестируется по его таблице истинности.

3.4. Разработка и макетирование принципиальной схемы ОЭ

Триггер является активным

запоминающим элементом, т.е.

хранит информацию без потерь при

наличии питающего напряжения. Это

достигается за счет обратных связей.

Комбинация 11 на RS-входах

считается запрещенной.

Проанализируйте, почему.

39.

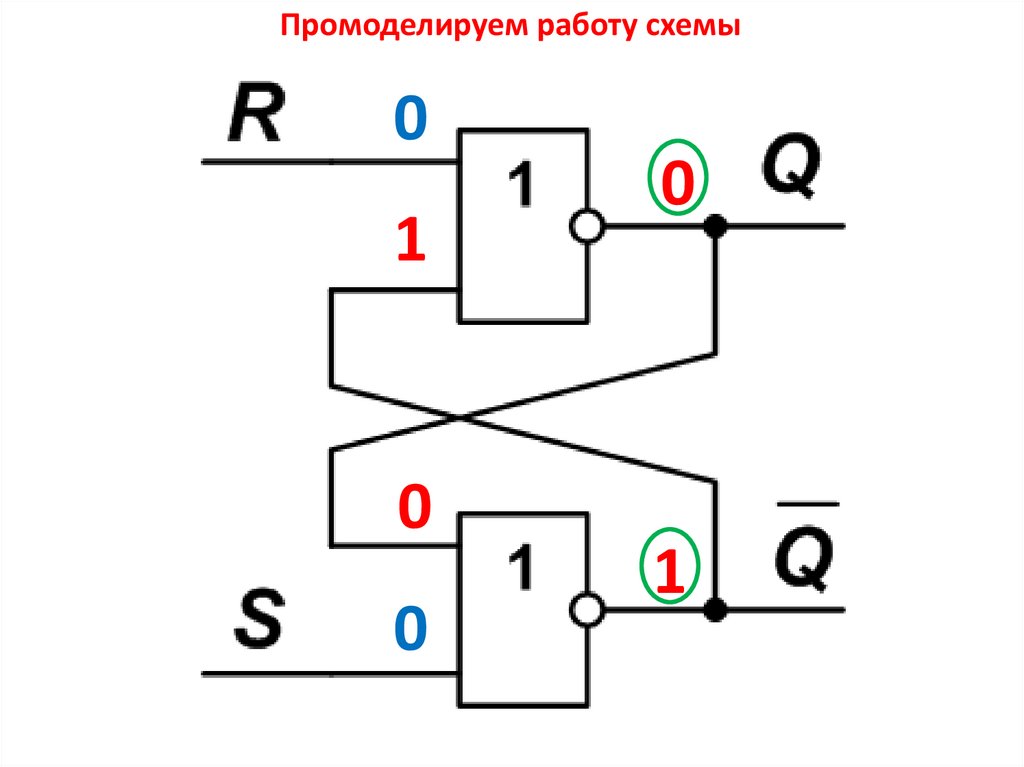

Промоделируем работу схемы0

1

0

0

0

1

40.

Промоделируем работу схемы0

0

1

0

1

0

41.

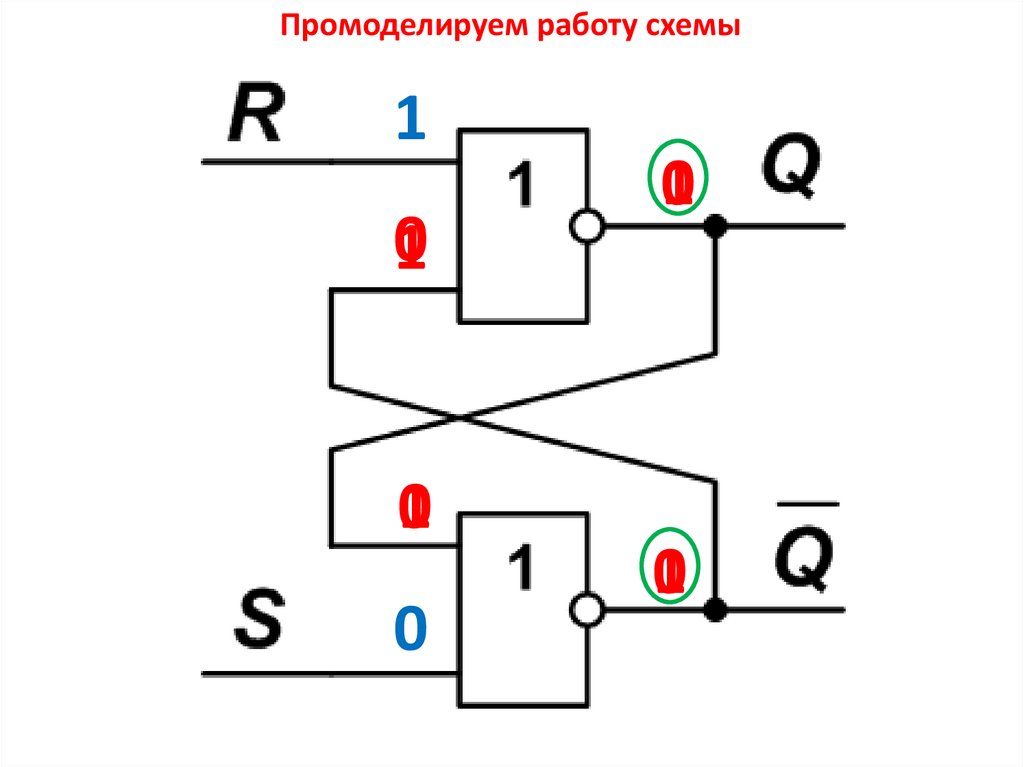

Промоделируем работу схемы1

0

1

0

1

0

1

0

0

1

42.

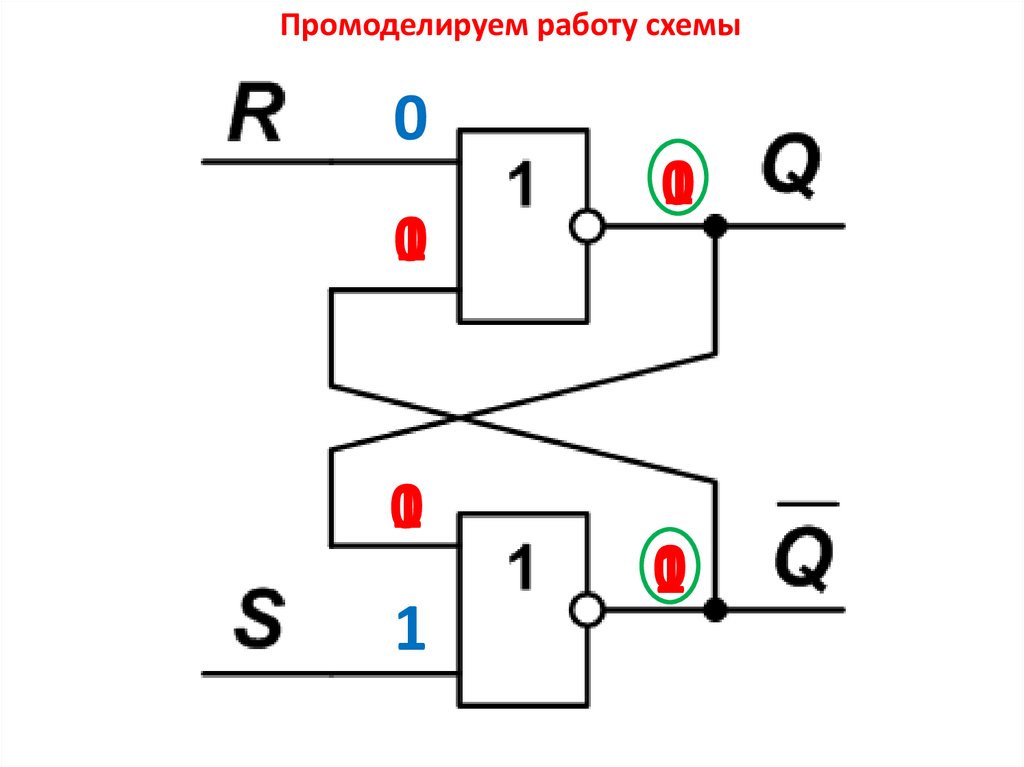

Промоделируем работу схемы0

0

1

0

1

1

0

1

0

1

43.

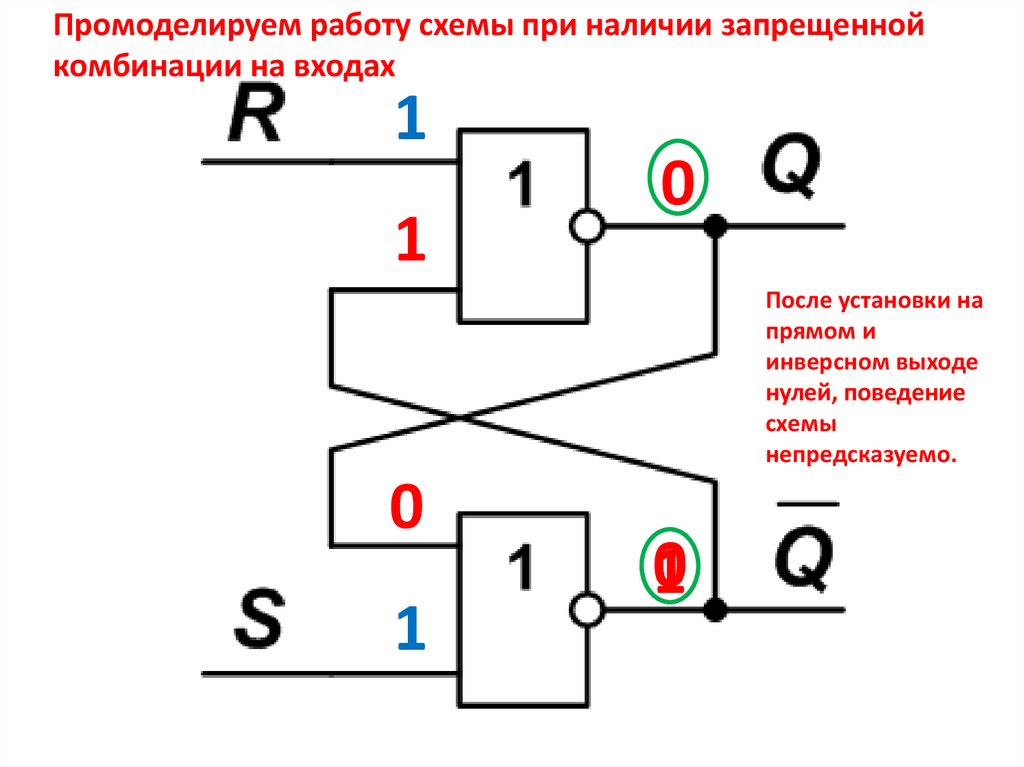

Промоделируем работу схемы при наличии запрещеннойкомбинации на входах

1

1

0

После установки на

прямом и

инверсном выходе

нулей, поведение

схемы

непредсказуемо.

1

0

0

1

44.

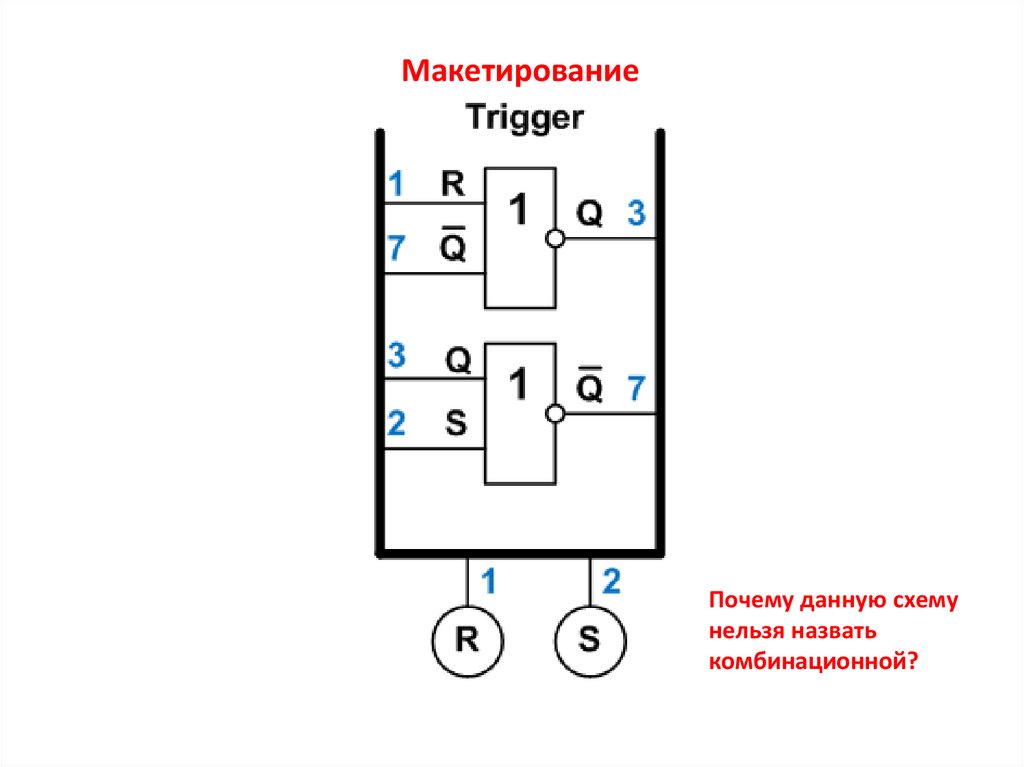

МакетированиеПочему данную схему

нельзя назвать

комбинационной?

45.

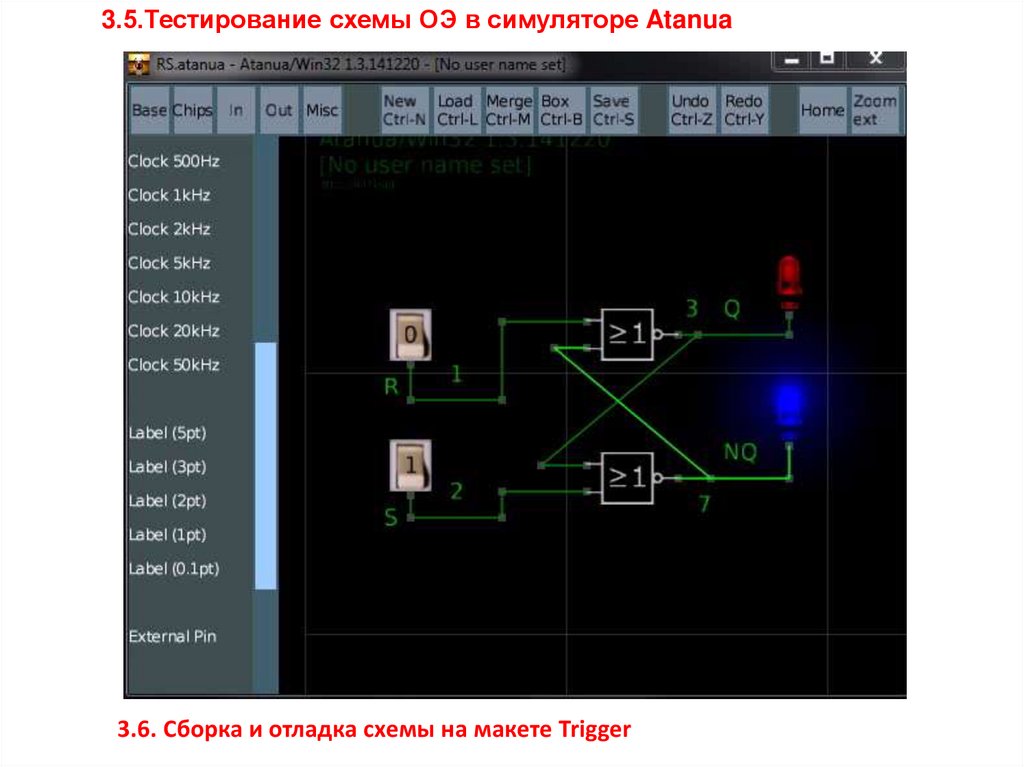

3.5.Тестирование схемы ОЭ в симуляторе Atanua3.6. Сборка и отладка схемы на макете Trigger

46.

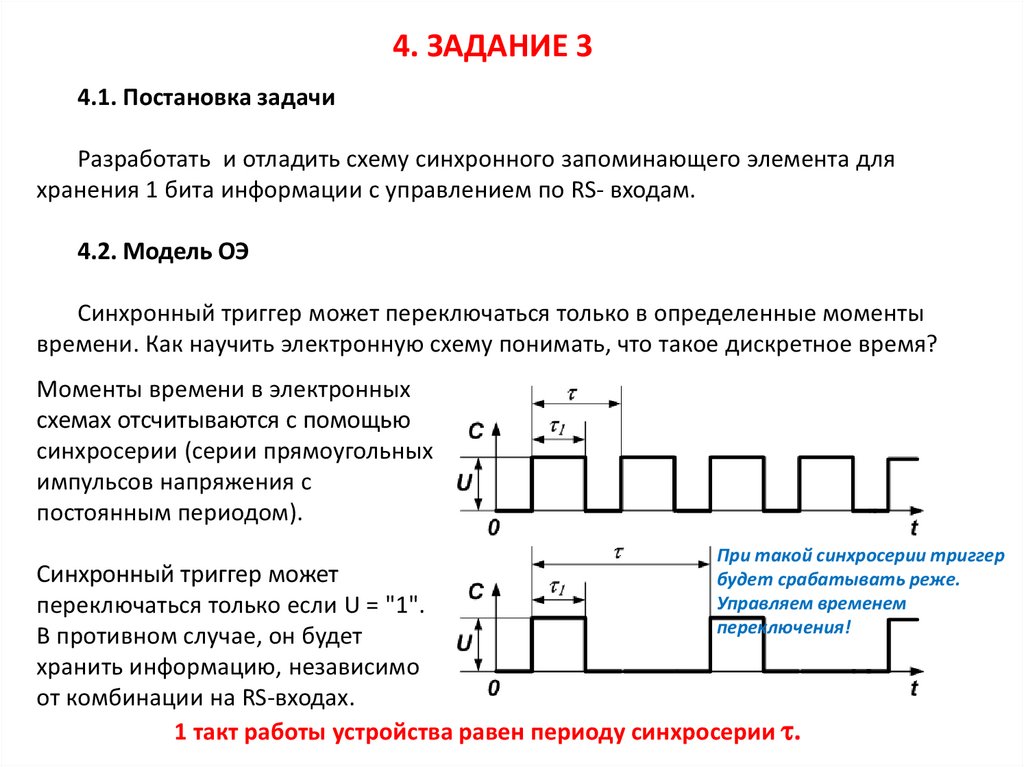

4. ЗАДАНИЕ 34.1. Постановка задачи

Разработать и отладить схему синхронного запоминающего элемента для

хранения 1 бита информации с управлением по RS- входам.

4.2. Модель ОЭ

Синхронный триггер может переключаться только в определенные моменты

времени. Как научить электронную схему понимать, что такое дискретное время?

Моменты времени в электронных

схемах отсчитываются с помощью

синхросерии (серии прямоугольных

импульсов напряжения с

постоянным периодом).

При такой синхросерии триггер

будет срабатывать реже.

Управляем временем

переключения!

Синхронный триггер может

переключаться только если U = "1".

В противном случае, он будет

хранить информацию, независимо

от комбинации на RS-входах.

1 такт работы устройства равен периоду синхросерии .

47.

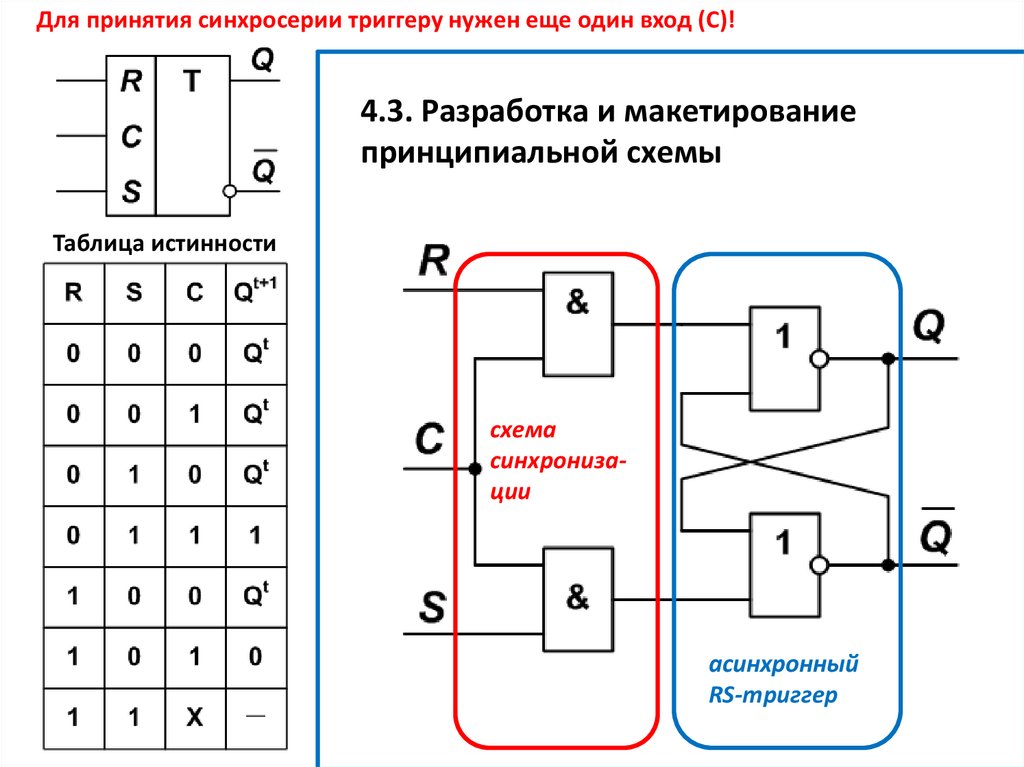

Для принятия синхросерии триггеру нужен еще один вход (С)!4.3. Разработка и макетирование

принципиальной схемы

Таблица истинности

схема

синхронизации

асинхронный

RS-триггер

48.

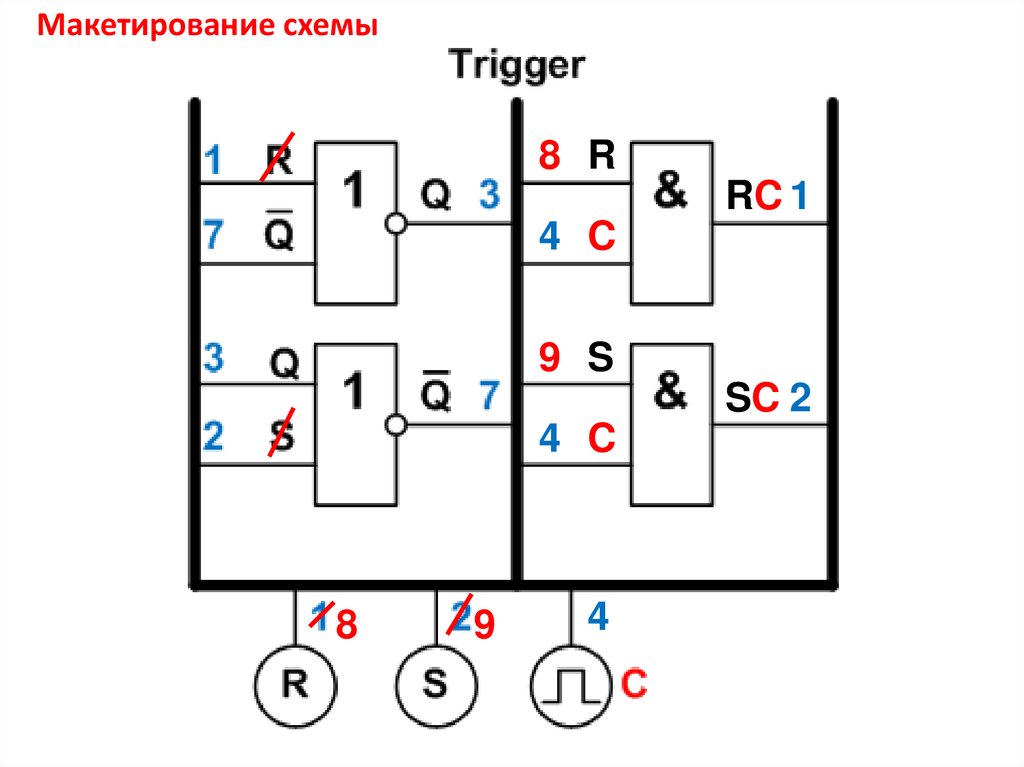

Макетирование схемы8 R

RC 1

4 C

9 S

SC 2

4 C

8

9

4

49.

4.5.1. Тестирование схемы ОЭ в симуляторе Atanua в пошаговом режиме50.

4.5.2. Тестирование схемы ОЭ в симуляторе Atanua вдинамическом режиме

Период

синхросерии

называют тактом

4.6. Сборка и отладка схемы на макете Trigger

51.

ВЫВОДВывод по лабораторной работе должен

констатировать, что достигнуты все цели

работы (перечисляются), и выполнены все

поставленные задачи (перечисляются).

Если при отладке схемы в симуляторе или

на макете возникли ошибки, нужно

описать их причину и способ устранения,

который был применен.

informatics

informatics